# Research Article

# On the Use of an Algebraic Signature Analyzer for Mixed-Signal Systems Testing

#### Vadim Geurkov and Lev Kirischian

Department of Electrical and Computer Engineering, Ryerson University, 350 Victoria Street, Toronto, ON, Canada M5B 2K3

Correspondence should be addressed to Vadim Geurkov; vgeurkov@ee.ryerson.ca

Received 31 May 2014; Revised 17 October 2014; Accepted 21 October 2014; Published 16 November 2014

Academic Editor: M. Renovell

Copyright © 2014 V. Geurkov and L. Kirischian. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

We propose an approach to design of an algebraic signature analyzer that can be used for mixed-signal systems testing. The analyzer does not contain carry propagating circuitry, which improves its performance as well as fault tolerance. The common design technique of a signature analyzer for mixed-signal systems is based on the rules of an arithmetic finite field. The application of this technique to the systems with an arbitrary radix is a challenging task and the devices designed possess high hardware complexity. The proposed technique is simple and applicable to systems of any size and radix. The hardware complexity is low. The technique can also be used in arithmetic/algebraic coding and cryptography.

## **1. Introduction**

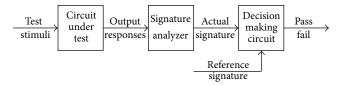

Signature analysis has been widely used for digital and mixedsignal systems testing [1-12]. Mixed-signal systems consist of both digital and analog circuits; however the signature analysis method is only applicable to the subset of these systems that have digital outputs (such as analog-to-digital converters, measurement instruments, etc.). Signature analysis can be employed as an external test solution or can be embedded into the system under test. In the built-in implementation, a circuit under test (CUT) of digital or mixed-signal nature is fed by test stimuli, while the output responses are compacted by a signature analyzer (SA), as illustrated in Figure 1. The actual signature is compared against the fault-free circuit's signature and a pass/fail decision is made. A signature of a fault-free circuit is referred to as a reference signature. If the CUT is of a digital nature, the SA essentially constitutes a circuit that computes an *algebraic remainder*. The reference signature has only one, punctual value, and the decision making circuit consists of a simple digital comparator. If the CUT is of a mixed-signal nature, the SA computes an arithmetic residue. In this case, the reference signature becomes an *interval* value and the decision making circuit uses a window comparator.

Design methods for an algebraic signature analyzer have been well developed in error-control coding [13]. A remainder calculating circuit for an arbitrary base (binary or nonbinary) can be readily designed for a digital CUT of any size. In contrast, it is much harder to design a residue calculating circuit, specifically for a nonbinary base [14]. Furthermore, due to the presence of carry propagating circuitry, the implementation complexity and error vulnerability of the residue calculating circuit.

We propose an approach to design of an algebraic signature analyzer that can be used for mixed-signal systems testing. Due to an algebraic nature, the analyzer does not contain carry propagating circuitry. This helps to improve its error immunity, as well as performance.

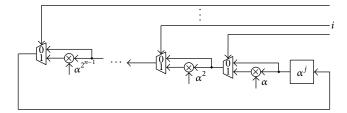

## 2. A Conventional Signature Analyzer

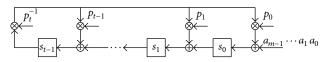

An algebraic signature analyzer is designed on the basis of a polynomial division circuit, as shown in Figure 2 [3, 13, 15]. This circuit divides the incoming sequence of nonbinary symbols (digits),  $a_{m-1}, \ldots, a_1, a_0$ , treated as a polynomial:

$$a(y) = a_{m-1}y^{m-1} + \dots + a_1y + a_0 \tag{1}$$

FIGURE 1: Built-in signature analysis of a circuit under test.

FIGURE 2: A *t*-stage polynomial division circuit.

by the polynomial

$$p(y) = p_t y^t + \dots + p_1 y + p_0, \quad t \ll m.$$

(2)

The remainder

$$s(y) = s_{t-1}y^{t-1} + \dots + s_1y + s_0$$

(3)

constitutes a CUT signature.

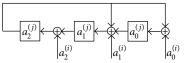

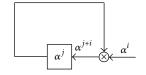

Each digit,  $a_i$ ,  $0 \le i \le m - 1$ , consists *n* bits and is considered to be an element of the field  $GF(2^n)$ . The degree of the polynomial (2), or the number of stages, *t*, in Figure 2, depends on the desired probability of undetected error in the sequence of incoming digits. For long sequences with independent errors, this probability is estimated as  $P_{nd} \approx 2^{-tn}$ . In practice,  $n \ge 8$  and even for the one-stage circuit,  $P_{nd} \le 2^{-(1\times 8)} = 0.0039$ , which is quite low. Therefore, a multiple-input signature analyzer normally contains only one stage. Such an analyzer is presented in Figure 3 [14], where  $\alpha$ is a primitive element of the field  $GF(2^n)$ , that is, a root of a primitive polynomial  $g(x) = g_{n-1}x^{n-1} + \cdots + g_1x + g_0$ . Each element of the field can be represented by a power of  $\alpha$ . Let  $\alpha^i$  be the incoming digit and  $\alpha^j$  the content of the analyzer. Then, each operational cycle of the analyzer is described by the expression

$$\alpha^{j}\alpha \oplus \alpha^{i} = \alpha^{k}.$$

(4)

Without a loss of generality, we will consider a 3-bit signature register (n = 3), with  $\alpha$  being a primitive element of  $GF(2^3)$ , in particular a root of a primitive polynomial  $g(x) = x^3 + x + 1$ . Then, a symbolic scheme of Figure 3 will transfer to the logic level circuit of Figure 4, where

$$\alpha^{l} = a_{2}^{(l)} x^{2} + a_{1}^{(l)} x + a_{0}^{(l)}, \qquad a_{i}^{(l)} \in \{0, 1\}, 0 \le i \le 2, \quad 0 \le l \le 6.$$

(5)

This expression indicates the relationship between the power and vector representations of a field element, as reflected in Table 1 (where  $x = \alpha$ ).

If the preliminary "cleared" analyzer receives, for example, the following sequence of 3-bit output responses from

FIGURE 3: A symbolic presentation of a one-stage algebraic signature analyzer.

FIGURE 4: A logic level presentation of the algebraic 3-input signature analyzer.

TABLE 1: Three representations for the elements of  $GF(2^3)$  generated by  $g(x) = x^3 + x + 1$ . Here  $g(\alpha) = 0$ .

| Power                                                                                     | Ι                    | Polynomi  | Vector<br>representation |   |                      |                               |

|-------------------------------------------------------------------------------------------|----------------------|-----------|--------------------------|---|----------------------|-------------------------------|

| representat                                                                               | re                   | presentat |                          |   |                      |                               |

| $\alpha^l$                                                                                | $a_2^{(l)} \alpha^2$ | +         | $a_1^{(l)} \alpha^1$     | + | $a_0^{(l)} \alpha^0$ | $a_2^{(l)}a_1^{(l)}a_0^{(l)}$ |

| 0                                                                                         |                      |           | 0                        |   |                      | 0 0 0                         |

| $lpha^0$                                                                                  |                      |           |                          |   | $\alpha^0$           | 0 0 1                         |

| $\alpha^1$                                                                                |                      |           | $\alpha^1$               |   |                      | 0 1 0                         |

| $\alpha^2$                                                                                | $\alpha^2$           |           |                          |   |                      | 1 0 0                         |

| $ \begin{array}{c} \alpha^1 \\ \alpha^2 \\ \alpha^3 \\ \alpha^4 \\ \alpha^5 \end{array} $ |                      |           | $\alpha^1$               | + | $\alpha^0$           | 0 1 1                         |

| $lpha^4$                                                                                  | $\alpha^2$           | +         | $\alpha^1$               |   |                      | 1 1 0                         |

| $\alpha^5$                                                                                | $\alpha^2$           | +         | $\alpha^1$               | + | $lpha^0$             | 1 1 1                         |

| $\alpha^6$                                                                                | $\alpha^2$           |           |                          | + | $lpha^0$             | 1 0 1                         |

a digital CUT,  $\alpha^5$ ,  $\alpha^6$ ,  $\alpha^4$ ,  $\alpha^2$ ,  $\alpha^1$ ,  $\alpha^0$ , then after the 6th shift its content will become

$$\left(\left(\left(\left(\left(0\cdot\alpha+\alpha^{5}\right)\alpha+\alpha^{6}\right)\alpha+\alpha^{4}\right)\alpha+\alpha^{2}\right)\alpha+\alpha^{1}\right)\alpha+\alpha^{0}=\alpha.$$

(6)

The power representation of the field element,  $\alpha$ , corresponds to the vector representation, 010, which is the actual signature of the CUT.

In contrast to a digital CUT, the output responses of a mixed-signal CUT are distorted even in a fault-free case. Small permissible variations in the responses cause a significant deviation of the final signature. For example, if in the above sequence of output responses the least significant bit in the first response changes from 1 to 0 (i.e., the vector 111 changes to 110, or power  $\alpha^5$  changes to  $\alpha^4$ ), then the actual signature will change from 010 to 101 (or from  $\alpha$  to  $\alpha^6$  in power form).

Apparently, the conventional SA represented in Figures 3 and 4 cannot be employed for mixed-signal circuits testing.

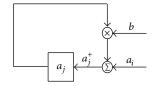

In the known methods, output responses of mixedsignal circuits are compacted by a circuit referred to as a modulo adder (or accumulator, or digital integrator) [4–8]. It should be noted that a modulo adder is a special case of a *residue computing circuit* [14]. A residue computing circuit is represented in Figure 5. Here  $a_i$  is the current content of

FIGURE 5: A symbolic presentation of a one-stage arithmetic signature analyzer.

the register,  $a_i$  is the incoming (arithmetic) symbol, and b is the base of the system. This circuit divides the incoming sequence of symbols,  $a_{m-1}, \ldots, a_1, a_0$ , treated as a number:

$$a = a_{m-1}b^{m-1} + \dots + a_1b + a_0 \tag{7}$$

by the modulus

$$p = p_{t-1}b^{t-1} + \dots + p_1b + p_0, \quad t \ll m.$$

(8)

As in the case with the algebraic SA, we consider a singlestage device; that is, t = 1,  $p = p_0 < b = 2^n$ , where *n* is the number of bits occupied by the symbol. The residue,  $s_0$ , constitutes a signature.

An operational cycle of the circuit in Figure 5 can be described by the expression

$$a_i b + a_i = a_i^+ (\operatorname{mod} p). \tag{9}$$

Although the circuits of Figures 3 and 5 look similar, their implementation is quite different. In general case, the designing procedure for the arithmetic circuits is more complicated and their hardware complexity is greater.

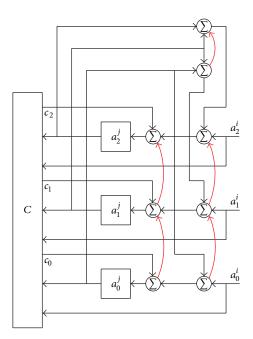

As an example, Figure 6 represents the circuit that computes a modulo 5 residue of the incoming sequence of 3-bit symbols treated as an octal number [14]. Here  $a_i$  is the incoming octal digit and *C* is a combinational circuit which generates the following next state signals:

$$c_{2} = a_{0}^{j}\overline{a_{1}^{j}}a_{0}^{i}a_{1}^{i}a_{2}^{i} + a_{1}^{j}\left(a_{0}^{j}a_{1}^{i}\oplus a_{2}^{i} + a_{0}^{j}a_{0}^{i}\overline{a_{2}^{i}}\right),$$

$$c_{1} = a_{2}^{j}\overline{a_{2}^{i}}\left(\overline{a_{0}^{i}} + \overline{a_{1}^{i}}\right) + \overline{a_{2}^{j}}a_{2}^{i}\left(\overline{a_{0}^{j}}a_{0}^{i} + \overline{a_{1}^{j}}a_{1}^{i}\right)$$

$$+ a_{1}^{j}\left(\overline{a_{0}^{j}} + \overline{a_{2}^{i}}\right) + a_{0}^{j}\left(a_{1}^{i}\oplus a_{2}^{i}\right), \qquad (10)$$

$$c_{0} = a_{0}^{j}a_{1}^{i}\left(\overline{a_{1}^{j}}\oplus a_{2}^{i}\right) + a_{1}^{j}\overline{a_{2}^{i}}\left(\overline{a_{0}^{j}} + \overline{a_{0}^{i}}a_{1}^{i}\right)$$

$$i = \overline{a_{1}^{j}}i \left(\overline{a_{1}^{j}} \oplus a_{2}^{i}\right) + a_{1}^{j}\overline{a_{2}^{i}}\left(\overline{a_{0}^{j}} + \overline{a_{0}^{i}}a_{1}^{i}\right)$$

$+ a_2^{j} + a_1^{j}a_2^{i} \left( a_0^{j}a_1^{i} + a_0^{i}a_1^{i} + a_0^{j}a_0^{i} \right).$ Each shift of this circuit implements the operation  $a_i \times 8 +$

$a_i \pmod{5}$ . In addition to high hardware complexity, the arithmetic compactor contains carry propagating circuitry (shown in red color in Figure 6) that delays the operation and aggravates the effect of a single fault.

Below, we design an algebraic circuit that can be employed for mixed-signal data compaction. It does not contain carry propagating circuitry.

FIGURE 6: A 3-input arithmetic compactor.

#### 3. A Novel Approach

Polynomial (1) in conjunction with the reference signature can be considered as a code word of the code whose minimal distance is defined by the g(x). The distance here is the Hamming distance. This distance characterizes algebraic error-detecting properties of the code and is not convenient for arithmetic errors that occur in mixed-signal systems. Indeed, a small permissible deviation of the data to be compacted causes the reference signature to span the entire space. Under these conditions, the decision making circuit in Figure 1 must be able to compare the actual signature with the entire set of possible reference signatures. This increases the analyzer complexity.

To decrease the complexity, an arithmetic SA treats the sequence of output responses from a mixed-signal circuit as a number (7). In conjunction with the reference residue, this is considered as a code word of an arithmetic errorcontrol code. The properties of this code depend on the arithmetic minimal distance which in turn depends on the modulus p. The arithmetic residue calculating analyzer does not search the entire space, since the space of arithmetic reference signatures is now contiguous. To make a decision, it employs a window comparator. This simplifies the circuitry. However, the hardware complexity of the arithmetic SA can still be quite high, as it was illustrated above.

In the rest of this paper, we will show how to design an algebraic SA, which generates a contiguous space of algebraic reference signatures.

In order to be contiguous, the space of signatures must be ordered. A signature can be represented in the vector or power forms. We will use the power exponent as the criterion for ordering the signature set. The distance between two vectors (signatures) will be evaluated as the arithmetic difference between the corresponding exponents. For example,

FIGURE 7: A symbolic form of an algebraic SA for a mixed-signal CUT.

the distance between the signatures 010 and 101 will be 5, because the exponents of powers  $\alpha^6$  and  $\alpha$  differ by 5. We can interpret these exponents as output responses of a mixedsignal CUT, since they possess arithmetic properties. At the same time, the corresponding vectors (signatures) possess algebraic properties. Therefore, arithmetic data is mapped into algebraic data. Figure 7 represents the circuit which performs the mapping and computes an algebraic signature.

The circuit of Figure 7 can be obtained from the circuit of Figure 3 by the following transform:

$$\alpha^{j}\alpha^{i} = (\alpha^{j}\alpha)\alpha^{i-1} = (\alpha^{j}\alpha)\overbrace{(1+\alpha^{k})}^{\alpha^{i-1}}$$

$$= \alpha^{j}\alpha + \alpha^{j+1+k} = \alpha^{j}\alpha + \alpha^{l}.$$

(11)

Since the finite field  $GF(2^n)$  is closed and errors are independent, this mapping will not change the probability of undetected error.

The logic level implementation of the circuit of Figure 7 is more complex compared to the circuit of Figure 3, but it is less complex than that of the circuit of Figure 5.

Prior to designing the circuit, we have to make a few observations.

The *first* observation is that

$$\alpha^{j}\alpha^{i} = \left(\cdots\left(\alpha^{j}\underline{\alpha}\right)\underline{\alpha}\cdots\right)\underline{\alpha}.$$

(12)

Let us denote an output response from a mixed-signal CUT by *i*. The *second* observation is that the response *i* can be considered as an exponent of the power, that is,  $\alpha^i$ . Essentially, this means that the arithmetic values *i* are mapped into algebraic values  $\alpha^i$ .

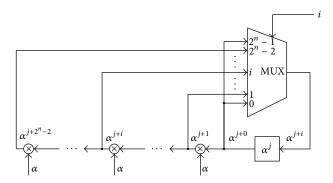

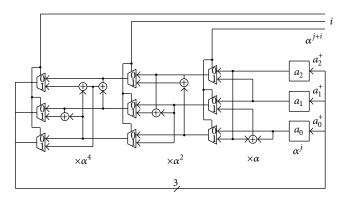

Based on these observations, we can design a signature analyzer in the way shown in Figure 8. Here  $\alpha$  is a primitive element of a finite field  $GF(2^n)$ ; *n* coincides with the bit-length of the output responses. The lower and upper inputs of the multiplexer in Figure 8 are connected together, since  $\alpha^{2^n-1} = \alpha^0$  in  $GF(2^n)$ .

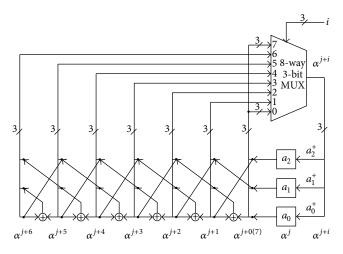

Considering the case when the analyzer is fed by 3-bit data, its more detailed implementation will have the form of Figure 9.

Here the buses consist of 3 lines, as indicated by the appropriate number. The initial content of the SA before the shift is  $\alpha^{j}$ , or  $a_{2}x^{2} + a_{1}x + a_{0}$  in the polynomial form (we have omitted the superscripts for the sake of simplicity). The notations  $a_{k}$  and  $a_{k}^{+}$ , where index k can be one of 0, 1, and 2, indicate the present and next states, respectively.

FIGURE 8: A more detailed symbolic form of the SA.

FIGURE 9: A register transfer level implementation of the SA.

A multiplier by  $\alpha$  in *GF*(2<sup>3</sup>) is realized bearing in mind that  $g(x) = x^3 + x + 1$ ,  $\alpha$  corresponds to *x*, and

$$(a_2x^2 + a_1x + a_0) x \mod g(x)$$

=  $(a_2x^3 + a_1x^2 + a_0x) \mod g(x)$

=  $a_2(x + 1) + a_1x^2 + a_0x$

=  $a_1x^2 + (a_2 + a_0) x + a_2.$  (13)

This operation is shown by crosslines in Figure 9. The multiplexer inputs "0" and "7" are tied together, because  $\alpha^7 = \alpha^0$  in the field *GF*(2<sup>3</sup>).

In order to demonstrate how to use this analyzer, we will assume that it receives only two values from a CUT, in particular *j* and *i*. Since the CUT is of a mixed-signal nature, there is an unavoidable (and thereby permitted) deviation of these values by ±1 (the greater tolerances can also be considered). The analyzer will map the received data into  $\alpha^{j\pm 1}$  and  $\alpha^{i\pm 1}$ , respectively. If we assume that the initial content of the SA is 001 (versus 000 for a conventional SA), then after the first shift the content becomes  $\alpha^0 \alpha^{j\pm 1} = \alpha^{j\pm 1}$ . After the second shift, it changes to  $\alpha^{j\pm 1} \alpha^{i\pm 1} = \alpha^{j+i\pm 2}$ . This expression is derived using the interval arithmetic rules. It states that for the fault-free CUT the actual result must match one of

the values from the interval  $[\alpha^{j+i-2}, \alpha^{j+i+2}]$ , that is, one of the following:

$$\alpha^{j+i-2}, \alpha^{j+i-1}, \alpha^{j+i}, \alpha^{j+i+1}, \alpha^{j+i+2}.$$

(14)

To further simplify the SA operation, we will assume that instead of  $\alpha^0$  (i.e., 001) the initial SA content is  $\alpha^{-(j+i)}$ . We will refer to this value as the *seed* value. Then, by the same reasoning, the SA content after two shifts will match one of the following powers:

$$\alpha^{-2}, \alpha^{-1}, \alpha^0, \alpha^1, \alpha^2.$$

(15)

Due to the closure property of the field  $GF(2^3)$ , this power set is equivalent to

$$\alpha^5, \alpha^6, \alpha^0, \alpha^1, \alpha^2. \tag{16}$$

Consequently, the decision making circuit in Figure 3 will work as follows. If the actual signature does not match any value from set (16), the CUT is considered to be faulty. Since these values are ordered (and surround the power  $\alpha^0$ ), the decision making circuit can employ a comparator, thereby reducing the hardware complexity of the SA.

As in any signature analyzer, some errors in the CUT output responses may escape detection. The aliasing rate can be estimated as described in [16] and will coincide with the aliasing rate of the conventional analyzer.

*Example.* Let us consider a 3-bit CUT, which is fed by two input stimuli. Under the fault-free operation, the CUT produces the output responses  $j = 101 \pm 1$  and  $i = 110 \pm 1$ . Therefore, the seed value will be  $\alpha^{-(j+i)} = \alpha^{-(5+6)} = \alpha^{-11} = \alpha^3$ , or 011 in the vector form. If the CUT is fault-free, then after 2 shifts the SA content must match one of the elements in set (16). For example, if the actual responses are 101 + 1 = 110 (or  $\alpha^6$ ) and 110 + 1 = 111 (or  $\alpha^7$ ) (i.e., the variations are within the tolerance bounds), the signature will be  $\alpha^3 \alpha^6 \alpha^7 = \alpha^2$  which belongs to set (16). And the decision making circuit will generate a *pass* signal. The validity of such a decision is determined by the aliasing rate.

Let us assume that a fault in the CUT has made the following changes in the output responses:  $110 \rightarrow 011$  $(\alpha^6 \rightarrow \alpha^3)$  and  $111 \rightarrow 100 (\alpha^7 \rightarrow \alpha^4)$ . Then the actual signature will become  $\alpha^3 \alpha^3 \alpha^4 = \alpha^3$ . This element does not belong to set (16), so the fault is detected.

There are two distinct ways of designing the decision making circuit depending on the optimization criteria (time or hardware overhead).

*Hardware Overhead.* If performance is paramount and time overhead is not desirable, the following approach can be employed. Let *m* be the number of output responses. All of the  $2m + 1 \alpha$ -multiplier outputs (see Figure 8) that belong to set (16) are connected to the first inputs of the 2m+1 comparators of a similar type. The second inputs of these comparators are shared and fed by the vector  $0 \cdots 01$ . If the CUT is fault-free, one of the comparators will produce a logic "1" signal. The logic OR of the comparator outputs will constitute a *pass/fail* signal.

FIGURE 10: An *n*-bit comparator.

The above procedure is based on the fact that the faultfree CUT produces one of the signatures from set (16). If the actual signature is  $\alpha^0$ , the comparator connected directly to the signature register produces a logic "1," thus indicating that the CUT is fault-free. If the actual signature is  $\alpha^6$ , then the product  $\alpha^6 \alpha$ , generated at the output of the first  $\alpha$ -multiplier, equals 1, which is detected by the next comparator. The same reasoning applies to the rest of the signatures from set (16). The logic diagram of the *n*-bit comparator is shown in Figure 10.

*Time Overhead*. If time overhead is allowed, the hardware complexity can be further reduced. In terms of implementation, it is more convenient to use the following seed value:  $\alpha^{-(j+i+m+1)}$ , where *m* is the number of output responses. For the above example,  $\alpha^{-(11+3)} = \alpha^0$ , and set (16) will transform to

$$\alpha^2, \alpha^3, \alpha^4, \alpha^5, \alpha^6. \tag{17}$$

After the last output response has been shifted in, the SA continues to shift its content 2m + 1 more times, while the input *i* is forced to 1. This ensures that the SA content is multiplied by  $\alpha$  with each shift. For the above example, 2m + 1 = 5. If, within this time, the match with an element of set (17) has been determined, the CUT is considered to be fault-free. Otherwise, it is faulty.

If the CUT is fault-free and its output responses have not exceeded their tolerances, then while cycling through the states during the extra 2m + 1 shifts, the output of the multiplexer in Figure 8 will go through the power  $\alpha^0$  or vector  $0\cdots01$ . The match with the vector  $0\cdots01$ is detected by the comparator of Figure 10 connected to the multiplexor's output. The comparator output is actually producing a *pass/fail* signal.

The implementation complexity of the circuit of Figure 8 increases significantly with the growth of the data width, *n*. Therefore, this circuit can only be implemented for the output responses with relatively low values of *n*. For greater values of *n*, we will modify the circuit of Figure 8 to the one shown in Figure 11. The modified circuit contains binary-weighted stages and is more economical in terms of hardware. The complexity of the multiplier  $\times \alpha^i$  is comparable with that of the multiplier  $\times \alpha$ , whereas the number of multipliers drops from  $2^n$  to *n*. The economy increases with the growth of *n*.

For the case of 3-bit data, the circuit of Figure 11 transfers to the one shown in Figure 12. This circuit operates much in the same way. The  $\alpha^i$ -multipliers structure is determined from the following expressions:

$$x (a_2 x^2 + a_1 x + a_0) \mod g(x)$$

=  $a_1 x^2 + (a_2 + a_0) x + a_2$ ,

FIGURE 11: A binary-weighted version of the SA.

FIGURE 12: A register transfer level implementation of the 3-bit SA.

$$x^{2} (a_{2}x^{2} + a_{1}x + a_{0}) \mod g (x)$$

=  $(a_{2} + a_{0}) x^{2} + (a_{2} + a_{1}) x + a_{1},$

$x^{4} (a_{2}x^{2} + a_{1}x + a_{0}) \mod g (x)$

=  $(a_{2} + a_{1} + a_{0}) x^{2} + (a_{1} + a_{0}) x + (a_{2} + a_{1}).$

(18)

#### 4. Experimental Results

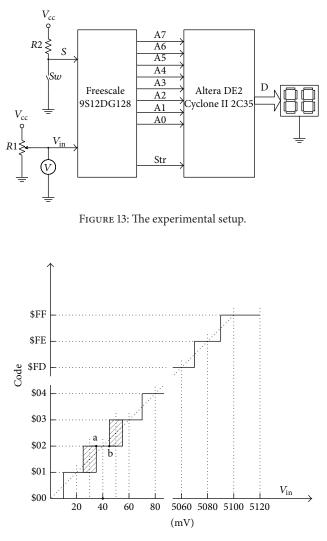

The experimental setup to test the proposed method of signature analysis is shown in Figure 13. The setup includes the microcontroller system board Adapt9S12D (Technological Arts Inc.) based on Freescale's 9S12DG128 microcontroller and the Altera DE2 Development board based on the Cyclone II EP2C35F672C6 field-programmable gate-array (FPGA) device. We have selected 16 input test stimuli (voltages  $V_{in}$ ) equally distributed over the range (0 ~ 5.12)V and applied them to the analog-to-digital converter (ADC) of the 9S12 microcontroller (which served as a mixed-signal system). Each input voltage,  $V_{in}$ , was measured by a high-precision voltmeter and regarded as a nominal test input value.

The circuit in Figure 13 operates as follows. Every time the switch S $\omega$  is closed, the system performs 8 measurements of the same test signal and averages the result by accumulating the sum of the eight 8-bit measurements and shifting it right three times, which eliminates noise. The ADC transfer characteristic is presented in Figure 14 [17]. According to this characteristic, each conversion result for a properly operating device can deviate from the nominal value by ±1, which is an implication of the fact that the permissible

FIGURE 14: 9S12 ADC transfer function.

differential nonlinearity can range from -0.5 to +0.5 LSB (see shadowed boxes in Figure 14). For example, if  $V_{\rm in} = 40$  mV, the conversion result can be \$01, \$02, or \$03 (in the worst case, the points *a* and *b* coincide). Therefore, each of the thirty-two 8-bit average results contains an error of at most  $\pm 1$  count. The test stimuli have been selected equal to the midpoints of the quantization bins, thereby increasing the uncertainty and worsening the probability of undetected error. If the test stimuli would have been selected at the transition points of the characteristic, the probability of undetected error (aliasing rate) would improve. This follows from the observation that each conversion would result in 2 possible values as opposed to 3 possible values in the previous case.

As soon as average values of the conversion results are computed by the microcontroller, they are transferred to the DE2 board. The transfer of each datum is accompanied by a high-to-low transition of the strobe signal *Str*. The *Str* signal serves as a *clock* for the state machine that implements the signature analyzer (in its 8-bit configuration). The signature, *D*,

TABLE 2: Relationship between input test stimuli and output responses.

| Input voltage |     | Output code |     |          |       |  |  |  |  |  |  |

|---------------|-----|-------------|-----|----------|-------|--|--|--|--|--|--|

| mV            | Min | Nom.        | Max | No fault | Fault |  |  |  |  |  |  |

| 80            | 3   | 4           | 5   | 3        | 3     |  |  |  |  |  |  |

| 400           | 19  | 20          | 21  | 21       | 21    |  |  |  |  |  |  |

| 720           | 35  | 36          | 37  | 37       | 37    |  |  |  |  |  |  |

| 1040          | 51  | 52          | 53  | 53       | 53    |  |  |  |  |  |  |

| 1360          | 67  | 68          | 69  | 68       | 70    |  |  |  |  |  |  |

| 1680          | 83  | 84          | 85  | 85       | 85    |  |  |  |  |  |  |

| 2000          | 99  | 100         | 101 | 99       | 99    |  |  |  |  |  |  |

| 2320          | 115 | 116         | 117 | 117      | 117   |  |  |  |  |  |  |

| 2640          | 131 | 132         | 133 | 133      | 133   |  |  |  |  |  |  |

| 2960          | 147 | 148         | 149 | 148      | 150   |  |  |  |  |  |  |

| 3280          | 163 | 164         | 165 | 165      | 165   |  |  |  |  |  |  |

| 3600          | 179 | 180         | 181 | 179      | 179   |  |  |  |  |  |  |

| 3920          | 195 | 196         | 197 | 197      | 197   |  |  |  |  |  |  |

| 4240          | 211 | 212         | 213 | 212      | 240   |  |  |  |  |  |  |

| 4560          | 227 | 228         | 229 | 229      | 230   |  |  |  |  |  |  |

| 4880          | 243 | 244         | 245 | 244      | 244   |  |  |  |  |  |  |

is displayed on a two-digit 7-segment display in hexadecimal form.

The first experiment was performed on the properly operating device. In the second experiment, the average results were corrupted digitally in the microcontroller (thereby simulating random faults in the ADC) and sent to the analyzer. The analyzer has correctly identified the faulty device.

The relationship between input voltages and output codes is presented in Table 2. Based on this table and taking into consideration that  $g(x) = x^8 + x^4 + x^3 + x^2 + 1$ , the seed value is calculated as follows:

$$4 + 20 + \dots + 244 = 1984 = 199 \mod (2^8 - 1) = 199,$$

$$\alpha^{-199} = \alpha^{56} = 01011101, \tag{19}$$

Seed Value =  $\alpha^{56} \alpha^{-16} = \alpha^{40} = 01101010 = 106$ .

In addition to test experiments, the operation of the analyzer (the DE2 part of the test setup) was simulated using Altera Quartus II software. Based on the two experiments represented in Table 2, the signatures that correspond to fault-free and faulty ADCs are, respectively, 233 and 201 (in decimal form). The process of calculation of these signatures is demonstrated in Figures 15 and 16. Figures 17 and 18 represent the fault detection process. The actual final signatures are shifted additionally 32 times. If the value 1 appears in the analyzer during these shifts, the system is fault-free. Otherwise it is faulty.

The simulation results matched the experimental results.

#### 5. Conclusion

We examined an algebraic signature analysis method that can be employed for mixed-signal circuits testing. We demonstrated how to design the appropriate device. This device does

| Name     | 0 ps 2.0 us 4.0 us 6.0 us 8.0 us 10.0 us 12.0 us 14.0 us 16.0 us<br>0 ps                                        |

|----------|-----------------------------------------------------------------------------------------------------------------|

| -ck      | ion and the second s |

| res      |                                                                                                                 |

| ⊕ seed   | 106                                                                                                             |

| 🗉 sin    | X X 3 ) 21 ( 37 ( 53 ) 68 ( 85 ) 99 (117)(133)(148)(165)(179)(197)(212)(229)(244))                              |

| i ⊡ sout | (X(106)(119)(95)(34)(57)(138)(20)(170)(135)(154)(53)(221)(133)(94)(12)(2)(233)                                  |

FIGURE 15: All output code deviations are within the tolerance bounds.

| Name     | 0 ps 2.0 us 4.0 us 6.0 us 8.0 us 10.0 us 12.0 us 14.0 us 16.0 us<br>0 ps       |

|----------|--------------------------------------------------------------------------------|

| -dk      |                                                                                |

| - res    |                                                                                |

| e 🗉 seed | 106                                                                            |

| e 🙂 sin  | (X)(3)(21)(37)(53)(70)(85)(99)(117)(133)(150)(165)(179)(197)(240)(230)(244)(3) |

| 5 E sout | 0((106)(119)(95)(34)(57)(18)(80)(146)(38)(82)(119)(81)(184)(137)(210)(78)(201) |

FIGURE 16: Some of the output code deviations exceed the tolerance bounds.

|       | emsk | 0 ps | 2.0 US   | 4.0 us  | 6.0 us     | 8.0 us | 10.0 us    | 12.0 us | 14.0 us | 16.0 us | 18.0 us   | 20.0 US | 22.9 US   | 24.0 us  | 26.0 us | 28.0 us | 30.0 us | 32.0 us    |

|-------|------|------|----------|---------|------------|--------|------------|---------|---------|---------|-----------|---------|-----------|----------|---------|---------|---------|------------|

|       |      | U ps |          |         |            |        |            |         |         |         |           |         |           |          |         |         |         |            |

|       | ck   |      |          | ЧЦГ     |            |        | ццц        |         |         | ЦЦЦ     |           |         | ццц       |          |         | ЦЦ      | ЦЦ      | ицц.       |

| 5-11  | res  |      |          |         |            |        |            |         |         |         |           |         |           |          |         |         |         |            |

| 3 4 3 | seed |      |          |         |            |        |            |         |         | 233     |           |         |           |          |         |         |         |            |

| 5     | sin  | XX   | 111      |         |            |        |            |         |         |         | 1         |         |           | 1.1.1    |         | 1.1.1   |         |            |

| 15 a. | sout | 8023 | 3(207)(1 | 31 27 1 | 54 (108) 7 | 16 173 | 71 (142)(1 | X2X.    | 4 8 1   | 6 32 6  | 1 (178) 2 | 9 58 1  | 16 032 00 | 5(135) 1 | 0 38 7  | 6 152 4 | 5 00 1  | 80(117)734 |

FIGURE 17: The combination "1" is detected: ADC is operating properly.

|     | Name | 0 ps<br>0 ps | 2.0 us | 4.0 us  | 6.Q US    | 8.0 us     | 10.9 us  | 12.0 us | 14.0 us     | 16.0 us   | 18.0 us   | 20.0 us  | 22.0 us  | 24.0 us  | 26.0 us   | 28.0 us  | 30.0 us  | 32.0 us      |

|-----|------|--------------|--------|---------|-----------|------------|----------|---------|-------------|-----------|-----------|----------|----------|----------|-----------|----------|----------|--------------|

| 3   | -dk  | tu           | LП     | лл      | лл        |            | пл       | пп      | лл          | пп        |           | лл       | лл       |          | пп        | пп       | пп       | ייייי        |

| 3   | res  | L.           |        | 1111    |           |            | 111      | 114     |             |           | 111       | 1111     |          | 111      |           | 1111     |          |              |

| 5 8 | seed |              |        |         |           |            |          |         |             | 20        |           |          |          |          |           |          |          |              |

| 5 8 | sin  | XX           |        |         |           |            |          |         |             |           | 1         |          |          |          |           |          |          |              |

| 5.  | sout | 5020         | 1/1437 | 3 X 6 X | 12 124 14 | 18 Y 96 Y1 | 211571 3 | 9 78 X1 | \$6X 37 X 7 | 4 (148) 5 | 3 (106)/2 | 12/181/1 | 10)738/1 | 3Y150Y 3 | 5 Y 70 Y1 | ANY SY 1 | 01 20 14 | HO X 80 X160 |

FIGURE 18: The combination "1" is not detected: ADC is faulty.

not produce arithmetic carries and is therefore less prone to errors. The absence of carry propagating circuitry also contributes to the higher performance of the device.

The proposed scheme can also be used in arithmetic and algebraic error-control coding, as well as cryptography.

#### **Conflict of Interests**

The authors declare that there is no conflict of interests regarding the publication of this paper.

#### References

- R. Frohwerk, "Signature analysis: a new digital field service method," *Hewlett-Packard Journal*, vol. 28, no. 9, pp. 2–8, 1977.

- [2] G. J. Starr, J. Qin, B. F. Dutton, C. E. Stroud, F. F. Dai, and V. P. Nelson, "Automated generation of built-in self-test and measurement circuitry for mixed-signal circuits and systems," in *Proceedings of the 15th IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems (DFT '09)*, pp. 11– 19, October 2009.

- [3] D. K. Pradhan and S. K. Gupta, "A new framework for designing and analyzing BIST techniques and zero aliasing compression," *IEEE Transactions on Computers*, vol. 40, no. 6, pp. 743–763, 1991.

- [4] C. Stroud, J. Morton, T. Islam, and H. Alassaly, "A mixed-signal builtin self-test approach for analog circuits," in *Proceedings of the Southwest Symposium on Mixed-Signal Design*, pp. 196–201, 2003.

- [5] N. Nagi, A. Chatterjee, H. Yoon, and J. A. Abraham, "Signature analysis for analog and mixed-signal circuit test response compaction," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 17, no. 6, pp. 540–546, 1998.

- [6] N. Nagi, A. Chatterjee, and J. A. Abraham, "Signature analyzer for analog and mixed-signal circuits," in *Proceedings of the IEEE International Conference on Computer Design: VLSI in Computers and Processors*, pp. 284–287, October 1994.

- [7] S. Mir, M. Lubaszewski, V. Liberali, and B. Courtois, "Built-in self-test approaches for analogue and mixed-signal integrated circuits," in *Proceedings of the IEEE 38th Midwest Symposium on Circuits and Systems*, vol. 2, pp. 1145–1150, Rio de Janeiro, Brazil, August 1995.

- [8] J. Rajski and J. Tyszer, "The analysis of digital integrators for test response compaction," *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, vol. 39, no. 5, pp. 293–301, 1992.

- [9] L. Wei and L. Jia, "An apprach to analong and mixed-signal BIST based-on pseudorandom testing," in *Proceedings of the IEEE International Conference on Communications, Circuits and Systems, (ICCCAS '08)*, pp. 1192–1195, Fujian, China, May 2008.

- [10] F. Corsi, C. Marzocca, and G. Matarrese, "Defining a BISToriented signature for mixed-signal devices," in *Proceedings of the IEEE Southwest Symposium on Mixed-Signal Design*, pp. 202–207, 2003.

- [11] S. Demidenko, V. Piuri, V. Yarmolik, and A. Shmidman, "Bist module for mixed-signal circuits," in *Proceedings of the IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems*, pp. 349–352, 1998.

- [12] T. Damarla, "Implementation of signature analysis for analog and mixed signal circuits," U.S. Patent 6 367 043, 2002.

- [13] W. W. Peterson and J. Weldon, *Error Correcting Codes*, MIT Press, Cambridge, Mass, USA, 2nd edition, 1972.

- [14] V. Geurkov, "Optimal choice of arithmetic compactors for mixed-signal systems," in *Proceedings of the IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT '12)*, pp. 182–186, October 2012.

- [15] S. Lin and D. Costello, *Error Control Coding*, Pearson Education, Upper Saddle River, NJ, USA, 2004.

- [16] V. Geurkov, V. Kirischian, L. Kirischian, and R. Sedaghat, "Concurrent testing of analog-to-digital converters," *i-manager's Journal on Electronics Engineering*, vol. 1, no. 1, pp. 8–14, 2010.

- [17] MC9S12DT128 Device User Guide, V02.11, Motorola, May 2004, http://www.freescale.com/.