Hindawi Publishing Corporation Advances in Condensed Matter Physics Volume 2015, Article ID 639218, 9 pages http://dx.doi.org/10.1155/2015/639218

# Review Article

# **Interface Engineering and Gate Dielectric Engineering for High Performance Ge MOSFETs**

## Jiabao Sun and Jiwu Lu

Department of Information Science and Electronic Engineering, Zhejiang University, No. 38 Zheda Road, Hangzhou 310027, China

Correspondence should be addressed to Jiwu Lu; jiwu\_lu@zju.edu.cn

Received 3 October 2014; Accepted 1 December 2014

Academic Editor: Rui Zhang

Copyright © 2015 J. Sun and J. Lu. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

In recent years, germanium has attracted intensive interests for its promising applications in the microelectronics industry. However, to achieve high performance Ge channel devices, several critical issues still have to be addressed. Amongst them, a high quality gate stack, that is, a low defect interface layer and a dielectric layer, is of crucial importance. In this work, we first review the existing methods of interface engineering and gate dielectric engineering and then in more detail we discuss and compare three promising approaches (i.e., plasma postoxidation, high pressure oxidation, and ozone postoxidation). It has been confirmed that these approaches all can significantly improve the overall performance of the metal-oxide-semiconductor field effect transistor (MOSFET) device.

#### 1. Introduction

After continuously pursuing higher performance complementary metal-oxide-semiconductor field effect transistor (MOSFET) devices for more than four decades, it is becoming increasingly difficult for Si-based MOSFET to enhance performance through traditional device scaling [1–5]. Recently, Ge has attracted intensive interests as the most promising channel material for next generation MOSFET because of the intrinsic higher carrier mobility in Ge than that in Si (2x higher mobility for electrons and 4x for holes) [6–14]. In order to realize high performance Ge p-type MOSFETs, advanced high-k/Ge gate stacks with scaled EOT and superior MOS interfaces are mandatory [15, 16]. Electrically active defects on the Ge surface and Ge/oxide interfaces are suspected as the probable cause of the mobility degradation of performance characteristics in MOSFETs. Hence, high quality MOS interfaces are not guaranteed due to the large amount of defects at direct high-k/Ge interfaces [17]. To solve this problem, an interfacial layer (IL) is introduced between the high-*k* layer and the Ge substrate, which can provide effective electrical passivation of the Ge surface. Among a variety of ILs, high quality GeO2 has been considered as the most promising choice due to its extremely low interface defect

density  $D_{\rm it}~(\sim 6\times 10^{10}~{\rm cm}^{-2}{\rm eV}^{-1})$  [18] and its potential to enable high performance Ge n-MOSFETs [19]. But there is a problem: the formation of volatile GeO either during growth or at elevated temperatures around 550°C-600°C, which are often used in MOSFET processing. Initially it was believed that GeO is formed at the interface between GeO<sub>2</sub> and Ge. More experimental evidences though suggest that GeO is formed at the top surface of GeO<sub>2</sub> and desorbs at high enough temperature [20-22]. In addition, the relative dielectric constant (k-value) of GeO2 is much lower than that of Hf- and La-based high-k gate dielectrics used for advanced Si technology [23-30]. This means that gate stacks containing thick interfacial GeO2 layers are difficult to scale below 1 nm EOT as required for future technology nodes. Therefore, a high-k/GeO<sub>2</sub> IL/Ge gate stack with a high quality and ultrathin GeO2 interfacial layer is obviously required to achieve subnanometer overall EOT in high performance Ge MOSFETs. The biggest challenge at present is how to manufacture, in a controlled manner, an ultrathin GeO<sub>2</sub> passivation layer without compromising its electrical quality.

The most promising route is to use well-controlled oxidation method to introduce the GeO<sub>2</sub> IL of very good quality. Recently, it has been reported that high quality GeO<sub>2</sub>/Ge interfaces have been fabricated by thermal oxidation [31],

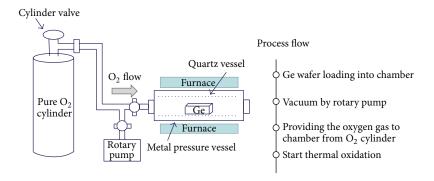

FIGURE 1: Schematic illustration of HPO system and process flow [35].

ozone oxidation [32], plasma oxidation [33], and so forth. Among them, high-temperature thermal oxidation [34] and ozone oxidation [35] can realize superior  $\text{GeO}_2/\text{Ge MOS}$  interfaces with a  $D_{\rm it}$  value less than  $5\times 10^{11}\,\text{cm}^{-2}\text{eV}^{-1}$ . Plasma postoxidation enables the formation of ultrathin  $\text{GeO}_x$  interfacial layer between high-k dielectrics and Ge, suitable for equivalent oxide thickness (EOT) scaling while keeping low  $D_{\rm it}~(\sim 5\times 10^{10}\,\text{cm}^{-2}\text{eV}^{-1})$  [33]. In this review, the three effective oxidation methods will be discussed in detail.

## 2. Ge/Dielectric Interface Passivation Methods

2.1. High-Pressure Oxidation. Many approaches were investigated to form a stable and desirable  ${\rm GeO_2}$  IL in high- $k/{\rm Ge}$  gate stack. One of the most effective methods was high-pressure oxidation. Lee et al. recently reported that the high-pressure oxidation (HPO) of germanium (Ge) for improving electrical properties of Ge/dielectric stacks was investigated [11, 34–39]. Figure 1 shows the schematic illustration of HPO system and the process flow used in their work. The system mainly composes of an oxygen cylinder, a vacuum pump, and a tube furnace. The furnace consists of a quartz oxidation tube enclosed in a steel pressure vessel.

During the process, the HPO system is evacuated to approximately 1Pa by rotary pump after the cleaned Ge wafers are placed into quartz oxidation tube. Then, the furnace chamber surrounding the steel pressure vessel is heated to a thermal oxidation temperature. Temperature calibration of HPO furnace was carried out in the temperature range from 200°C to 600°C for precise measurements [35].

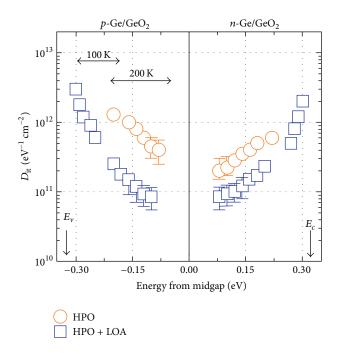

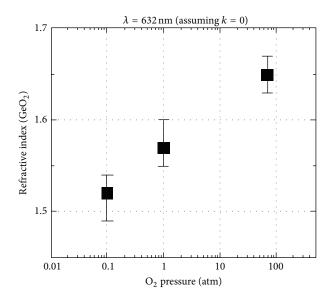

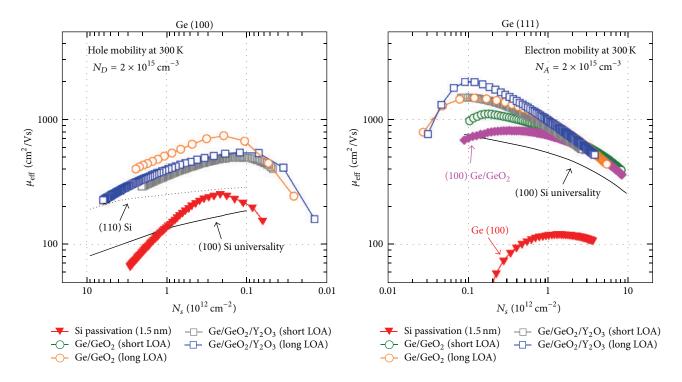

By applying the HPO method followed by low-temperature oxygen annealing (LOA), the interface state density was reduced to less than 10<sup>11</sup> cm<sup>-2</sup>eV<sup>-1</sup> near the midgap, as shown in Figure 2. Moreover, the refractive index of thermally oxidized GeO<sub>2</sub> was increased by HPO which is indicating higher density of GeO<sub>2</sub> grown by HPO, as shown in Figure 3. It was also revealed that the dielectric constant of GeO<sub>2</sub> increases from 5.2 in the case of atmospheric-pressure oxidation (APO) to 5.8 in the case of HPO. With HPO method followed by LOA, Lee et al. also obtained the highest hole mobility of 725 cm<sup>2</sup>/Vs in Ge/GeO<sub>2</sub> gate stack which is 3.5 times higher than (100) Si universal mobility. With this method, they also demonstrated the highest electron mobility

Figure 2: Energy distribution of the interface states density ( $D_{\rm it}$ ) estimated by the conductance method at 100 and 200 K. [37].

of 1920 cm<sup>2</sup>/Vs in Ge/GeO<sub>2</sub>/Y<sub>2</sub>O<sub>3</sub> gate stack, as shown in Figure 4. Both are the record-high values of Ge MOSFETs, and this is a strong evidence that high quality Ge interface from conduction to valence band edge is possible by the Ge surface passivation. Discussed from a thermodynamic point of view, the GeO desorption from Ge/GeO<sub>2</sub> stacks could be efficiently suppressed by HPO.

Furthermore, by applying the combination of  $Y_2O_3$  and low-temperature high-pressure oxidation (LT-HPO) method, Lee et al. also have demonstrated the peak mobility of  $787\,\mathrm{cm}^2/\mathrm{Vs}$  and high- $N_s$  mobility (at  $N_s=1\times10^{13}\,\mathrm{cm}^{-2}$ ) of  $429\,\mathrm{cm}^2/\mathrm{Vs}$  in Ge n-MOSFET with sub-nm EOT, which are the highest ones to date among scaled Si and Ge MOSFETs [38]. It is expected that electrical properties of  $\mathrm{GeO}_2$  metalinsulator-semiconductor capacitor (MISCAP) can be further improved by optimizing the oxidation temperature and oxygen pressure of HPO.

FIGURE 3: Refractive index (n) of GeO<sub>2</sub> films estimated by spectroscopic ellipsometry at  $\lambda$  of 632.8 nm under the assumption that the extinction coefficient is zero [35].

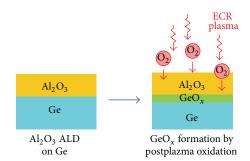

2.2. Plasma Postoxidation. O2 plasma treatment is a very effective approach to form low defect GeO<sub>2</sub>/Ge interfaces and GeO<sub>2</sub> IL at low substrate temperatures, due to the highly reactive O radicals [48, 49]. Zhang et al. have proposed a novel GeO<sub>2</sub> IL formation process by applying the electron cyclotron resonance (ECR) oxygen plasma to form high quality GeO<sub>x</sub> ILs through a thin Al<sub>2</sub>O<sub>3</sub> oxygen barrier, which can realize a low  $D_{it}$  and a thin EOT of around 1 nm at the same time [33]. The basic process flow is shown in Figure 5. In this plasma postoxidation method, a thin GeO<sub>x</sub> IL is formed by oxidizing the Ge surface beneath a thin Al<sub>2</sub>O<sub>3</sub> layer. The Al<sub>2</sub>O<sub>3</sub> serves as a sufficient oxygen barrier which suppresses the growth of unnecessarily thick GeO<sub>x</sub> IL. In more detail, an ultrathin (1-1.5 nm) Al<sub>2</sub>O<sub>3</sub> layer is first deposited on Ge by atomic layer deposition, followed by oxygen plasma treatment to oxidize the Ge substrate. The Al<sub>2</sub>O<sub>3</sub> layer then acts as a barrier layer of oxygen and effectively protects Ge surfaces from direct exposure of ECR oxygen plasma and any damages during the fabrication processes. In addition, low processing temperature provided by the ECR plasma oxidation is expected to minimize the thermal degradation of the GeO<sub>x</sub>/Ge interface. They have improved this process to realize EOT less than 1 nm by employing this plasma postoxidation (PPO) process to HfO<sub>2</sub>-based gate stacks [45].

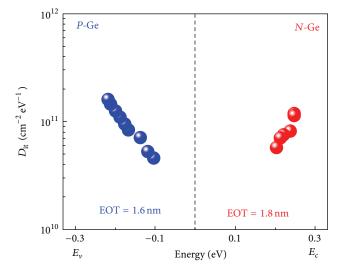

A plasma postoxidation time of 10 s is sufficient to reduce  $D_{\rm it}$  while maintaining the equivalent oxide thickness (EOT). The  $D_{\rm it}$  of Au/Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge MOS capacitors is found to be significantly suppressed down to a value lower than  $10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup>. As shown in Figure 6, they can achieve the minimum  $D_{\rm it}$  of  $5 \times 10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup> and  $6 \times 10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup> for pMOS (1.67 nm EOT) and nMOS (1.83 nm) capacitors, respectively.

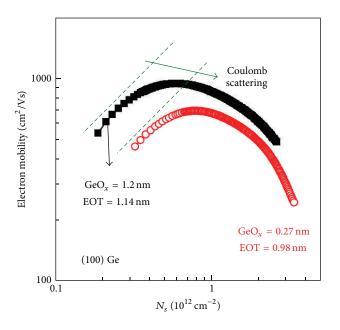

High performance Ge MOSFETs with 0.98 nm (EOT) Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge gate stack have also been demonstrated by

Zhang et al. [12]. The Ge n-MOSFETs have a record-high peak mobility of 937 cm²/Vs as shown in Figure 7, and the Ge pMOSFETs with EOTs of 1.18, 1.06, and 0.98 nm have provided peak mobility values of 515, 466, and 401 cm²/Vs, respectively. The Ge pMOSFET with an EOT of 0.98 nm has been found to provide around 1.8 times mobility enhancement against the previously reported values at this EOT value.

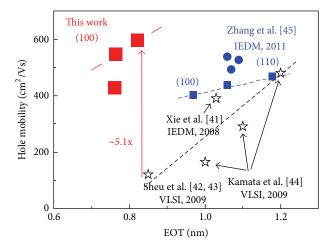

Figure 8 shows the mobility benchmark of Ge pMOS-FETs in the ultrathin EOT range. From the comparison among the data record so far, a record-high peak mobility (596 cm²/Vs) has been achieved in EOT of ~0.8 nm for  $HfO_2/Al_2O_3/GeO_x/Ge$  pMOSFETs, which is 5.1 times large as the previous value. This proves the novel gate stack structure and plasma postoxidation method can provide sufficient MOS interface passivation. In the same work, a high quality gate stack ( $HfO_2/Al_2O_3$  (0.2 nm)/ $GeO_x/Ge$ ) with a record 0.7 nm EOT was also successfully demonstrated. The  $D_{\rm it}$  of this 0.7 nm gate stack is in the order of  $10^{11}$  cm $^{-2}$ eV $^{-1}$ , which leads to a record 546 cm $^2$ /Vs peak mobility.

So, we can conclude that, by applying the PPO method, one can realize both ultrathin EOT less than 1 nm and low  $D_{\rm it}$  value at the same time. As a result, the ECR plasma postoxidation method is a promising solution for fabricating advanced high- $k/{\rm GeO}_x/{\rm Ge}$  gate stacks with superior MOS interfaces and thin EOT.

$2.3.\ Ozone\ Postoxidation.$  Ozone oxidation provides an alternative method to form a high quality  ${\rm GeO_2}$  IL. The minimum  $D_{\rm it}$  of  $3\times 10^{11}\ {\rm cm^{-2}eV^{-1}}$  was demonstrated by using ozone oxidation at  $400\ ^{\circ}{\rm C}$  [32]. In previous experimental investigation, Kuzum et al. demonstrated a ~1.5 times higher mobility than universal Si mobility, where a  ${\rm GeO_2}$  passivation layer was first formed by ozone oxidation and an  ${\rm Al_2O_3}$  dielectric was followed by ALD [50]. Considering the promising aspect of this ozone-based surface passivation, in the remainder of this review, the research of ozone postoxidation for Ge surface passivation will be discussed in more detail.

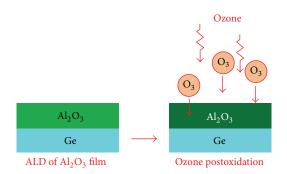

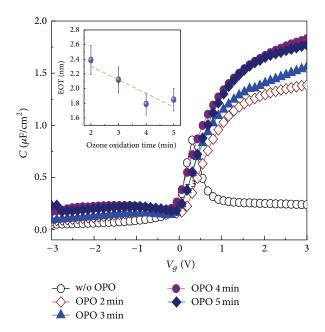

Aiming at realizing Ge surface passivation and thin EOTs at the same time, Sun et al. proposed a new ozone postoxidation (OPO) method for  $Al_2O_3/Ge$  MOS devices [46]. The OPO treatment performed on  $Al_2O_3/Ge$  gate stack is schematically shown in Figures 9 and 10 comparing the C-V characteristics of  $Al_2O_3/Ge$  MOS capacitors with different OPO times. It could be found that the sample without the OPO treatment process exhibits very poor C-V behaviors, and the C-V properties were significantly improved with the increase of the OPO time. The inset shows the EOT value of the capacitors decreases from  $\sim$ 2.39 nm to  $\sim$ 1.79 nm with the increasing time of OPO.

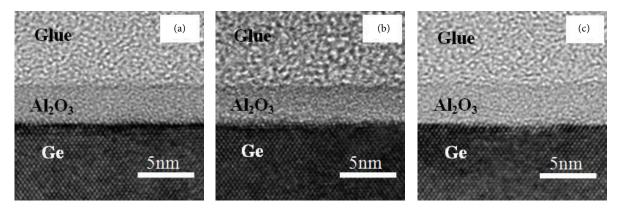

In order to investigate the impact of OPO treatment on the interface features of  ${\rm Al_2O_3/Ge}$  gate stack, the high-resolution cross-sectional transmission electron microscopy (HR-TEM) images were taken and shown in Figure 11. It can be seen that the as-deposited sample is uniform and amorphous with a sharp interface. The physical thickness of the  ${\rm Al_2O_3}$  layer is deduced to be 3.6 nm. Furthermore, there was no  ${\rm GeO_2}$  interfacial layer (IL) growth between  ${\rm Al_2O_3}$

FIGURE 4: A hole mobility of  $725 \, \text{cm}^2/\text{Vs}$  was achieved in  $\text{Ge/GeO}_2$  gate stack with long LOA, which is 3.5 times higher than Si universal mobility. In case of electron mobility,  $\text{Ge/GeO}_2/\text{Y}_2\text{O}_3$  gate stack shows the highest electron mobility of  $1920 \, \text{cm}^2/\text{Vs}$ . Both are record-high values of Ge MOSFETs [11].

FIGURE 5:  $Al_2O_3/GeO_x/Ge$  gate stack formation process by using oxygen plasma through a thin ALD  $Al_2O_3$  layer [40].

films and Ge substrates even after the OPO treatment for 3 and 5 min.

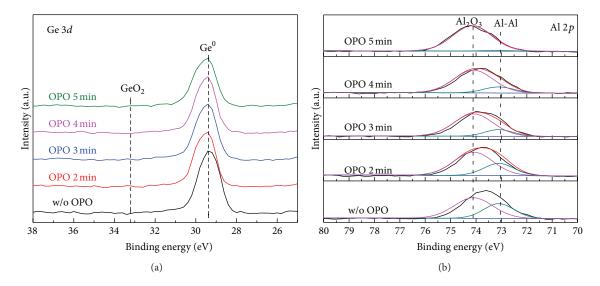

To further understand the impact of the OPO treatment on  $Al_2O_3$ /Ge gate stack, the chemical components of  $Al_2O_3$  films and the interfacial stoichiometry of all samples were examined by X-ray photoelectron spectroscopy (XPS) measurement. As shown in Figure 12, except the  $Ge^0$  component, no germanium-related peak signals could be observed in the XPS spectrum of both as-deposited and OPO treated samples. This indicates that the Ge substrate was not oxidized after the OPO treatment even for 5 min or the amount of the  $GeO_x$  at the interface is under the XPS's detection limit. It could also be found that the Al 2p spectrum of as-deposited sample exhibits two split peaks of Al–Al bonding at 73.0 eV and Al–O bonding at 74.1 eV, indicating

FIGURE 6:  $D_{\rm it}$  distribution of the Au/Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge MOS capacitors versus energy [33].

the coexistence of the oxygen-deficient composition and the stoichiometric composition in the  $\mathrm{Al_2O_3}$  film. From the OPO treated samples' XPS spectra, we could find that the Al–Al bonding feature intensity rapidly decreases, while the Al–O bonding feature intensity continues to increase with the increase in the OPO time. It indicates that the OPO treatment could cure the oxygen deficiency in the  $\mathrm{Al_2O_3}$  film and finally enhance the average oxygen content of the film.

FIGURE 7: Mobilities of Ge n-MOSFETs with an  ${\rm Al_2O_3/GeO_x/Ge}$  gate stack having different  ${\rm GeO_x}$  IL thickness [12].

FIGURE 8: Peak mobility of Ge (100) pMOSFETs in Zhang et al.'s work versus EOT, compared with the results reported so far [41–45].

FIGURE 9: Process flow of the OPO treatment on  $Al_2O_3/Ge$  gate stack [46].

FIGURE 10: C-V characteristics (1 MHz) of  $\text{Al}_2\text{O}_3/\text{Ge}$  MOScap improved significantly with the OPO treatment. The inset shows the reduction of EOT versus the OPO treatment time [46].

The EOT value of the MOS capacitor, extracted from the C-V characterizations, decreases from  $\sim$ 2.39 nm to  $\sim$ 1.79 nm, which may be attributed to the continuous improvement in the permittivity of the ALD-Al $_2$ O $_3$  film with the increase in the OPO time. After a careful process optimization with the OPO technology, sub-1 nm EOT and surface passivation could be achievable at the same time in Ge MOSFETs.

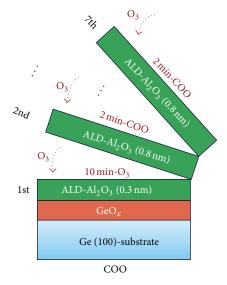

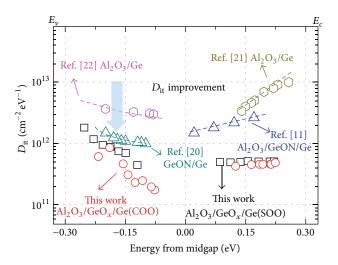

Just recently, Yang et al. have introduced the cycling ozone oxidation (COO) method into the ALD process to form a high quality  ${\rm Al_2O_3/GeO_x/Ge}$  stack [47]. Figure 13 shows the process flow of COO method used in their work. This COO method is proved to be effective in repairing the defects like OH-related groups to suppress the gate leakage current. The minimum  $D_{\rm it}$  value of  $1.9\times10^{11}~{\rm cm^{-2}eV^{-1}}$  is obtained by inserting  ${\rm GeO_x}$  passivation layer with the COO treatment, as shown in Figure 14 [47].

#### 3. Conclusion and Further Outlook

In order to realize high-mobility Ge CMOS device, different interface control and gate dielectric enhancement methods of Ge were systematically investigated. In this review, we have summarized and discussed various interface control technologies which are effective in obtaining high quality Ge MOSFETs. For reducing the interface state density and enhancing the mobility in Ge MOSFETs, the high-pressure oxidation, plasma postoxidation, and ozone postoxidation have been proven to be very effective based on the formation of good quality Ge oxide. For high-pressure oxidation and plasma postoxidation techniques, both of them can obtain a relatively low minimum value of  $D_{\rm it}$  in the order of  $10^{11}~{\rm cm}^{-2}{\rm eV}^{-1}$  even at a thin EOT of subnanometer [12, 38].

FIGURE 11: High-resolution cross-sectional transmission electron microscopy (HR-TEM) image of ALD-Al $_2$ O $_3$  on Ge structure: (a) without OPO treatment; (b) OPO treatment for 3 min; and (c) OPO treatment for 5 min [46].

FIGURE 12: (a) Ge 3d and (b) Al 2p XPS spectra of Al<sub>2</sub>O<sub>3</sub>/Ge structure before and after an OPO treatment [46].

FIGURE 13: Schematic of fabrication procedure of Ge MOS gate stacks for samples with cycling ozone oxidation (COO) treatment [47].

FIGURE 14: Energy distribution of  $D_{\rm it}$  of  ${\rm Al_2O_3/GeO_x/Ge~MOS}$  capacitors with cycling ozone oxidation (COO) and single ozone oxidation (SOO) treatments, in comparison with previously reported data by other groups [47].

For ozone postoxidation technique, a relatively low minimum value of  $D_{\rm it}$  of  $1.9\times10^{11}$  cm $^{-2}$  eV $^{-1}$  was also obtained under a relatively thick EOT (definite data not given in their report) [47]. Thus, these three techniques are all potential methods to improve the interfacial properties of Ge/dielectric gate stack in Ge MOSFETs.

It is noted that there are still several challenges for this Ge MOS interface passivation technique. The high-pressure oxidation technique has to be performed under a high pressure of ~70 atm, and thus its applicability to integrate with the current Si CMOS technology is still not clear. On the other hand, the plasma postoxidation technique is well approved in planar Ge MOSFETs. However, its applicability in 3D channel device, especially the gate-all-around (GAA) device, is not investigated yet. For ozone postoxidation, it is still desired to examine the scalability of Ge gate stacks. Due to the drawbacks or limits of each technique, further optimization is still needed to improve the mobility and to scale down the EOT in Ge MOSFETs. The compatibility with existing integrated circuit technology platform is also an important issue.

#### **Conflict of Interests**

The authors declare that there is no conflict of interests regarding the publication of this paper.

# Acknowledgments

This work was supported by the National Program on Key Basic Research Project (973 Program) of China (Grant no. 2011CBA00607), National Natural Science Foundation of China (Grants nos. 61106089 and 61376097), and the Zhejiang Provincial Natural Science Foundation of China (Grant no. LR14F040001).

#### References

- [1] K. Mistry, C. Allen, C. Auth et al., "A 45 nm logic technology with high-k<sup>+</sup>metal gate transistors, strained silicon, 9 Cu interconnect layers, 193 nm dry patterning, and 100% Pb-free packaging," in *Proceedings of the IEEE International Electron Devices Meeting (IEDM '07)*, Technical Digest, pp. 247–250, Washington, DC, USA, December 2007.

- [2] Y. Kamata, "High-k/Ge MOSFETs for future nanoelectronics," *Materials Today*, vol. 11, no. 1-2, pp. 30–38, 2008.

- [3] M. Bohr, "The evolution of scaling from the homogeneous era to the heterogeneous era," in *Proceedings of the IEEE International Electron Devices Meeting (IEDM '11)*, Technical Digest, pp. 1.1.1–1.1.6, Washington, DC, USA, 2011.

- [4] E. J. Nowak, "Advanced CMOS scaling and FinFET technology," ECS Transactions, vol. 50, no. 9, pp. 3–16, 2012.

- [5] K. J. Kuhn, "Considerations for ultimate CMOS scaling," *IEEE Transactions on Electron Devices*, vol. 59, no. 7, pp. 1813–1828, 2012.

- [6] S. Takagi, T. Mizun, T. Tezuka et al., "Channel structure design, fabrication and carrier transport properties of strained-Si/SiGe-On-Insulator (strained-SOI) MOSFETs," in *Proceedings of*

- the International Electron Devices Meeting (IEDM '03), Technical Digest, pp. 3.3.1–33.3.4, Washington, DC, USA, December 2003

- [7] K. Kita, K. Kyuno, and A. Toriumi, "Growth mechanism difference of sputtered HfO<sub>2</sub> on Ge and on Si," *Applied Physics Letters*, vol. 85, no. 1, pp. 52–54, 2004.

- [8] T. Krishnamohan, D. Kim, T. V. Dinh et al., "Comparison of (001), (110) and (111) uniaxial- and biaxial- strained-Ge and strained-Si PMOS DGFETs for all channel orientations: mobility enhancement, drive current, delay and off-state Leakage," in Proceedings of the IEEE International Electron Devices Meeting (IEDM '08), Technical Digest, pp. 899–892, San Francisco, Calif, USA, December 2008.

- [9] M. Caymax, G. Eneman, F. Bellenger et al., "Germanium for advanced CMOS anno 2009: a SWOT analysis," in *Proceedings* of the International Electron Devices Meeting (IEDM '09), Technical Digest, pp. 461–464, Baltimore, Md, USA, December 2009

- [10] R. Pillarisetty, B. Chu-Kung, S. Corcoran et al., "High mobility strained germanium quantum well field effect transistor as the P-channel device option for low power (Vcc = 0. 5 V) III-V CMOS architecture," in *Proceedings of the International Electron Devices Meeting (IEDM '10)*, Technical Digest, pp. 150–153, 2010.

- [11] C. H. Lee, T. Nishimura, T. Tabata et al., "Ge MOSFETs performance: impact of Ge interface passivation," in *Proceedings of* the International Electron Device Meeting (IEDM '10), Technical Digest, pp. 416–419, Washington, DC, USA, 2010.

- [12] R. Zhang, N. Taoka, P. Huang, M. Takenaka, and S. Takagi, "1-nm-thick EOT high mobility Ge n- and p-MOSFETs with ultrathin GeOx/Ge MOS interfaces fabricated by plasma post oxidation," in *Proceedings of the International Electron Devices Meeting (IEDM '11)*, Technical Digest, pp. 642–645, Washington, DC, USA, December 2011.

- [13] R. Zhang, P.-C. Huang, J.-C. Lin, M. Takenaka, and S. Takagi, "Physical mechanism determining Ge p- and n-MOSFETs mobility in high Ns region and mobility improvement by atomically Flat GeOx/Ge interfaces," in *Proceedings of the International Electron Devices Meeting (IEDM '12)*, Technical Digest, pp. 371–374, Washington, DC, USA, 2012.

- [14] B. Duriez, G. Vellianitis, M. J. H. van Dal et al., "Scaled p-channel Ge FinFET with optimized gate stack and record performance integrated on 300 mm Si wafers," in *Proceedings of the International Electron Devices Meeting (IEDM '13)*, Technical Digest, pp. 20.1.1–20.1.4, Washington, DC, USA, December 2013.

- [15] S. Takagi, T. Maeda, N. Taoka et al., "Gate dielectric formation and MIS interface characterization on Ge," *Microelectronic Engineering*, vol. 84, no. 9-10, pp. 2314–2319, 2007.

- [16] A. Toriumi, T. Tabata, C. Hyun Lee, T. Nishimura, K. Kita, and K. Nagashio, "Opportunities and challenges for Ge CMOS control of interfacing field on Ge is a key," *Microelectronic Engineering*, vol. 86, no. 7–9, pp. 1571–1576, 2009.

- [17] C. Lin, H. Chang, Y. Chen et al., "Interfacial layer-free  $\rm ZrO_2$  on Ge with 0.39-nm EOT,  $\kappa \sim 43$ ,  $\sim 2\times 10^{-3}$  A/cm² gate leakage, SS =85 mV/dec, Ion/Ioff =6×10<sup>5</sup>, and high strain response," in *Proceedings of the International Electron Devices Meeting (IEDM '12)*, Technical Digest, pp. 23.2.1–23.1.4, San Francisco, Calif, USA, December 2012.

- [18] Y. Fukuda, T. Ueno, S. Hirono, and S. Hashimoto, "Bend-mode liquid crystal cells stabilized by aligned polymer walls," *Japanese Journal of Applied Physics*, vol. 44, no. 2, p. 981, 2005.

- [19] T. Takahashi, T. Nishimura, L. Chen, S. Sakata, K. Kita, and A. Toriumi, "Proof of Ge-interfacing concepts for metal/highk/Ge CMOS, Ge-intimate material selection and interface conscious process flow," in *Proceedings of the International Electron Devices Meeting (IEDM '07)*, Technical Digest, pp. 697– 700, December 2007.

- [20] K. Kita, S. K. Wang, M. Yoshida et al., "Comprehensive study of GeO<sub>2</sub> oxidation, GeO desorption and GeO<sub>2</sub>-metal interaction. Understanding of Ge processing kinetics for perfect interface control," in *Proceedings of the International Electron Device Meeting (IEDM '09)*, Technical Digest, pp. 693–696, Baltimore, Md, USA, December 2009.

- [21] S. K. Wang, K. Kita, C. H. Lee et al., "Desorption kinetics of GeO from GeO<sub>2</sub>/Ge structure," *Journal of Applied Physics*, vol. 108, Article ID 054104, 2010.

- [22] S. K. Wang, K. Kita, T. Nishimura, K. Nagashio, and A. Toriumi, "Isotope tracing study of GeO desorption mechanism from GeO<sub>2</sub>/Ge stack using <sup>73</sup>Ge and <sup>18</sup>O," *Japanese Journal of Applied Physics*, vol. 50, Article ID 04DA01, 2011.

- [23] E. P. Gusev, D. A. Buchanan, E. Cartier et al., "Ultrathin high-K gate stacks for advanced CMOS devices," in *Proceedings of the International Electron Devices Meeting (IEDM '01)*, Technical Digest, pp. 451–454, December 2001.

- [24] C. Choi, C.-Y. Kang, S. J. Rhee et al., "Aggressively scaled ultrathin undoped HfO<sub>2</sub> gate dielectric (EOT < 0.7 nm) with tan gate electrode using engineered interface layer," *IEEE Electron Device Letters*, vol. 26, no. 7, pp. 454–457, 2005.

- [25] R. Puthenkovilakam, M. Sawkar, and J. P. Changa, "Electrical characteristics of postdeposition annealed HfO<sub>2</sub> on silicon," *Applied Physics Letters*, vol. 86, no. 20, Article ID 202902, 2005.

- [26] Y. Zhao, M. Toyama, K. Kita, K. Kyuno, and A. Toriumi, "Moisture-absorption-induced permittivity deterioration and surface roughness enhancement of lanthanum oxide films on silicon," *Applied Physics Letters*, vol. 88, no. 7, Article ID 072904, 2006.

- [27] Y. Zhao, K. Kita, K. Kyuno, and A. Toriumi, "Higher-k LaYO<sub>x</sub> films with strong moisture resistance," *Applied Physics Letters*, vol. 89, Article ID 252905, 2006.

- [28] Y. Zhao, K. Kita, K. Kyuno, and A. Toriumi, "Band gap enhancement and electrical properties of La<sub>2</sub>O<sub>3</sub> films doped with Y<sub>2</sub>O<sub>3</sub> as high-k gate insulators," *Applied Physics Letters*, vol. 94, no. 4, Article ID 042901, 3 pages, 2009.

- [29] Y. Zhao, K. Kita, K. Kyuno, and A. Toriumi, "Dielectric and electrical properties of amorphous  $La_{1-x}$   $Ta_x$   $O_y$  films as higher-k gate insulators," *Journal of Applied Physics*, vol. 105, no. 3, Article ID 034103, 2009.

- [30] Y. Zhao, "Design of higher-k and more stable rare earth oxides as gate dielectrics for advanced CMOS devices," *Materials*, vol. 5, no. 8, pp. 1413–1438, 2012.

- [31] H. Matsubara, T. Sasada, M. Takenaka, and S. Takagi, "Evidence of low interface trap density in GeO<sub>2</sub>/Ge metal-oxide-semiconductor structures fabricated by thermal oxidation," *Applied Physics Letters*, vol. 93, no. 3, Article ID 032104, 2008.

- [32] D. Kuzum, T. Krishnamohan, A. J. Pethe et al., "Ge-interface engineering with ozone oxidation for low interface-state density," *IEEE Electron Device Letters*, vol. 29, no. 4, pp. 328–330,

- [33] R. Zhang, T. Iwasaki, N. Taoka, M. Takenaka, and S. Takagi, "Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge gate stacks with low interface trap density fabricated by electron cyclotron resonance plasma postoxidation," Applied Physics Letters, vol. 98, no. 11, Article ID 112902, 2011.

- [34] C. H. Lee, T. Tabata, T. Nishimura, K. Nagashio, K. Kita, and A. Toriumi, "Ge/GeO<sub>2</sub> interface control with high-pressure oxidation for improving electrical characteristics," *Applied Physics Express*, vol. 2, no. 7, Article ID 071404, 2009.

- [35] C. H. Lee, T. Tabata, T. Nishimura, K. Nagashio, K. Kita, and A. Toriumi, "Ge/GeO<sub>2</sub> interface control with high pressure oxidation for improving electrical characteristics," ECS Transactions, vol. 19, no. 1, pp. 165–173, 2009.

- [36] T. Nishimura, C. H. Lee, T. Tabata et al., "High-electron-mobility Ge n-channel metal-oxide-semiconductor field-effect transistors with high-pressure oxidized Y<sub>2</sub>O<sub>3</sub>," *Applied Physics Express*, vol. 4, no. 6, Article ID 064201, 2011.

- [37] C. H. Lee, T. Nishimura, K. Nagashio, K. Kita, and A. Toriumi, "High-electron-mobility Ge/GeO2 n-MOSFETs with two-step oxidation," *IEEE Transactions on Electron Devices*, vol. 58, no. 5, pp. 1295–1301, 2011.

- [38] C. H. Lee, C. Lu, T. Tabata, T. Nishimura, K. Nagashio, and A. Toriumi, "Enhancement of high-Ns electron mobility in sub-nm EOT Ge n-MOSFETs," in *Proceedings of the Symposium on VLSI Technology Digest of Technical*, T29, p. T28, Kyoto, Japan, June 2013.

- [39] C. H. Lee, T. Nishimura, C. Lu, W. Zhang, K. Nagashio, and A. Toriumi, "Significant enhancement of high-N-s electron mobility in Ge n-MOSFETs with atomically flat Ge/GeO<sub>2</sub> interface," ECS Transactions, vol. 61, pp. 147–156, 2014.

- [40] S. Takagi, R. Zhang, and M. Takenaka, "Ge gate stacks based on Ge oxide interfacial layers and the impact on MOS device properties," *Microelectronic Engineering*, vol. 109, pp. 389–395, 2013.

- [41] R. Xie, T. H. Phung, W. He et al., "High mobility highπ/Ge pMOSFETs with 1nm EOT-new concept on interface engineering and interface characterization," in *Proceedings of the IEDM Technical Digest*, pp. 1–4, San Francisco, Calif, USA, 2008.

- [42] S.-S. Sheu, P.-C. Chiang, W.-P. Lin et al., "A 5ns fast write multi-level non-volatile 1Kb its RRAM memory with advance write scheme," in *Proceedings of the IEEE Symposium on VLSI Technology. Digest of Technical Papers*, pp. 82–83, 2009.

- [43] S.-S. Sheu, P.-C. Chiang, W.-P. Lin et al., "A 5ns fast write multi-level non-volatile 1Kbits RRAM memory with advance write scheme," in *Proceedings of the IEEE VLSI Symposium Technical Digest*, pp. 82–83, 2009.

- [44] Y. Kamata, A. Takashima, Y. Kamimuta, and T. Tezuka, "New approach to form EOT-scalable gate stack with strontium germanide interlayer for high-k/Ge MISFETs," in *Proceedings* of the IEEE Symposium on VLSI Technology. Digest of Technical Papers, pp. 78–79, 2009.

- [45] R. Zhang, P. C. Huang, N. Taoka, M. Takenaka, and S. Takagi, "High mobility Ge pMOSFETs with 0.7 nm ultrathin EOT using HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge gate stacks fabricated by plasma post oxidation," in *Proceedings of the Symposium on VLSI Technology* (VLSIT '12), pp. 161–162, June 2012.

- [46] J. Sun, Z. Yang, Y. Geng et al., "Equivalent oxide thickness scaling of Al<sub>2</sub>O<sub>3</sub>/Ge metal—oxide—semiconductor capacitors with ozone post oxidation," *Chinese Physics B*, vol. 22, no. 6, Article ID 067701, 2013.

- [47] X. Yang, S. Wang, X. Zhang et al., "Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub> gate stack on germanium substrate fabricated by in situ cycling ozone oxidation method," *Applied Physics Letters*, vol. 105, no. 9, Article ID 092101, 2014.

- [48] Y. Fukuda, Y. Yazaki, Y. Otani, T. Sato, H. Toyota, and T. Ono, "Low-temperature formation of high-quality GeO<sub>2</sub> interlayer

- for high- $\kappa$  gate dielectrics/Ge by electron-cyclotron-resonance plasma techniques," *IEEE Transactions on Electron Devices*, vol. 57, no. 1, pp. 282–287, 2010.

- [49] Q. Xie, D. Deduytsche, M. Schaekers et al., "Effective electrical passivation of Ge(100) for  $HfO_2$  gate dielectric layers using  $O_2$  plasma," *Electrochemical and Solid-State Letters*, vol. 14, no. 5, pp. G20–G22, 2011.

- [50] D. Kuzum, T. Krishnamohan, A. Nainani et al., "Experimental demonstration of high mobility Ge NMOS," in *Proceedings of the International Electron Devices Meeting (IEDM '09)*, Technical Digest, pp. 1–4, Baltimore, Md, USA, December 2009.

Submit your manuscripts at http://www.hindawi.com