Hindawi Advances in Condensed Matter Physics Volume 2017, Article ID 7820676, 8 pages https://doi.org/10.1155/2017/7820676

# Research Article

# Fast Switching 4*H*-SiC *P-i-n* Structures Fabricated by Low Temperature Diffusion of Al

# I. G. Atabaev, Kh. N. Juraev, and V. A. Pak

Physical-Technical Institute, Scientific Association "Physics-Sun", Uzbek Academy of Sciences, Bodomzor Street 2B, 100084 Tashkent, Uzbekistan

Correspondence should be addressed to Kh. N. Juraev; khimmatali@gmail.com

Received 12 January 2017; Revised 30 March 2017; Accepted 3 May 2017; Published 30 May 2017

Academic Editor: Jörg Fink

Copyright © 2017 I. G. Atabaev et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

P-i-n 4H-SiC $\langle$ Al $\rangle$  diode structures are fabricated by a new approach which is low temperature diffusion of aluminium (Al) in SiC using flow of vacancy defects from surface into volume of crystal. In conventional diffusion in SiC, the operating temperature is usually >2050°C while, in this approach, the diffusion temperature is between 1150 and 1300°C. As the conditions of formation of junction in this method essentially differ from conventional diffusion (low temperature and process of diffusion are accompanied by forming structure defects), it is interesting to identify the advantages and disadvantages of a new method of diffusion. Fabricated p-i-n structures have low breakdown voltage between 80 and 140 V (due to the influence of dislocations and micropipes) and are capable of operating at temperatures up to 300°C. Structure has fast switching time and duration of the reverse recovery current less than 10 ns. We believe that because of low diffusion temperature, the concentration of nitrogen related trapping levels is relatively low and as a result the fast switching time is observed in our samples. It has been shown that this low temperature diffusion technology can be used to fabricate p-region and high resistive i-region of SiC diode in single-step process.

# 1. Introduction

Silicon carbide (SiC) has some unique properties which improve the performance of the SiC based devices and provide a number of advantages over devices made of traditional semiconductor materials such as silicon and gallium arsenide. One of these advantages is the high thermal stability of SiC made devices [1, 2] which makes it suitable for power and extreme electronics [3].

An important characteristic of SiC diodes for power and pulse techniques is the switching time ( $\tau$ ) of diodes which is usually >20 ns for a diode with an area of  $100 \times 100 \ \mu \text{m}^2$  [4]. This switching time is probably related to a trapping level in SiC material. It has been found that the base region of SiC diodes doped with aluminium has a deep trapping level with an ionization energy ~1.45 eV and trapping level ~0.16 eV which is due to nitrogen impurity [2]. Capture processes and thermal activation of electrons associated with these levels can greatly increase the duration of the relaxation of current through the p-n junction.

Currently, power diodes made of silicon carbide using diffusion technology have a breakdown voltage ~700 V for

4H polytype [5] and ~1000 V for 6H polytype [6]. The most important steps in manufacturing silicon carbide based devices are the formation of p-n-junctions and fabrication of low-resistance ohmic contacts.

Previously it has been shown that to fabricate diodes with high breakdown voltage, highly resistive i-region of p-i-n SiC diodes needs to be created by epitaxial growth of thin SiC layer (free from micropipe defects) [7, 8]. Afterwards (second technological step), p-region of p-i-n SiC diodes is formed by thermal diffusion at a temperature >2050°C or ion implantation of SiC by aluminium [4, 9]. It is worth mentioning that heavily doped SiC crystal fabricated by ion implantation (with concentration of impurities up to  $10^{19}$  cm $^{-3}$ ) should be annealed at a temperature ~1800°C to remove the defects [10, 11]. Extremely high temperature processing (>2050°C) needed during thermal diffusion [12–14] or after ion implantation [10, 11] may increase the production cost.

Thus epitaxy and ion implantation have gained popularity to fabricate concurrent SiC based devices. And conventional thermal diffusion of impurity is regarded as old and unstable technology for fabrication of p-n junction on the base of SiC.

In this article we report on properties of *p-i-n* structures fabricated by low temperature diffusion of aluminium (Al) in SiC using flow of defects (silicon and carbon vacancies) from surface into volume of crystal. In conventional diffusion in SiC, operating temperature is usually >2050°C while in our developed method the diffusion temperature is between 1150 and 1300°C. As the conditions of formation of junction in this method essentially differ from conventional diffusion (low temperature and process of diffusion are accompanied by formation of structure defects) it is interesting to identify the advantages and disadvantages of a new method of diffusion

#### 2. Materials and Methods

*P-i-n* diodes are fabricated on the basis of single crystal samples of silicon carbide 4*H-n-*SiC grown by the Physical Vapour Transport (PVT) method (Cree Research, Inc, USA) with a relatively low concentration of growth defects:  $N_d$  dislocations  $10^4$  cm<sup>-2</sup> and  $N_m$  micropipes ~ $10^{-10^2}$  cm<sup>-2</sup>, thickness ~ $300^{-600}$  μm, surface ~0.25 cm<sup>2</sup> and specific resistance ~ $3.6^{-20}$  Ω·cm, and nitrogen impurity concentration ~ $(0.5^{-1.0}) \times 10^{17}$  cm<sup>-3</sup>.

Etching of samples is performed in KOH–water solution upon stimulation by ultraviolet (UV) light. Unlike reactive ion etching the UV light stimulated etching does not create defects and allows fabricating a smooth surface [16, 17].

After the removal of the surface layer, the low temperature diffusion of aluminium is carried out. This diffusion in 4H-SiC is performed at different temperatures ranging between 1150 and 1300°C during 30 min by our new method patented in USA and Uzbekistan and described in detail [17–26]. Below some information about new method of diffusion is given briefly. Well known diffusions of impurities in SiC are carried out via Si- and C-vacancies and the solubility of impurity and diffusion coefficient in SiC are different in Si and C - sublattice [13]. In our method the diffusion process is carried out in air atmosphere in condition of surface oxidation to create a flow of vacancies of Si and C from the crystal surface into the bulk of the sample [17]. Increasing vacancy concentration increases the diffusion constant and solubility of impurity up to  $10^{20} \, \text{cm}^{-3}$  [20–22]. Temperature of diffusion in this method is between 1150 and 1300°C which is lower compared to the conventional diffusion process (more 2000°C). Thus low disintegration of SiC surface is expected.

The source of impurity of aluminium atoms for diffusion is formed by two ways: (1) thin pure aluminium film is thermally evaporated onto the sample in Vacuum Universal Post VUP-4 (10<sup>-6</sup> Torr.). (2) The aluminium chloride thin film is created on the surface of sample using the saturated solution of aluminium chloride in methanol. The sample is then heated in the air up to 650°C for 30 min, which leads to the formation of an Al and Si oxides glass layer on the surface. Afterwards the sample is annealed in the air during 30 min in the diffusion furnace at a temperature ranging between 1150°C and 1300°C. In these conditions of surface oxidation from the surface of SiC the SiO and CO molecules are evaporated and flow of vacancies is created from the surface into volume of crystal. After the sample is cooled to

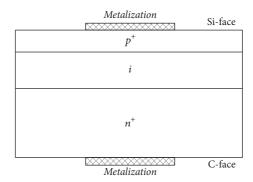

FIGURE 1: Schematic diode structures of *p-i-n* 4*H*-SiC $\langle$ Al $\rangle$  diode.

room temperature, it is immersed in buffered oxide etch to remove the top oxide layer [18–20].

As a first assumption it is presumed that the diffusion of aluminium goes via carbon and silicon vacancies like conventional mechanism diffusion in SiC and differs only by increased concentration of vacancies. Of course, the real mechanism of aluminium diffusion in our case can differ from conventional mechanism of diffusion via C- and Sivacancies. It is clear that increased concentration of vacancies near the surface of the crystal leads to SiC lattice distortion. Other factors can also influence the diffusion process; for example, the formation of nanopores or new defects can influence the diffusion of aluminium. But in this presented article the diffusion mechanisms are not investigated as for this study additional experiments and thorough analysis are required. Our approach is based on an obvious fact that the increased concentration of silicon and carbon vacancies leads to low temperature diffusion.

Further study shows that during diffusion process vacancies of Si and C penetrate into volume deeper than doping impurity and lead to the formation of i-region simultaneously with the formation of p-region. So in one processing step both the p- and i-regions can be formed. The i-region is created (compensated) by deep level defects related to Si- and C-vacancies.

Type of conductivity of doped layers and silicon carbide single crystals was tested by hot probe (thermoprobe) method [27]. Impurity concentration was measured using standard capacitance-voltage (C-V) measurements [28]. Impedance measurements were carried out at different frequencies with the amplitude of the alternating current (AC) signal kept constant at 20 mV, while the researched structure was under applied direct current (DC) bias. Switching time of 4H-SiC $\langle$ Al $\rangle$  diode structures was measured on a special pulse stand [29].

#### 3. Results

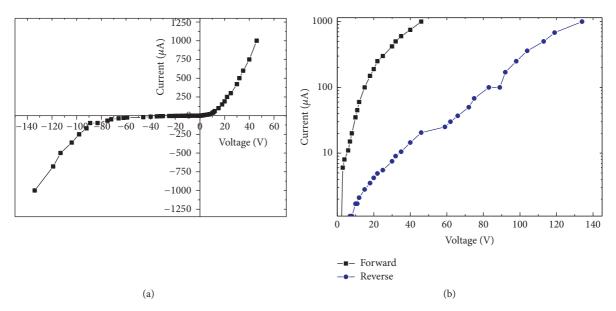

Schematic structure of the fabricated SiC diode and its current-voltage (I-V) characteristics of p-n 4H-SiC $\langle$ Al $\rangle$  junction (area of p-n-junction  $\sim$  6 mm²) are shown in Figures 1 and 2, respectively. Figure 2 shows that the diode has a breakdown voltage between 80 and 140 V which is significantly low

FIGURE 2: I-V characteristic of p-i-n 4H-SiC $\langle$ Al $\rangle$  junction, in the (a) linear and (b) semilog scale.

compared to the results reported elsewhere (>600 V, 1.2 kV, and 1.7 kV) [30, 31]. It is well known that the breakdown voltage in SiC structures is greatly reduced in the presence of such defects like micropipes, screw dislocations, stacking faults, and so on. The largest breakdown voltages are achieved in SiC/SiC structures with epitaxial layers without micropipes and with a low concentration of dislocations [7, 8].

In our structures low value of breakdown voltage is mainly due to the influence of dislocations ( $N_d \sim 10^4 \, {\rm cm}^{-2}$ ) and micropipes ( $N_m \sim 10$ – $10^2 \, {\rm cm}^{-2}$ ) in used SiC crystals. It has been reported previously [32] that with a screw dislocation concentration of ~ $10^4 \, {\rm cm}^{-2}$  the maximum breakdown voltage ( $V_b$ ) of samples with diameter 300–500  $\mu$ m between 350 and 400 V can be reached. For our samples with area 4000 × 4000  $\mu$ m the breakdown voltage was ~140– $160 \, {\rm V}$ .

This breakdown voltage can be improved in several ways, for example, by improving low temperature diffusion technology, by the formation of mesa-structure, and by surface passivation. But to get a significantly high breakdown voltage up to 1-2 kV like Cree Inc. [33], it is necessary to use SiC crystal free from micropipes and with lower concentration of dislocations.

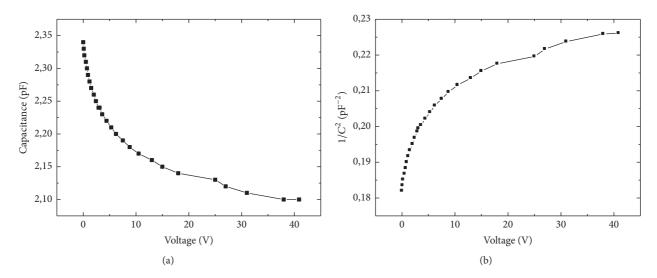

An increasing of direct current is observed at voltages higher than 10 V, which indicates the presence of a high-resistance layer between the *p*-region and *n*-region. This is also confirmed by C-V measurements at 1 MHz. For the applied reverse voltage, capacitance is ~2.2 pF (Figure 3) and the series resistance is ~70 k $\Omega$ .

Thickness of *p-i-n* junction (W) is found to be  $W(V = 0) \sim 12 \,\mu\text{m}$  using [28]

$$C = \frac{\varepsilon \varepsilon_0 S}{W},\tag{1}$$

where C is capacitance of the diode,  $\varepsilon$  is dielectric constant of the silicon carbide,  $\varepsilon_0$  is electric constant, S is layer area, and W is thickness of the depletion layer.

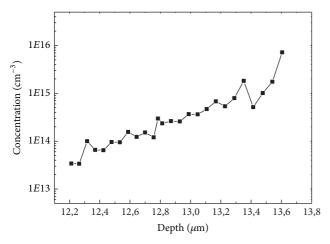

Figure 4 shows the distribution of impurities in the i-layer, determined from dependence of the C(V) characteristics. This figure shows that the depletion region spreads from 12.2  $\mu$ m at  $V_r=0$  up to 13.7  $\mu$ m for  $V_r=40$  V. So the thickness of i-region is about 1.5–2  $\mu$ m.

The high-resistance region is caused by defects, which is probably introduced during the diffusion and it has inhomogeneous distribution of the carrier density. According to Figure 4 the carrier concentration at the interface of the junction and a high-resistance n-layer increase from  $10^{13}$  to  $5 \times 10^{16}$  cm<sup>-3</sup> (impurity concentration in the substrate of silicon carbide).

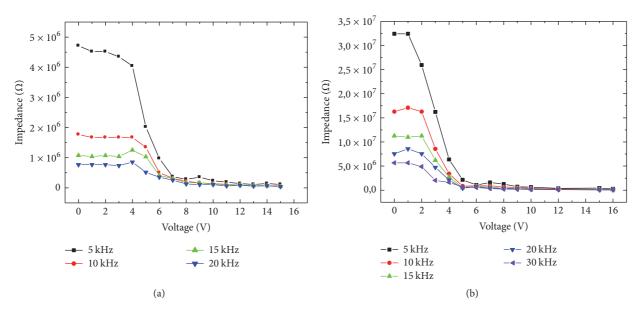

To further study the fabricated diode, impedance measurements at relatively low frequencies 5000, 10000, 15000, and 20000 Hz (see Figure 5) were carried out to evaluate the capacitance, series resistance, and other parameters of structure.

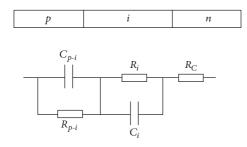

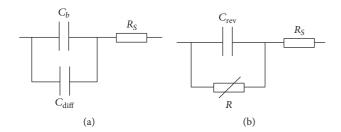

Assuming the parameters of the structures do not change in this frequency range, on the base of the equivalent circuit it is possible to evaluate the capacitance and the series resistance of structure. Figure 6 shows the equivalent circuit of our structure which is created based on the equivalent circuit of p-i-n diode reported in [15]. According to the work done in [15],  $L_s$  inductance has to be added in equivalent circuit. But in our case,  $L_s$  can be neglected as this small parasitic element has little effect on p-i-n diode performance below 1 MHz.

According to [15] the simplified equivalent circuit of *p-i-n* junction at direct applied bias consists of diffusion capacity (which is parallel to barrier capacitance) and series resistance (Figure 7(a)). And simplified equivalent circuit for the *p-i-n* junction for reverse applied bias consists of barrier capacitance and parallel and series resistances (Figure 7(b)) [15].

If we assume that at constant applied voltage, resistance and capacitance of the junctions do not change or slightly change with frequency, the module of impedance of the above equivalent circuits can be considered.

FIGURE 3: The dependence of capacitance (a) and the value  $1/C^2$  (b) for one of the diodes under reverse voltages measured at 1 MHz.

FIGURE 4: The distribution of aluminium concentration versus W(V) according to C-V data in high-resistance layer of the sample 4H-SiC $\langle AI \rangle$ .

For direct bias  $C_{\rm dif}$  and  $C_b$  are parallel ( $C = C_{\rm dif} + C_b$ ) and with serial resistance  $R_s$  have the total impedance

$$Z = R_{S} + \frac{1}{iwC},\tag{2}$$

where jwC is capacitance conductivity ( $j = \sqrt{-1}$  means that capacitance changes the phase of AC) and  $w = 2\pi v$  is angular frequency. Module of total impedance for direct bias is

$$Z = \left(R_S^2 + \frac{1}{(wC)^2}\right)^{1/2}.$$

(3)

Let us consider case of reverse bias.

The conductivity of parallel connected  $C_{rev}$  and R is

$$\Sigma = jwC + \frac{1}{R} = \frac{1 + jwCR}{R} \tag{4}$$

and total impedance for reverse bias is

$$Z = \frac{R}{1 + jwCR} + R_{S}. (5)$$

Let us transform this expression to the canonical form (using multiplication on conjugate expression)

$$Z = \frac{R(1 - jwCR)}{(1 + jwCR)(1 - jwCR)} + R_{S},$$

$$Z = \left(R_{S} + \frac{R}{(1 + w^{2}C^{2}R^{2})}\right) - \frac{jwCR}{(1 + w^{2}C^{2}R^{2})}.$$

(6)

Module of this impedance is

$$Z = \left[ \left( R_S + \frac{R}{\left( 1 + (wCR)^2 \right)} \right)^2 + \left( \frac{wCR^2}{\left( 1 + (wCR)^2 \right)} \right)^2 \right]^{1/2}.$$

$$(7)$$

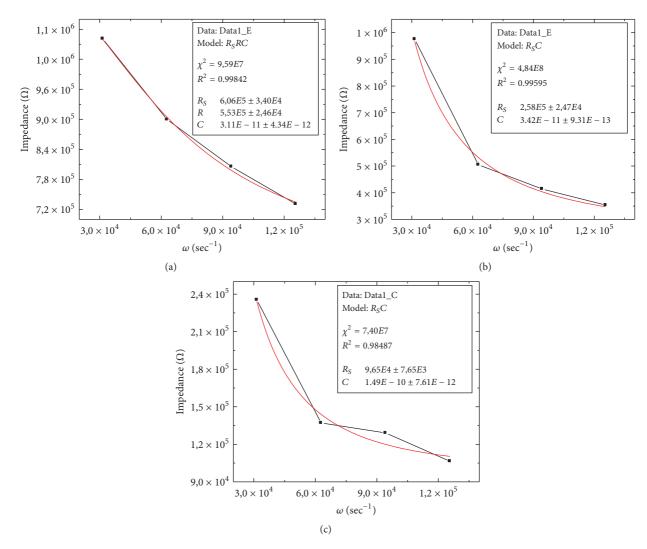

The computer fitting of expression (3) (Figure 7(a)) and (7) (Figure 7(b)) to experimental data was performed using Origin 60 which is shown in Figure 8.

At direct connection, the forward capacitance increases from  $34\,pF$  at  $6\,V$  to  $276\,pF$  at  $12\,V$  and series resistance decreases from  $260\,k\Omega$  at  $6\,V$  to  $80\,k\Omega$  at  $12\,V$ .

Lifetime of the minority carriers is found to be ~7 ns using

$$C_D = \frac{\tau_p J}{kT/q},\tag{8}$$

where  $\tau_p$  is the minority carrier lifetime, J is a forward current through the diode, k is Boltzmann constant, T is the temperature, and q is electron charge.

FIGURE 5: Impedance of the diode structure at different frequencies at direct (a) and reverse (b) bias (●: 5 kHz, ▲: 10 kHz, ▼: 15 kHz, ■: 20 kHz, ◄: 30 kHz).

FIGURE 6: Equivalent circuit diagram of p-n junction with the intermediate layer of high resistance, constructed on the basis of an equivalent circuit of p-i-n diode [15].

FIGURE 7: Simplified equivalent circuit of *p-i-n* junction for direct connection (a) and reverse connection (b).

Forward biased p-i-n diode is a Current Controlled Resistor [29] and relationship between  $R_S$  and  $I_f$  can be described using

$$R_{S} = \frac{W^{2}}{I_{f}\tau\left(\mu_{n} + \mu_{p}\right)},\tag{9}$$

where  $I_f$  is forward bias current,  $\tau$  is minority carrier lifetime, and  $\mu_n$ ,  $\mu_p$  are electron and hole mobility, respectively.

For perfect SiC single crystal,  $(\mu_n + \mu_p) \sim 1000 \text{ cm}^2/(\text{V} \cdot \text{s})$  [34]. If *i*-region has a thickness  $\sim 2 \, \mu \text{m}$ , minority carrier lifetime will be  $\sim 0.1 \, \text{ns}$  from (9). For SiC material with micropipes and dislocations and concentration of electrons  $\sim 10^{17} \, \text{cm}^{-3}$  the sum  $(\mu_n + \mu_p)$  is  $\sim 400 - 500 \, \text{cm}^2/(\text{V} \cdot \text{s})$  [35]. Thus in *i*-region the minority carrier lifetime is  $\sim 0.20 - 0.3 \, \text{ns}$ .

It is necessary to mention here that the (1) and (3) will not remain exactly the same as it is now because under various applied voltages, fitting parameter  $R_S$  will change (because it includes the series resistance of contacts and resistance of *i*-region which is often nonlinear in SiC devices). It should be also noted that at least 20 data points need to be used for fitting. For our study, measurements are performed in four frequencies only, which is why the values we have obtained are just estimations.

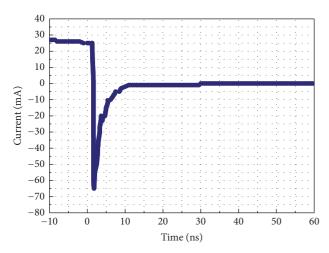

The current waveform of 4H-SiC $\langle$ Al $\rangle$  diodes was measured at room temperatures and shown in Figure 9. The switching of diodes from forward current ( $I=0.25\,\mathrm{mA}$ ) to reverse voltage 60 V is measured. As seen from Figure 9, the diodes have very fast switching time and duration of the reverse recovery current (of the order of 5–7 ns) for junctions with an area of approximately 6 mm². Obtained experimental data do not contradict above stated estimations of minority carrier lifetime.

Literature suggests switching time ( $\tau$ ) > 20 ns can be obtained for a diode with an area of  $100\,\mu\mathrm{m} \times 100\,\mu\mathrm{m}$  in laboratory [4]. In the catalogue of Toshiba, reverse recovery time for SiC Schottky commercial diodes is ~40 ns [36]. The reverse recovery characteristics of a 4*H*-SiC *p-i-n* diode under higher voltage and faster switching are investigated elsewhere [37] where it is shown that at a room temperature  $\tau$  is ~80 ns.

Now we will further investigate the origin of fast switching time. If we assume that junction process is determined only by electrical capacitance of the junction (capacitive

FIGURE 8: Results of fitting of expressions (2, 3) to experimental data: (a) reverse applied voltage 6 V; (b) direct applied voltage 6 V; (c) direct applied voltage 10 V.

processes) and resistivity the relaxation time  $t_r = RC$  (R is series resistance and C is capacity of the junction) then the relaxation time should be  $\sim 10^{-10}$  s. However, as it is shown earlier [2], junction processes involve nonequilibrium carriers in silicon carbide determined by trapping level ( $EK_2$  with energy  $E_c \sim 0.16\,\mathrm{eV}$ ). This trap level is ascribed to the donor impurity of nitrogen and the observed concentration profile in silicon carbide diode associated with the diffusion of nitrogen as background impurities [2]. The diffusion temperature in our technology is  $1150-1300\,^{\circ}\mathrm{C}$ , significantly lower than the conventional diffusion temperature which is  $\sim 2000-2200\,^{\circ}\mathrm{C}$ . Because of this low diffusion temperature, the concentration of trapping levels due to nitrogen is relatively low and as a result the fast switching time is observed in our samples.

Measurement of the *I-V* characteristics at different temperatures has also been performed. In reverse branch of the *I-V* characteristic, we have not seen any sharp electrical breakdown and reverse current of 100 mA was considered

to be the beginning of electrical breakdown. With increasing temperature up to 300°C the breakdown voltage has decreased down to 15 V. Thus the fabricated SiC diodes keep their rectifying properties up to 300°C.

The fabricated SiC diodes with relatively low breakdown voltage of ~150 V and fast switching time less 10 ns have the prospect of being used in application devices like mobile phones, DSC, lighting, Notebook PCs, HDD, PPC, power supplies for communication devices, and so on [38, 39].

## 4. Conclusions

*P-i-n* 4*H* SiC⟨Al⟩ diodes are fabricated by low temperature diffusion of Al in SiC by using flow of Si, C-vacancies from surface into volume of crystal. In this method the diffusion temperature is about 1150–1300°C, lower than conventional diffusion temperature (>2050°C). Fabricated *p-i-n* structure have low breakdown voltage between 80 and 140 V (due to the influence of dislocations and micropipes) and are capable

FIGURE 9: Oscillogram of the current of 4H-SiC $\langle$ Al $\rangle$  diode measured at switching from the forward current ( $I=25\,\text{mA}$ ) to a reverse voltage of 60 V.

of operating at temperatures up to  $300^{\circ}$  C. Structure has fast switching time and duration of the reverse recovery current less than 10 ns. It has been shown that this low temperature diffusion technology can be used to fabricate p-region and high resistive i-region of SiC diode in single-step process.

## **Conflicts of Interest**

The authors declare that they have no conflicts of interest.

# Acknowledgments

The authors would like to thank Farsad Imtiaz Chowdhury and Ulug'bek Abdurakhmanov for assisting during the proof-reading of the manuscript.

#### References

- A. A. Lebedev, N. S. Savkina, A. M. Ivanov, N. B. Strokan, and D. V. Davydov, "6H-SiC epilayers as nuclear particle detectors," *Semiconductors*, vol. 34, no. 2, pp. 243–249, 2000.

- [2] N. I. Kuznetsov and J. A. Edmond, "Effect of deep levels on current excitation in 6H-SiC diodes," *Semiconductors*, vol. 31, no. 10, pp. 1049–1052, 1997.

- [3] J. Rogowski and A. Kubiak, "Effects of annealing temperature on the structure and electrical properties of tungsten contacts to n-type silicon carbide," *Materials Science and Engineering B: Solid-State Materials for Advanced Technology*, vol. 191, no. C, pp. 57–65, 2015.

- [4] P. G. Neudeck and C. Fazi, "Nanosecond risetime pulse characterization of SiC p+n junction diode breakdown and switching properties," *Materials Science Forum*, vol. 264-268, no. 2, pp. 1037–1040, 1998.

- [5] Y. Gao, S. Soloviev, and T. Sudarshan, "Planar 4H- and 6H-SiC p-n diodes fabricated by selective diffusion of boron," *Solid-State Electronics*, vol. 45, no. 12, pp. 1987–1990, 2001.

- [6] S. Soloviev, Y. Gao, X. Wang, and T. Sudarshan, "Boron diffusion into 6H-SiC through graphite mask," *Journal of Electronic Materials*, vol. 30, no. 3, pp. 224–227, 2001.

- [7] P.-A. Nilsson, Method for Producing a Pn-Junction for a Semiconductor Device of SiC, US Patent, 2000.

- [8] R. V. Ryzhuk, N. I. Kargin, V. A. Gudkov, A. S. Gusev, and S. M. Ryndja, "Method to make high voltage silicon-carbide diode based on ion-doped p-n-structures," *RU Patent*, Article ID 2528554, 2014.

- [9] P. A. Ivanov, M. E. Levinshtein, T. T. Mnatsakanov, J. W. Palmour, and A. K. Agarwal, "Power bipolar devices based on silicon carbide," *Semiconductors*, vol. 39, no. 8, pp. 861–877, 2005.

- [10] E. V. Kalinina, V. G. Kossov, R. R. Yafaev, A. M. Strelchuk, and G. N. Violina, "A high-temperature radiation-resistant rectifier based on p\*-n junctions in 4H-SiC ion-implanted with aluminum," *Semiconductors*, vol. 44, no. 6, pp. 778–788, 2010.

- [11] J. Pernot, J. Camassel, S. Contreras et al., "Control of Alimplantation doping in 4H-SiC," *Materials Science and Engineering B: Solid-State Materials for Advanced Technology*, vol. 80, no. 1–3, pp. 362–365, 2001.

- [12] M. G. Mynbaeva, E. N. Mokhov, A. A. Lavrent'ev, and K. D. Mynbaev, "High-temperature diffusion doping of porous silicon carbide," *Technical Physics Letters*, vol. 34, no. 9, pp. 731–733, 2008.

- [13] Y. Gao, S. I. Soloviev, and T. S. Sudarshan, "Selective doping of 4H-SiC by codiffusion of aluminum and boron," *Applied Physics Letters*, vol. 83, pp. 905–907, 2003.

- [14] A. Kubiak and J. Rogowski, "Boron and aluminum diffusion into 4H–SiC substrates," *Materials Science and Engineering: B*, vol. 176, no. 4, pp. 297–300, 2011.

- [15] W. E. Doherty and R. D. Joos, *The pin diode circuit designers handbook*, Microsemi Corporation, Watertown MA, 1998.

- [16] I. G. Atabaev, V. A. Pak, B. G. Atabaev, and Kh. N. Juraev, "Etching of SiC in Potassium Hydroxide Solution (KOH), stimulate by UV Radiation," *Uzbek Journal of Physics*, vol. 13, no. 2, pp. 137–139, 2011.

- [17] I. G. Atabaev, T. M. Saliev, D. Saidov et al., "Influence of defects on low temperature diffusion of boron in SiC," *Materials Sciences and Applications*, vol. 02, no. 09, pp. 1205–1211, 2011.

- [18] I. G. Atabaev, T. M. Saliev, and E. N. Bakhranov, "Method of Diffusion of Boron in Silicon Carbide , UZ Patent," *IAP 02792*, 2006.

- [19] C. C. Tin, A. V. Adedeji, I. G. Atabayev et al., *Low temperature impurity doping of silicon carbide*, US Patent, 2011.

- [20] I. G. Atabaev, T. M. Saliev, E. N. Bakhranov et al., "Nonequilibrium diffusion of boron in SiC at low temperatures," *Materials Sciences and Applications*, vol. 01, no. 02, pp. 53–58, 2010.

- [21] I. G. Atabaev, C. C. Tin, B. G. Atabaev et al., "Diffusion and electroluminescence studies of low temperature diffusion of boron in 3C-SiC," *Materials Science Forum*, vol. 600-603, pp. 457–460, 2009.

- [22] C.-C. Tin, S. Mendis, M. T. Tin, T. I. Smith, and J. R. Williams, "A new approach in impurity doping of 4H-SiC using silicidation," *Journal of Applied Physics*, vol. 114, no. 24, Article ID 244502, 2013.

- [23] C. C. Tin, S. Mendis, K. Chew et al., "Oxide film assisted dopant diffusion in silicon carbide," *Thin Solid Films*, vol. 518, no. 24, pp. 118–120, 2010.

- [24] S. Mendis, C. C. Tin, I. G. Atabaev, and B. G. Atabaev, "The Method of Solid State Impurity Diffusion and Doping In 4H-SiC," *International Journal of Fundamental Physical Sciences*, vol. 3, pp. 75–78, 2013.

- [25] S. P. Mendis and C. C. Tin, "Phosphorus oxide assisted n-type dopant diffusion in 4H-Silicon Carbide," Materials Research Society Symposium Proceedings, vol. 1246, pp. B07–B12, 2010.

- [26] I. G. Atabaev, T. M. Saliev, B. G. Atabaev, and R. Jabbarganov, ""Negative secondary ion mass spectra under Cs+ ion bombardment of the p-SiC-B-surface," *Journal of Surface Investigation. X-ray, Synchrotron and Neutron Techniques*, vol. 5, no. 4, pp. 796–800, 2011.

- [27] D. K. Schroder, Semiconductor Material and Device Characterization, John Wiley & Sons, Inc., New York, NY, USA, 3rd edition, 2006.

- [28] S. M. Sze, Physics of Semiconductor Devices, Wiley, New York, NY, USA, 2nd edition, 1981.

- [29] J. D. Irwin, The Industrial Electronics Handbook, CRC Press, 2nd edition, 2011.

- [30] K. Nakayama, R. Ishii, K. Asano, T. Miyazawa, M. Ito, and H. Tsuchida, "Component technologies for ultra-high-voltage 4H-SiC pin diode," *Materials Science Forum*, vol. 679-680, pp. 535–538, 2011.

- [31] V. D'Alessandro, A. Irace, G. Breglio et al., "Influence of layout geometries on the behavior of 4H-SiC 600V Merged PiN Schottky (MPS) rectifiers," in *Proceedings of 18th International* Symposium on Power Semiconductor Devices and ICs, ISPSD'06, pp. 1–4, Naples, Italy, 2006.

- [32] Q. Wahab, A. Ellison, A. Henry et al., "Influence of epitaxial growth and substrate-induced defects on the breakdown of 4H-SiC Schottky diodes," *Applied Physics Letters*, vol. 76, no. 19, pp. 2725–2727, 2000.

- [33] Cree Inc., "Cree Expands Product Offering with Very Low Basal Plane Dislocation 4H Silicon Carbide Epitaxial Wafers, (04 Sep 2012)".

- [34] F. Henry, P. Marti, Y. Casaux, C. Combescure, A. Figueras et al., "LPCVD of SiC layers in a hot-wall reactor using TMS precursor," *Journal de Physique IV Colloque*, vol. 3, pp. 329–336, 1003

- [35] T. T. Mnatsakanov, L. I. Pomortseva, and S. N. Yurkov, "A semiempirical model in analyzing the charge carrier mobility dependence on temperature and doping in silicon carbide," *Semiconductors*, vol. 35, no. 4, pp. 394–397, 2001.

- [36] Toshiba, SiC Schottky Barrier Diodes, (Semiconductor Catalog, Sep 2014), http://toshiba.semicon-storage.com.

- [37] K. Nakayama, S. Ogata, T. Hayashi et al., "High voltage and fast switching reverse recovery characteristics of 4H-SiC PiN diode," *Materials Science Forum*, vol. 778-780, pp. 841–844, 2014.

- [38] T. Kimoto, "Material science and device physics in SiC technology for high-voltage power devices," *Japanese Journal of Applied Physics*, vol. 54, no. 4, article 040103, 2015.

- [39] M. Bakowski, "Roadmap for SiC power devices," Journal of Telecommunications and Information Technology, vol. 3-4, pp. 19–30, 2000.

Submit your manuscripts at https://www.hindawi.com