# Research Article Realization of DVCCTA Based Versatile Modulator

## Neeta Pandey,<sup>1</sup> Rajeshwari Pandey,<sup>1</sup> Aseem Sayal,<sup>2</sup> and Manan Tripathi<sup>2</sup>

<sup>1</sup> Department of Electronics & Communication Engineering, Delhi Technological University, Delhi 110042, India <sup>2</sup> Department of Electrical Engineering, Delhi Technological University, Delhi 110042, India

Correspondence should be addressed to Neeta Pandey; n66pandey@rediffmail.com

Received 31 May 2014; Accepted 7 October 2014; Published 27 October 2014

Academic Editor: Stephan Gift

Copyright © 2014 Neeta Pandey et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

A Differential Voltage Current Conveyor Transconductance Amplifier (DVCCTA) based versatile modulator is proposed which can work as an amplitude modulator, frequency modulator, delta modulator, and sigma delta modulator. The modulator operational scheme uses pulse generator as a core and its output is used as carrier signal. A DVCCTA based pulse generator is proposed first and subsequently configured as different modulators. Compact realization is the key feature of the proposed circuit as it uses two DVCCTA; a grounded resistor and a grounded capacitor hence are appropriate for IC realization. The functionality of the proposed circuit is verified through SPICE simulations using TSMC 0.25  $\mu$ m CMOS process model parameters. The performance parameters such as power dissipation and noise for various modulator schemes are also obtained.

## **1. Introduction**

Modulation is a process of modifying some characteristic of a carrier signal according to the instantaneous value of modulating signal and is a fundamental requirement of any communication system. Analog and digital modulations are two representative classes of modulation techniques. Amplitude and frequency modulation fall under analog modulation schemes wherein amplitude and frequency of the carrier signal, respectively, are varied according to the instantaneous value of the modulating signal while keeping other parameters constant. Delta and sigma delta modulation belong to digital modulation and are widely used in digital communication and digital signal processing and analog to digital converters.

Mobile communication systems and portable electronic equipment demand low-power circuitry to enable longer battery operation. The current-mode (CM) processing has emerged as a promising solution for such circuits as CM circuits are designed for lower voltage swings. Exploiting this virtue of CM processing the researchers have reported a large number of modulator circuits using different CM active building blocks (ABB) such as current conveyor II (CCII) [1], operational transconductance amplifier (OTA) [2-4], current controlled current difference transconductance amplifier (CCCDTA) [5], multiple output current controlled current difference transconductance amplifier (MOCCCDTA) [6], and operational transresistance amplifier (OTRA) [7]. The pulse width of the carrier signal is modulated in accordance with input modulating signal in circuits proposed in [1-7]. Sigma delta modulators are the other class of modulators available in literature [4, 8-15]. These modulators can be classified as designs based on (i) switched capacitor technique [8-11], (ii) switched current technique [12], (iii) Loop filter and quantizer method [13-15], and (iv) ABB [4]. A detailed comparison of these structures is given in Table 1. It is evident from Table 1 that a large number of modulator circuits are available in literature but only the modulator structure of [4] can provide amplitude, frequency, delta, and sigma delta modulated outputs. In this paper, a DVCCTA based versatile modulator is presented which employs two ABBs and two grounded passive elements only as against the three ABBs and three passive elements used in [4].

The paper is organized as follows. Section 2 describes the port relation of DVCCTA and its CMOS based implementation. Operational scheme of the proposed modulator

| Ref. number | Implementation scheme                  | Active element used    | Modulation type                |

|-------------|----------------------------------------|------------------------|--------------------------------|

| [1]         | Schmitt trigger followed by integrator | CCII, Opamps           | PWM                            |

| [2, 3]      | Schmitt trigger followed by integrator | OTAs                   | PWM                            |

| [4]         | Schmitt trigger followed by integrator | OTAs                   | AM, FM, delta, and sigma delta |

| [5]         | Schmitt trigger followed by integrator | CCCDTA                 | PWM                            |

| [6]         | Schmitt trigger followed by integrator | MOCCCDTA               | PWM                            |

| [7]         | Schmitt trigger followed by integrator | OTRA                   | PWM                            |

| [8]         | Switched capacitor                     | Opamps                 | Sigma delta                    |

| [9]         | Comparator based switched capacitors   | Dynamic Comparator OTA | Sigma delta                    |

| [10]        | Class-C inverter switched capacitor    | Class-C inverter       | Sigma delta                    |

| [11]        | Comparator based switched capacitors   | Opamps                 | Sigma delta                    |

| [12]        | Switched current CMOS                  | None                   | Sigma delta                    |

| [13–15]     | Loop filter + quantizer                | Opamps                 | Sigma delta                    |

| Proposed    | Schmitt trigger followed by integrator | DVCCTA                 | AM, FM, delta, and sigma delta |

TABLE 1: Comparison of exiting modulator topologies.

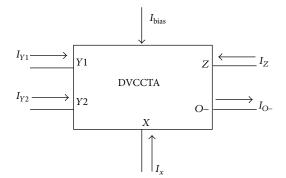

FIGURE 1: Symbol of proposed DVCCTA.

is elaborated in Section 3 wherein a DVCCTA based pulse generator core is described first followed by its applications as amplitude, frequency, delta, and sigma delta modulators. The proposed work is concluded in Section 6.

## 2. DVCCTA

The DVCCTA [16], a relatively new ABB, employs DVCC [17] as input block which is followed by a TA. The circuit symbol of DVCCTA is shown in Figure 1 and its terminal characteristics in matrix form are given by

$$\begin{bmatrix} I_{Y1} \\ I_{Y2} \\ V_X \\ I_Z \\ I_{O-} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 \\ 1 & -1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & -g & 0 \end{bmatrix} \begin{bmatrix} V_{Y1} \\ V_{Y2} \\ I_X \\ V_Z \\ V_{O-} \end{bmatrix},$$

(1)

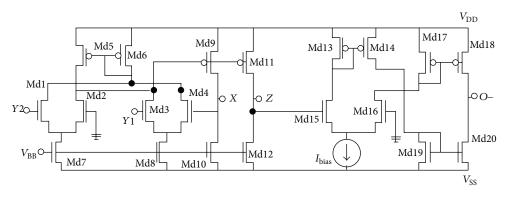

where g is transconductance of the DVCCTA. The CMOS implementation of DVCCTA [16] is given in Figure 2. It comprises of a DVCC block (Md1–Md12) [16] which is followed by transconductance amplifier (Md13–Md20). The value of transconductance (g) is expressed by (2) which

can be adjusted by varying current  $I_{\text{Bias}}$ , thereby making it electronically tunable:

$$g = \sqrt{2\mu C_{ox} \left(\frac{W}{L}\right)_{15,16} I_{\text{Bias}}}.$$

(2)

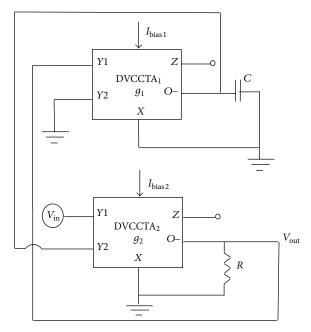

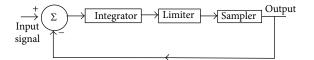

#### 3. Modulator Operational Scheme

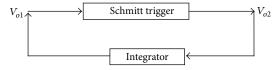

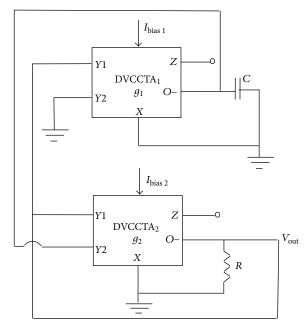

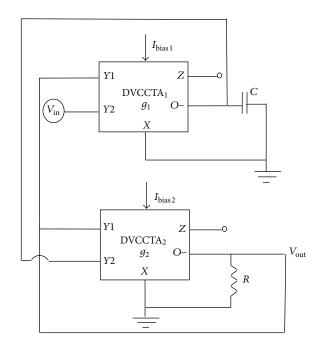

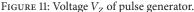

The modulator operational scheme uses pulse generator as a core and its output is used as carrier signal. The pulse generator can be constructed using the well-known scheme of placing an integrator in a feedback loop with Schmitt trigger [18] as shown in Figure 3 and has been implemented using DVCCTA in this work. The DVCCTA based realization of pulse generator is depicted in Figure 4. The first DVCCTA with capacitor *C* forms an integrator, whereas the second DVCCTA works as Schmitt trigger with resistor *R*.

The operation of the circuit is as follows. Both DVCCTAs operate in saturation mode irrespective of the bias currents and voltages at the input terminals as their Z ports are left open. The voltage of Z port would approach to  $V_{DD}$  or  $V_{SS}$  depending upon the current flowing into  $X(I_{in})$  terminal:

$$V_Z = \begin{cases} V_{\rm DD} & \text{for } I_{\rm in} \ge 0\\ V_{\rm SS} & \text{for } I_{\rm in} < 0. \end{cases}$$

(3)

It may be noted that the amplitude of current would be positive if voltage of Y1 terminal is larger than Y2 terminal voltage. The amplitude of current flowing through O- port would remain constant and equal to bias current ( $I_{\text{Bias}}$ ) and the exact values would be given by

$$I_{\rm O-} = \begin{cases} -I_{\rm Bias} & \text{for } I_{\rm in} \ge 0\\ I_{\rm Bias} & \text{for } I_{\rm in} < 0. \end{cases}$$

(4)

FIGURE 2: CMOS implementation of DVCCTA [16].

FIGURE 3: Pulse generator scheme [18].

The maximum and minimmum output voltages of the schmitt trigger are given by the following:

$$V_{\rm max} = I_{\rm Bias2}R,\tag{5a}$$

$$V_{\min} = -I_{\text{Bias2}}R.$$

(5b)

The upper and lower threshold values for the schmitt trigger are given by

$$V_{\rm TH} = V_{\rm max} = I_{\rm Bias2}R,\tag{6a}$$

$$V_{\rm TL} = V_{\rm min} = -I_{\rm Bias2}R.$$

(6b)

The frequency of the output signal can be obtained by calculating the charging (to  $V_{\text{TH}}$ ) and discharging (to  $V_{\text{TL}}$ ) time of the capacitor. The time taken by the capacitor to charge to  $V_{\text{TL}}$  from level  $V_{\text{TH}}$  is given by

$$t_1 = \frac{C\left(V_{\rm TH} - V_{\rm TL}\right)}{I_{\rm Bias1}}.$$

(7)

The time taken by the capacitor to discharge from  $V_{\rm TH}$  to  $V_{\rm TL}$  is given by

$$t_2 = \frac{C\left(V_{\rm TL} - V_{\rm TH}\right)}{-I_{\rm Bias1}}.$$

(8)

The frequency of the output signal is expressed as

$$f = \frac{1}{t_1 + t_2}.$$

(9)

As  $V_{\text{TL}}$  and  $V_{\text{TH}}$  are equal in magnitude, using (6a) and (6b) to (9), the frequency is computed by (10) which can be adjusted electronically via bias currents of DVCCTAs:

$$f = \frac{I_{\text{Bias1}}}{4RCI_{\text{Bias2}}}.$$

(10)

FIGURE 4: Proposed DVCCTA based pulse generator.

In the following subsections, analog (AM and FM) and digital (delta and sigma delta modulation) modulator circuits based on pulse generator circuit of Figure 4 are presented.

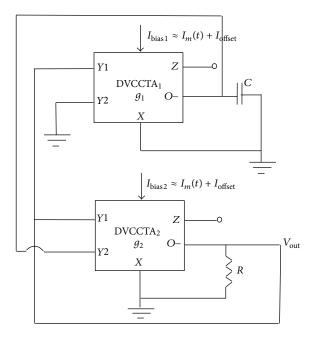

3.1. Amplitude Modulator. In amplitude modulation, the amplitude of the carrier signal varied according to the instantaneous value of the modulating signal. According to (5a) and (5b), the output amplitude of the pulse generator circuit of Figure 4 depends on bias current  $I_{\text{Bias2}}$ . Therefore, the pulse generator circuit can work as amplitude modulator if the bias currents  $I_{\text{Bias1}}$  and  $I_{\text{Bias2}}$  are taken as sinusoidal modulating signal ( $I_m(t)$ ) superposed on the dc offset signal ( $I_{\text{offset}}$ ). The condition on the amplitude of modulating signal and offset current is given by

$$I_{\text{Bias2}} = I_{\text{offset}} + I_m(t) \quad \forall t.$$

(11)

FIGURE 5: Proposed AM modulator.

Using (5a) and (5b), the maximum and minimum output voltages are expressed by

$$V_{\text{max}} = \left(I_{\text{offset}} + I_m(t)\right)R,\tag{12a}$$

$$V_{\min} = -(I_{\text{offset}} + I_m(t))R.$$

(12b)

Thus peak to peak output voltage is given by

$$V_{\text{out}} = 2\left(I_{\text{offset}} + I_m\left(t\right)\right)R.$$

(13)

The output voltage amplitude is proportional to modulating signal if a sufficiently large offset current is chosen. Since the output frequency is function of ratio of bias currents  $I_{\text{Bias1}}/I_{\text{Bias2}}$  as shown by (10), the output frequency remains unaltered if the ratio of bias currents  $I_{\text{Bias1}}$  and  $I_{\text{Bias2}}$  are kept equal. Thus the circuit of Figure 5 works as an amplitude modulator.

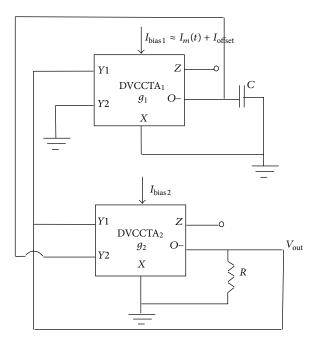

3.2. Frequency Modulator. In frequency modulation, the frequency of the carrier signal varied according to the instantaneous value of the modulating signal. According to (10), the frequency of pulse generator is function of ratio of bias currents  $I_{\text{Bias1}}/I_{\text{Bias2}}$  whereas the output amplitude depends solely on bias current  $I_{\text{Bias2}}$ . Therefore, the pulse generator circuit can work as frequency modulator if a sinusoidal modulating signal ( $I_m(t)$ ) superimposed on the dc offset signal ( $I_{\text{offset}}$ ) is applied as bias currents  $I_{\text{Bias2}}$  while keeping bias current  $I_{\text{Bias2}}$  constant. This selection of bias currents causes the output to toggle between  $I_{\text{Bias2}}R$  and  $-I_{\text{Bias2}}R$  whose frequency varies with the instantaneous value of the modulating current. Figure 6 shows the DVCCTA based frequency modulator.

FIGURE 6: Proposed FM modulator.

FIGURE 7: Delta modulator scheme.

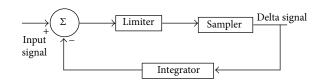

3.3. Delta Modulator. The pulse code modulation (PCM) is fundamental technique for digital modulation. It, however, has drawback of data redundancy in digitally encoded data. The differential pulse code modulation (DPCM) eliminates this problem by encoding difference between successive samples. Delta modulation is a special case of DPCM where the output is one bit encoded. The schematic of delta modulation is shown in Figure 7 wherein the difference of the input and integrated output signal is applied to limiter and sampler. The 1st DVCCTA of Figure 4 gives integrated output as capacitor voltage. The 2nd DVCCTA provides functionality of both limiter and sampler as it generates output voltage  $I_{\text{Bias}2}R$  or  $-I_{\text{Bias}2}R$  by comparing the output voltage with the capacitor voltage. If the modulating input signal is connected to Y1 terminal of 2nd DVCCTA as shown in Figure 8, then the comparison is performed between modulating and integrated output signals which is desired in delta modulator.

3.4. Sigma Delta Modulator. Sigma delta modulation is another scheme, as shown in Figure 9, which can be considered as smoothed version of delta modulation [19]. The name sigma delta modulator comes from the fact that a sigma

FIGURE 8: Proposed delta modulator.

| DVCCTA                          |                       |

|---------------------------------|-----------------------|

| MOSFETs                         | $W (\mu m)/L (\mu m)$ |

| Md5, Md6, Md13, Md14, Md17-Md20 | 5/0.5                 |

| Md9, Md11                       | 8.5/0.5               |

| Md1, Md2, Md3, Md4              | 10/0.5                |

| Md15, Md16                      | 27/0.5                |

| Md7, Md8                        | 27.25/0.5             |

| Md10, Md12                      | 44/0.5                |

which means integrator is put in front of delta modulator. A close observation of the schematic of Figures 7 and 9 indicates that the only difference in the implementation scheme of the delta and sigma delta modulator lies in the way input is fed to a limiter and a sampler blocks. The limiter and sampler blocks as shown in Figures 7 and 9 can be realized with DVCCTA based pulse generator circuit implemented in Figure 4. For sigma delta modulation, the difference between output and modulating signal need to be integrated. This can be easily achieved by the voltage differencing property of the DVCCTA (building block employed in pulse generator circuit), that is by simply connecting modulating signal to Y2 terminal of first DVCCTA block in Figure 4. The resulting DVCCTA based schematic of sigma delta modulator is shown in Figure 10.

FIGURE 9: Sigma delta modulator scheme.

FIGURE 10: Proposed sigma delta modulator.

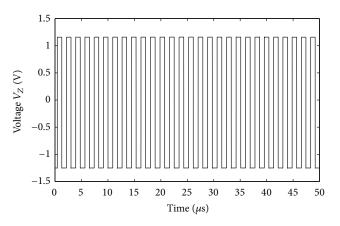

#### 4. Simulation Results

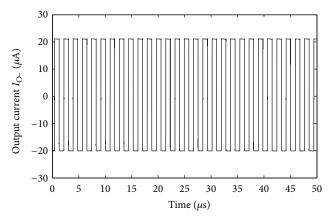

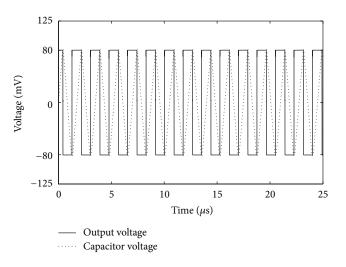

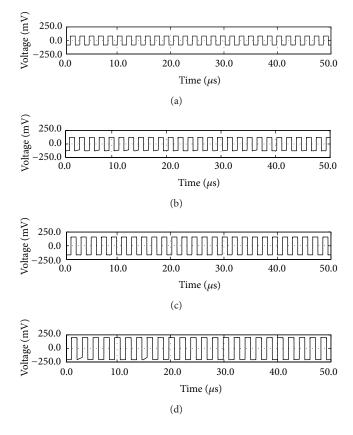

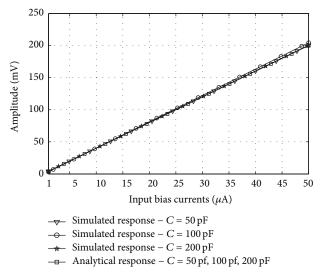

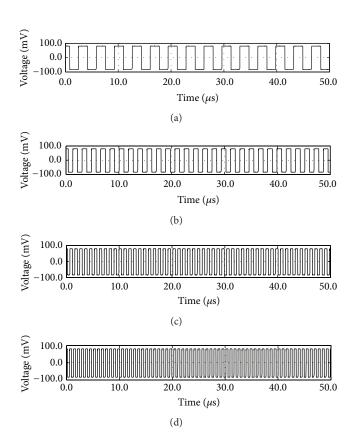

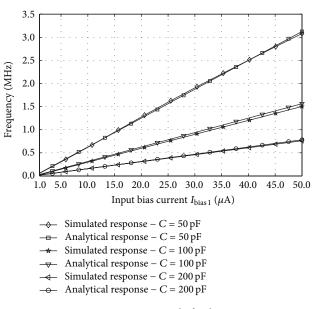

The theoretical propositions have been verified through SPICE simulations using TSMC  $0.25 \,\mu m$  CMOS process model parameters. The CMOS schematic of Figure 2 is used for DVCCTA implementation. Aspect ratio used for various transistors is given in Table 2. Supply voltages of  $V_{DD} = -V_{SS} =$ 1.25 V and  $V_{BB} = -0.8$  V are used and the passive components are chosen as C = 100 pF and  $R = 4 \text{ K}\Omega$ . The voltage  $V_Z$  and current I<sub>O</sub> responses of proposed pulse generator are plotted in Figures 11 and 12, respectively, for  $I_{\text{Bias1}} = I_{\text{Bias2}} = 20 \,\mu\text{A}$ . It may be noted that  $V_Z$  and  $I_{O-}$  saturate to supply voltages and bias current, respectively, thus verifying the theoretical propositions of (3) and (4). The pulse generator output and the voltage across the capacitor are depicted in Figure 13. The transient responses of the pulse generator by simultaneous variation of  $I_{\rm Bias1}$  and  $I_{\rm Bias2}$  from 20  $\mu{\rm A}$  to 50  $\mu{\rm A}$  in step of 10  $\mu$ A are shown in Figures 14(a)–14(d), respectively. The analytical and simulated pulse generator output amplitude curves with respect to bias currents, for different capacitance values (50 pF, 100 pF, and 200 pF) are plotted in Figure 15. It is observed from Figure 15 that the output amplitude is dependent on bias currents irrespective of capacitance value

FIGURE 12: Current  $I_{O-}$  of pulse generator.

which is in tune with the proposed theory. It may also be noted that the analytical and simulated responses are in close agreement. The transient responses of the pulse generator, showing frequency variation with  $I_{\text{Bias1}}$ , have been depicted in Figures 16(a)–16(d) wherein  $I_{\text{Bias1}}$  is varied from 10  $\mu$ A to 50  $\mu$ A in step of 10  $\mu$ A keeping  $I_{\text{Bias2}}$  fixed at 20  $\mu$ A. Figure 17 shows the analytical and simulated frequency versus  $I_{\text{Bias1}}$ curves, for different capacitor values, depicting the frequency controllability through  $I_{\text{Bias1}}$ . Both analytical and simulated frequency curves are found to be in synchronization.

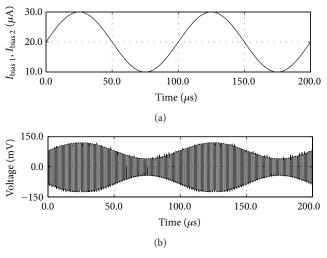

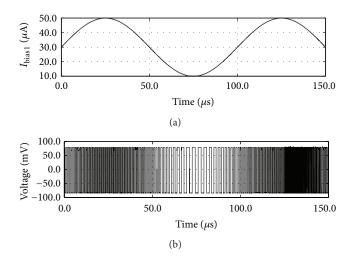

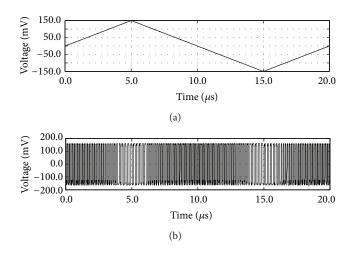

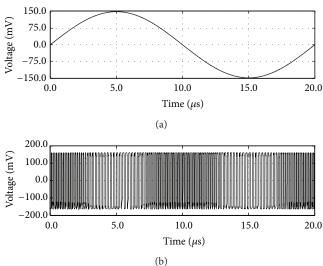

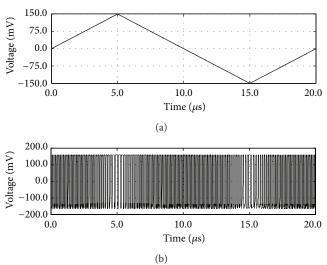

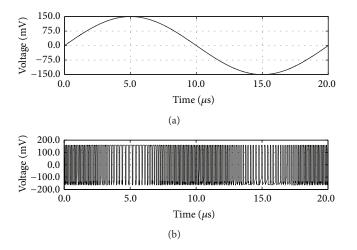

In order to obtain amplitude modulated output, a 10  $\mu$ A, sinusoidal modulating signal of 10 KHz is superimposed on the bias currents  $I_{\text{Bias1}}$  and  $I_{\text{Bias2}}$  keeping DC offset to be 20  $\mu$ A. The modulating current signal and amplitude modulated output voltage are shown in Figures 18(a) and 18(b), respectively. The workability of pulse generator as frequency modulator is verified by applying  $I_{\text{Bias1}}(t)$  as a 20  $\mu$ A, 10 KHz sinusoidal modulating signal with a DC offset of 30  $\mu$ A, and keeping  $I_{\text{Bias2}}$  constant at 20  $\mu$ A. The modulating and the modulated output signals are shown in Figures 19(a) and 19(b), respectively. The verified for two different modulating

FIGURE 13: Output and capacitor's voltage waveform of pulse generator.

FIGURE 14: Output voltage with (a)  $I_{\text{Bias1}} = I_{\text{Bias2}} = 20 \,\mu\text{A}$ , (b)  $I_{\text{Bias1}} = I_{\text{Bias2}} = 30 \,\mu\text{A}$ , (c)  $I_{\text{Bias1}} = I_{\text{Bias2}} = 40 \,\mu\text{A}$ , and (d)  $I_{\text{Bias1}} = I_{\text{Bias2}} = 50 \,\mu\text{A}$ .

signals: a triangular and a sinusoidal, each one represented as 50 KHz, 150 mV signal. The bias currents  $I_{\text{Bias1}}$  and  $I_{\text{Bias2}}$ are, respectively, set as 20  $\mu$ A and 40  $\mu$ A. The outputs of delta modulator for triangular and sinusoidal modulating signals are shown in Figures 20 and 21, respectively, and those

FIGURE 15: Amplitude versus bias current of pulse generator.

FIGURE 16: Output voltage with  $I_{\text{Bias2}} = 20 \,\mu\text{A}$  and  $I_{\text{Bias1}} = (a) 10 \,\mu\text{A}$ , (b) 20  $\mu$ A, (c) 40  $\mu$ A, and (d) 50  $\mu$ A.

for sigma delta modulators are given in Figures 22 and 23, respectively.

FIGURE 17: Frequency control of pulse generator.

FIGURE 18: (a) Modulating signal and (b) amplitude modulated signal.

TABLE 3: Performance characteristics of DVCCTA based modulators.

| Modulator type           | Power dissipation<br>(mW) | Output noise voltage<br>(nV) |

|--------------------------|---------------------------|------------------------------|

| AM modulator             | 0.55 mW                   | 15.64 nV                     |

| FM modulator             | 0.36 mW                   | 4.50 nV                      |

| Delta modulator          | 1.69 mW                   | 5.79 nV                      |

| Sigma delta<br>modulator | 0.63 mW                   | 15.64 nV                     |

## 5. Performance Evaluation

The performance of proposed DVCCTA based modulator circuits is studied in terms of power dissipation. The overall

FIGURE 19: (a) Modulating signal and (b) frequency modulated signal.

FIGURE 20: (a) Triangular modulating signal and (b) delta modulated signal.

FIGURE 21: (a) Sinusoidal modulating signal and (b) delta modulated signal.

FIGURE 22: (a) Triangular modulating signal and (b) sigma delta modulated signal.

performance characteristics of DVCCTA based modulators are summarized in Table 3. The performance of proposed DVCCTA based modulator circuits is studied in terms of power dissipation and output noise voltage. The power dissipation of the versatile modulator circuit when  $I_{\text{Bias1}}$  and  $I_{\text{Bias2}}$ are set to 1  $\mu$ A each is 0.418 mW. The minimum cut-off value of the input bias current,  $I_{\text{Bias2}}$  for proper functioning of circuit as an amplitude modulator, is 0.5  $\mu$ A. The modulating signal with maximum frequency of 3.84 MHz can be applied to FM Modulator when  $I_{\text{Bias1}}$  is set to 0.01  $\mu$ A. On increasing the magnitude of  $I_{\text{Bias1}}$ , the frequency of modulating signal can be increased to maximum value of carrier signal frequency.

## 6. Conclusion

A differential voltage current conveyor transconductance amplifier (DVCCTA) based modulator configuration is presented in this paper. A pulse generator based on DVCCTA has been is proposed and later configured as AM, FM, delta, and sigma delta modulator. The topology uses grounded capacitor and is suitable from integration viewpoint. The simulation results are included to demonstrate the workability of the pulse generator scheme and different modulation schemes. The performance of modulation schemes is studied in terms of power dissipation and noise.

FIGURE 23: Sinusoidal modulating signal and (b) sigma delta modulated signal.

## **Conflict of Interests**

The authors declare that there is no conflict of interests regarding the publication of this paper.

#### References

- M. Siripruchyanun, P. Wardkein, and W. Sangpisit, "A simple pulse width modulator using current conveyor," in *Proceedings of the TENCON*, pp. 452–457, Kuala Lumpur, Malaysia, September 2000.

- [2] H. Kim, H.-J. Kim, and W.-S. Chung, "Pulsewidth modulation circuits using CMOS OTAs," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 54, no. 9, pp. 1869–1878, 2007.

- [3] M. Siripruchyanun and P. Wardkein, "A fully independently adjustable, integrable simple current-controlled oscillator and derivative PWM signal generator," *IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences*, vol. 86, no. 12, pp. 3119–3126, 2003.

- [4] P. Tuwanut, J. Koseeyaporn, and P. Wardkein, "A novel versatile modulator circuit," AEU—International Journal of Electronics and Communications, vol. 63, no. 5, pp. 387–397, 2009.

- [5] M. Siripruchyanun and W. Jaikla, "Current-controlled current differencing transconductance amplifier and applications in continuous-time signal processing circuits," *Analog Integrated Circuits and Signal Processing*, vol. 61, no. 3, pp. 247–257, 2009.

- [6] P. Silapan and M. Siripruchyanun, "Fully and electronically controllable current-mode Schmitt triggers employing only single MO-CCCDTA and their applications," *Analog Integrated Circuits and Signal Processing*, vol. 68, no. 1, pp. 111–128, 2011.

- [7] R. Pandey, N. Pandey, and S. K. Paul, "Voltage mode pulse width modulator using single operational transresistance amplifier," *Journal of Engineering*, vol. 2013, Article ID 309124, 6 pages, 2013.

- [8] G. Bourdopoulos, A. Pneumatikakis, and T. Deliyannis, "Second order sigma-delta modulator realization," in *Proceedings of the 3rd IEEE International Conference on Electronics, Circuits, and Systems (ICECS '96)*, pp. 85–88, Rodos, Greece, October 1996.

- [9] K. Yamamoto and A. Carusone, "A 1-1-1 MASH delta-sigma modulator with dynamic comparator-based OTAs," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 8, pp. 1866–1883, 2012.

- [10] Y. Chae, M. Kwon, and G. Han, "A 0.8-μW switched-capacitor sigma-delta modulator using a class-C inverter," in *Proceedings* of the IEEE International Symposium on Cirquits and Systems (ISCAS '04), vol. 1, pp. I-1152–I-1155, can, May 2004.

- [11] M. Momeni, P. B. Basinchi, and M. Glesner, "Comparison of Opamp-based and comparator-based Delta-Sigma modulation," in *Proceedings of the Design, Automation and Test in Europe (DATE '08)*, pp. 688–693, Munich, Germany, 2008.

- [12] N. Tan and S. Eriksson, "A fully differential switched-current delta-sigma modulator using a single 3.3-V power-supply voltage," in *Proceedings of the IEEE International Symposium on Circuits and Systems*, vol. 5, pp. 485–488, London, UK, June 1994.

- [13] E. Farshidi, "A new current-mode sigma delta modulator," *International Journal of Electronics and Electrical Engineering*, vol. 2, no. 1, pp. 1–9, 2012.

- [14] E. Farshidi and N. Ahmadpoor, "A continuous time sigma delta modulators using CMOS current conveyors," World Academy of Science, Engineering and Technology, vol. 78, pp. 231–234, 2011.

- [15] R. Zanbaghi, P. K. Hanumolu, and T. S. Fiez, "An 80-dB DR, 7.2-MHz bandwidth single opamp biquad based CT ΔΣ modulator dissipating 13.7 mW," *IEEE Journal of Solid-State Circuits*, vol. 48, no. 2, pp. 487–501, 2013.

- [16] A. Jantakun, N. Pisutthipong, and M. Siripruchyanun, "A synthesis of temperature insensitive/electronically controllable floating simulators based on DV-CCTAs," in *Proceedings* of the 6th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI-CON '09), pp. 560–563, Pattaya, Thailand, May 2009.

- [17] H. O. Elwan and A. M. Soliman, "Novel CMOS differential voltage current conveyor and its applications," *IEE Proceedings— Circuits, Devices and Systems*, vol. 144, no. 3, pp. 195–200, 1997.

- [18] A. Sedra and K. Smith, *Microelectronic Circuits*, Oxford University Press, 2004.

- [19] M. Pui-In, U. Seng-Pan, and P. M. Rui, Analog-Baseband Architectures and Circuits for Multistandard and Low-Voltage Wireless Transceivers, Springer, 2007.