Hindawi Publishing Corporation Active and Passive Electronic Components Volume 2014, Article ID 524107, 7 pages http://dx.doi.org/10.1155/2014/524107

# Research Article

# **Signal Integrity Analysis in Carbon Nanotube Based Through-Silicon Via**

## Manoj Kumar Majumder, Archana Kumari, Brajesh Kumar Kaushik, and Sanjeev Kumar Manhas

Microelectronics and VLSI Group, Deptartment of Electronics and Communication Engineering, Indian Institute of Technology Roorkee, Roorkee, Uttarakhand 247667, India

Correspondence should be addressed to Manoj Kumar Majumder; manojbesu@gmail.com

Received 18 October 2013; Revised 15 December 2013; Accepted 16 January 2014; Published 2 March 2014

Academic Editor: Ashok Goel

Copyright © 2014 Manoj Kumar Majumder et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Development of a reliable 3D integrated system is largely dependent on the choice of filler materials used in through-silicon vias (TSVs). This research paper presents carbon nanotube (CNT) bundles as prospective filler materials for TSVs and provides an analysis of signal integrity for different single- (SWCNT), double- (DWCNT), and multi-walled CNT (MWCNT) bundle based TSVs. Depending on the physical configuration of a pair of TSVs, an equivalent electrical model is employed to analyze the inphase and out-phase delays. It is observed that, using an MWCNT bundle (with number of shells = 10), the overall in-phase delays are reduced by 96.86%, 92.33%, 78.35%, and 32.72% compared to the bundled SWCNT, DWCNT, 4-shell MWCNT, and 8-shell MWCNT, respectively; similarly, the overall reduction in out-phase delay is 85.89%, 73.38%, 45.92%, and 12.56%, respectively.

### 1. Introduction

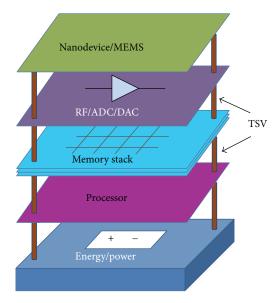

During recent past, several researchers [1] have designed the stacked IC layers on top of each other in order to integrate more devices on a single chip with improved performance. This advocated technique, known as 3D die stacking, primarily results in higher transistor density, improved speed, lower power dissipation and area [2]. Traditionally, the connections were made through the multiple IP (intellectual property) cores on a single die (System-on-Chip), multiple dies in a single package (Multi-Chip Package), and multiple ICs on a printed circuit board (PCB) [3]. Later on, system-inpackage (SiP) technology is introduced where dies containing ICs are stacked vertically on a substrate. Another stacking technique is package-on-package (PoP) that uses vertically stacked multiple packaged chips [4]. The latest development in this area is the 3D stacked IC using through silicon vias (TSVs) that employs a single package containing vertical stack of naked dies and allows the die to be vertically interconnected with another die. TSVs are primarily referred as a vertical electrical connection "VIA" (vertical interconnect access) that passes completely through a silicon wafer or a die.

A TSV based 3D IC offers various advantages in integrating a heterogeneous system onto a single platform as shown in Figure 1.

Copper (Cu), tungsten (W), polysilicon, gold (Au) and polymers are the most commonly used conductive filler materials for TSVs [5]. Cu is preferred due to its economical feasibility and technical superiority, but it faces certain challenges that arise due to fabrication limitations in achieving proper physical vapor deposition (PVD), seed layer deposition for ECD (electrochemical deposition), and performance limitations such as electromigration and higher resistivity. Therefore, researchers have targeted to find some alternative solutions that can potentially replace the Cu TSVs. Carbon nanotubes (CNTs) have emerged as an interesting choice of filler material. Improved thermal stability and negligible electromigration are the added advantages of CNT based TSVs. Thus, compared to Cu TSVs, an impressive result can be obtained for CNT based TSVs [5].

CNTs, known as the allotropes of carbon [6], have an extremely high length-to-diameter ratio up to 132,000,000:1. CNTs are considered as hollow cylindrical structures that are made of concentrically rolled up graphene sheets at specific

FIGURE 1: TSV based 3D technology.

and discrete angles. Depending on the rolled up direction (chirality) and the chiral angle, CNTs can exhibit unique electrical, thermal, mechanical, and chemical properties. The sp<sup>2</sup> bonding in graphene between carbon molecules is stronger than sp<sup>3</sup> bonds in diamond that makes CNTs the strongest and stiffest material in terms of tensile strength and elastic modulus, respectively [7]. The higher current carrying capability [8, 9], long ballistic transport length [8], higher thermal conductivity [10], and mechanical strength [11] are responsible for their exciting prospects in the areas of microelectronics/nanoelectronics [12], spintronics [13], optics [14], material science [15], mechanical [16], and biological fields [16, 17]. Moreover, CNTs can demonstrate a lot of research interest for their applications as energy storage devices, composite materials, field emitting devices, and chemical sensors [12–17]. Depending on the concentrically rolled up graphene sheets, CNTs are classified as single-walled CNTs (SWCNTs) and multi-walled CNTs (MWCNTs). SWCNTs consist of only one rolled up graphene sheet, whereas MWCNTs consist of two or more concentrically rolled up graphene sheets [18]. Double-walled CNT (DWCNT) is a special type of MWCNT wherein only two concentrically rolled up graphene sheets are present. Depending upon their different structures and chirality, CNTs can exhibit either metallic or semiconducting properties. Statistically, a natural mix of CNTs will have 1/3rd of metallic and 2/3rd of semiconducting chirality [8].

The research paper presents an equivalent electrical model that primarily integrates either SWCNT or MWCNT bundled TSVs on Si substrate. The equivalent model takes into account the conductive and capacitive behaviour of the Si substrate [5]. In this model, the capacitive effect of SiO<sub>2</sub> (insulating layer) is also considered and the interconnect line is represented by the electrical equivalent model of SWCNT, DWCNT, and MWCNT bundles. Using the capacitively coupled TSVs, crosstalk delay (signal integrity) is analyzed for in-phase and out-of-phase switching scenarios. The organization of this paper is as follows: Section 1 introduces

the recent research scenario and briefs about the works carried out. Section 2 provides a detailed description of the physical configuration and an equivalent electrical model of a pair of CNT bundle based TSVs. Using the equivalent electrical model of different CNT bundled TSVs, Section 3 analyzes the signal integrity at different TSV heights. Finally, Section 4 draws a brief summary of the paper.

# 2. Physical Configuration and Equivalent *RLC* Model

The stacking of TSVs on Si substrate primarily uses a SWCNT/MWCNT bundle as prospective filler material. A thin layer of silicon dioxide (SiO<sub>2</sub>) is the most commonly used dielectric material for TSVs. However, for high frequency applications, SiO<sub>2</sub> cannot be used due to its large fringing capacitance [19]. Hence, this layer needs to be replaced with a suitable polymer liner. The capacitance of TSVs with polymer liners reduces due to its lower dielectric constants and larger thickness than SiO<sub>2</sub> liners. It results in an improved electrical performance in terms of higher speed, reduced power dissipation, and crosstalk [20, 21].

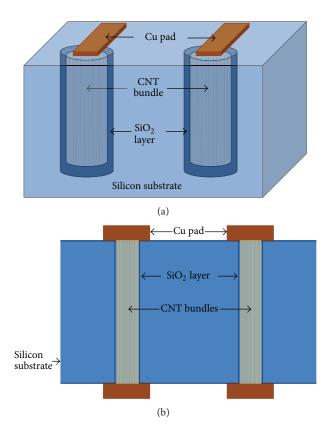

The physical configuration of a pair of CNT bundle based TSV is shown in Figure 2. The number of CNTs ( $N_{\rm CNT}$ ) is approximated using the cross-sectional area of the via and the diameter of each CNT in a bundle. For a given via radius  $r_{\rm TSV}=45$  nm, the cross-sectional area of the TSV is equal to 6361.73 nm². Therefore, the total numbers of SWCNTs, DWCNTs, and 4-, 8-, and 10-shell MWCNTs in a bundle are obtained as 8100, 2869, 876, 244, and 159, respectively, for a fixed SWCNT and DWCNT/MWCNT inner shell diameter ( $d_{\rm CNT}$ ) = 1 nm.

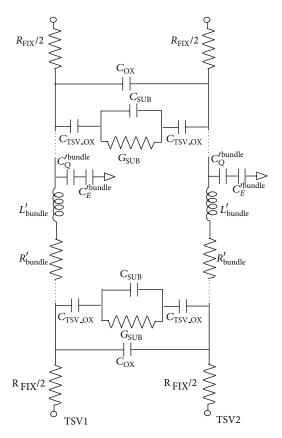

2.1. Equivalent Electrical Model of a Pair of CNT Bundle Based TSVs. Depending on the physical configuration of Figure 2, an equivalent electrical model of a pair of CNT bundle based TSV is shown in Figure 3 [5]. Between each TSV and the silicon substrate,  $\mathrm{SiO}_2$  is used as dielectric layer. The equivalent model takes into account per unit length (p.u.l.) scattering resistance  $(R'_{\mathrm{Bundle}})$ , inductance  $(L'_{\mathrm{Bundle}})$ , quantum  $(C'_{\mathrm{Q}}^{\mathrm{Bundle}})$ , and electrostatic capacitances  $(C'_{E}^{\mathrm{Bundle}})$ .  $C_{\mathrm{TSV\_OX}}$  and  $C_{\mathrm{OX}}$  represent the oxide capacitance around the via and between the TSVs, respectively. The capacitances  $C_{\mathrm{TSV\_OX}}$  and  $C_{\mathrm{OX}}$  primarily depend on the thickness of  $\mathrm{SiO}_2$  layer  $(t_{\mathrm{ox}})$  and can be expressed as

$$C_{\text{TSV\_OX}} = \frac{4\varepsilon_0 \varepsilon_r t_{\text{si}} \left( r_{\text{TSV}} - t_{\text{ox}} \right)}{t_{\text{ox}}}, \quad \text{where } t_{\text{si}} = H_{\text{TSV}},$$

$$C_{\text{OX}} = \left( \frac{2}{C_{\text{TSV\_OX}}} + \left( \frac{\varepsilon_0 \varepsilon_r A}{d_{\text{pitch}}} \right)^{-1} \right)^{-1},$$

$$\text{where } A = \pi r_{\text{TSV}} H_{\text{TSV}},$$

$$(1)$$

where  $H_{\rm TSV}$ ,  $d_{\rm pitch}$ ,  $\varepsilon_0$ , and  $\varepsilon_r$  represent the via height, distance between two TSVs, permittivity of vacuum, and SiO<sub>2</sub>, respectively. The capacitance and conductance of Si substrate are represented as  $C_{\rm SUB}$  and  $G_{\rm SUB}$ , respectively. They

FIGURE 2: (a) Schematic and (b) physical configuration of a pair of CNT bundle based TSVs.

primarily depend on the via area and  $d_{\rm pitch}$  [5] and can be expressed as

$$C_{\text{SUB}} = \frac{\varepsilon_0 \varepsilon_r A}{d_{\text{pitch}}},$$

$$G_{\text{SUB}} = \frac{\pi \sigma}{\ln \left( \left( d_{\text{pitch}} / 2r_{\text{TSV}} \right) + \left( \sqrt{\left( d_{\text{pitch}} / 2r_{\text{TSV}} \right)^2 - 1} \right) \right)},$$

(2)

where  $\sigma = 0.1 (\Omega.\text{cm})^{-1}$  represents the conductivity of the silicon substrate.

2.2. Equivalent RLC Model of CNT Bundle. The modeling of via parasitic is primarily dependent on the number of conducting channels associated with each CNT in a bundle. Naeemi and Meindl [22] modeled the conducting channels of MWCNTs as a function of shell diameter. Assuming one-third shells (or CNTs) as metallic, the average number of conducting channels for a particular shell (or diameter) can be expressed as [22]

$$N_{i}(D_{i}) \approx \begin{cases} k_{1}TD_{i} + k_{2}, & D_{i} > \frac{d_{T}}{T} \\ \frac{2}{3} & D_{i} \leq \frac{d_{T}}{T}, \end{cases}$$

$$(3)$$

FIGURE 3: Equivalent electrical model of a pair of CNT bundle based TSVs.

where  $D_i$  represents the diameter of the ith shell in MWCNT (or SWCNT) and constants  $k_1$  and  $k_2$  have a value of  $3.87 \times 10^{-4} \, \mathrm{nm}^{-1} \, \mathrm{K}^{-1}$  and 0.2, respectively. The thermal energy of electrons and gap between two sub-bands determine the quantitative value of  $d_T$  that is equivalent to  $1300 \, \mathrm{nm} \cdot \mathrm{K}$  at room temperature ( $T = 300 \, \mathrm{K}$ ) [22]. For  $D_i > 4.3 \, \mathrm{nm}$ , the average number of conducting channels is proportional to its shell diameter. Thus, the total number of conducting channels in a CNT is obtained using the summation of conducting channels ( $N_i$ ) of each shell as

$$N_{\text{channel}} = \sum_{i=1}^{n} N_i.$$

(4)

The conduction mechanism in CNT is ballistic or dissipative due to the long mean free path (*mfp*) in the range of micrometers. The diameter dependent *mfp* can be expressed as

$$\lambda_{mfp,i} = \frac{1000D_i}{(T/T_i) - 2}. (5)$$

Thus, the total number of conducting channels in a bundle can be expressed as

$$N_{\text{total}} = N_{\text{channel}} \times N_{\text{CNT}}.$$

(6)

| Via parasitics                                  | SWCNT bundle | DWCNT bundle | MWCNT bundle |           |            |

|-------------------------------------------------|--------------|--------------|--------------|-----------|------------|

|                                                 |              |              | Shell = 4    | Shell = 8 | Shell = 10 |

| $N_{ m total}$                                  | 5400         | 3825         | 2336         | 1352      | 1148       |

| $R_{\mathrm{FIX}}\left(\mathrm{k}\Omega\right)$ | 3.2024       | 3.2013       | 3.2007       | 3.2004    | 3.2003     |

| $R'_{\rm Bundle} (\Omega/\mu {\rm m})$          | 1.19         | 1.25         | 1.36         | 1.37      | 1.38       |

| $L'_{\rm Bundle}$ (pH/ $\mu$ m)                 | 2.99         | 4.23         | 6.93         | 11.97     | 14.09      |

| $C_Q^{'Bundle}$ (fF/ $\mu$ m)                   | 521.53       | 369.45       | 225.61       | 130.58    | 110.89     |

| $C_E^{'Bundle}$ (fF/ $\mu$ m)                   | 76.48        | 29.69        | 10.17        | 3.26      | 2.23       |

| $C'_{CM}$ (fF/ $\mu$ m)                         | 7.71         | 5.07         | 3.17         | 1.93      | 1.64       |

TABLE 1: Via parasitics associated with different CNT bundled TSVs.

Table 2: Percentage reduction of in-phase delay for 10-shell MWCNT bundled TSV w.r.t. SWCNT, DWCNT, and 4-shell and 8-shell MWCNT bundle based TSVs.

| TSV heights (µm)  | %     | reduction in delay for MWC | CNT bundle (shell = 10) in compari | son to          |

|-------------------|-------|----------------------------|------------------------------------|-----------------|

| 13 v neights (µm) | SWB   | DWB                        | MWB (shell = 4)                    | MWB (shell = 8) |

| 50                | 96.62 | 91.82                      | 77.08                              | 30.26           |

| 100               | 96.71 | 92.02                      | 77.53                              | 31.02           |

| 150               | 96.79 | 92.20                      | 77.85                              | 31.52           |

| 200               | 97.32 | 93.27                      | 80.92                              | 38.07           |

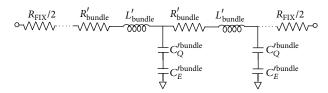

FIGURE 4: Equivalent RLC model of CNT bundle.

FIGURE 5: Capacitively coupled via lines.

The equivalent *RLC* model of CNT bundle is shown in Figure 4. Each CNT in a bundle primarily consists of three different types of resistances: (1) quantum or intrinsic resistance ( $R_q$ ) that is due to the quantum confinement of electrons in a nanowire [23], (2) imperfect metal-nanotube contact resistance ( $R_c$ ) that has a typical value of  $3.2\,\mathrm{k}\Omega$  depending on the fabrication process [24], and (3) scattering resistance (R') that occurs due to the higher nanotube length exceeding *mfps* of electrons. Therefore, the equivalent

intrinsic and the scattering resistance of the ESC can be expressed as [22, 25]

$$R_{\text{FIX}} = \frac{R_q}{N_{\text{total}}} + R_c, \quad \text{where } R_q = \frac{h}{2e^2} \approx 12.9 \,\text{k}\Omega,$$

$$R'_{\text{Bundle}} = \frac{\left(\sum_{i=1}^n \left(R_q/2N_i\lambda_{mfp,i}\right)^{-1}\right)^{-1}}{N_{\text{CMT}}},$$

(7)

where *h*, *n*, and *e* represent Planck's constant, number of CNTs in a bundle, and charge of an electron, respectively.

The equivalent *RLC* model of CNT bundle primarily comprises two different types of capacitances: (1) quantum capacitance ( $C_Q^{'Bundle}$ ) that represents the finite density of states at Fermi energy and (2) electrostatic capacitance ( $C_E^{'Bundle}$ ) that is due to the potential difference between the CNT bundle and the ground plane. Thus, the  $C_Q^{'Bundle}$  and  $C_E^{'Bundle}$  can be expressed as

$$C_Q^{\prime \text{Bundle}} = C_Q^{\prime} \times 2N_{\text{total}}, \text{ where } C_Q^{\prime} = \frac{2e^2}{hv_F},$$

(8)

$$C_E^{\prime \text{Bundle}} = \frac{2\pi\varepsilon_0\varepsilon_r}{\cosh^{-1}\left[\left(d_{\text{CNT}}^{\text{Outer}} + H_{\text{TSV}}\right)/d_{\text{CNT}}^{\text{Outer}}\right]},\tag{9}$$

where  $v_F$  and  $d_{\rm CNT}^{\rm Outer}$  represent the Fermi velocity ( $\approx 8 \times 10^5 \, {\rm m/s}$ ) and the diameter of the outer shell in MWCNT, respectively. The equivalent bundle inductance ( $L_{\rm Bundle}'$ ) consists of (1) kinetic inductance ( $L_K'$ ) that originates from kinetic energy of electrons and (2) magnetic

TABLE 3: Percentage reduction of out-phase delay for 10-shell MWCNT bundled TSV w.r.t. SWCNT, DWCNT, and 4-shell and 8-shell MWCNT bundle based TSVs.

| TSV heights (μm)  | %     | reduction in delay for MWC | CNT bundle (shell = 10) in compari | son to          |

|-------------------|-------|----------------------------|------------------------------------|-----------------|

| 15 v neights (µm) | SWB   | DWB                        | MWB (shell $= 4$ )                 | MWB (shell = 8) |

| 50                | 78.14 | 60.86                      | 35.98                              | 10.19           |

| 100               | 85.27 | 70.12                      | 44.12                              | 10.55           |

| 150               | 88.61 | 75.69                      | 49.89                              | 13.49           |

| 200               | 90.37 | 78.84                      | 53.67                              | 15.99           |

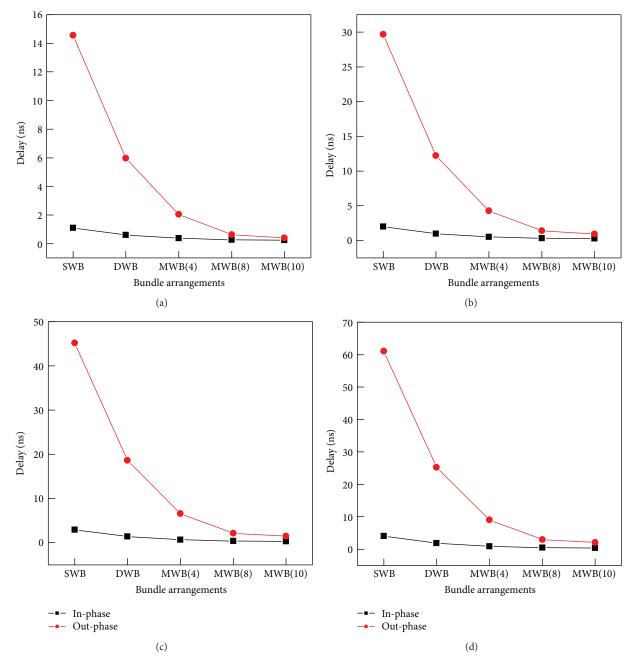

FIGURE 6: Crosstalk delays for different CNT bundles at (a)  $50 \,\mu\text{m}$ , (b)  $100 \,\mu\text{m}$ , (c)  $150 \,\mu\text{m}$ , and (d)  $200 \,\mu\text{m}$  TSV heights, where SWB, DWB, MWB(4), MWB(8), and MWB(10) represent the bundled SWCNT, DWCNT, and 4-shell, 8-shell, and 10-shell MWCNTs, respectively.

inductance  $(L'_M)$  that is due to the magnetic field induced by the current flowing through a nanotube [25]. Therefore, the  $L'_{\text{Bundle}}, L'_K$  and  $L'_M$  can be expressed as

$$L'_{\text{Bundle}} = \frac{L'_K}{2N_{\text{Total}}} + L'_M, \tag{10}$$

where

$$L'_{K} = \frac{h}{2e^{2}v_{F}}, \qquad L'_{M} = \frac{\mu}{2\pi} \ln\left(\frac{y}{d_{\text{CNT}}}\right).$$

(11)

$y(=1~\mu m)$  is the distance between the CNT bundle and the ground plane. Tubes within the same and different bundled TSVs experience a coupling capacitance  $C_{CM}$  as shown in Figure 5. The  $C_{CM}$  has significant effect on crosstalk delay and primarily depends on the spacing between aggressor and victim  $(S_{\text{a-v}})$  lines, number of peripheral SWCNTs/MWCNTs  $(N_{\text{periphery}})$ , and the outermost shell diameter  $(D_n)$ . The  $C_{CM}'$  can be expressed as

$$C'_{CM} = \frac{\pi \varepsilon_0 \varepsilon_r}{\cosh^{-1} \left( S_{a-v} / D_n \right)} \times N_{\text{periphery}}.$$

(12)

The quantitative values of the parasitics associated with different CNT bundled TSVs are placed in Table 1. These parasitic values are obtained using total numbers of conducting channels associated with each CNT in a bundle.

### 3. Signal Integrity Analysis

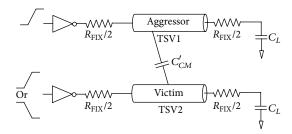

Crosstalk (signal integrity) in coupled lines is broadly classified in two categories: (1) functional and (2) dynamic crosstalk. Under functional crosstalk category, victim line experiences a voltage spike when the aggressor line switches. On the other hand, dynamic crosstalk is observed when aggressor and victim line switches simultaneously. A change in propagation delay is experienced under dynamic crosstalk when adjacent line (aggressor and victim) switches either in the same direction (in-phase) or in the opposite direction (out-of-phase) [26]. This section analyzes the in-phase and out-phase crosstalk delays using capacitively coupled TSV lines as shown in Figure 5. The TSVs in Figure 5 is primarily modeled by the equivalent RLC line of different SWCNT, DWCNT, and MWCNT bundles presented in Figure 3. A CMOS driver with supply voltage  $V_{dd} = 1 \text{ V}$  is used for accurate estimation of crosstalk delay. The TSV lines are terminated by a load capacitance  $C_L = 10$  aF.

Using the above mentioned setup and equivalent *RLC* model, Figure 6 presents the in-phase and out-phase delays for bundled SWCNT, DWCNT, and 4-shell, 8-shell, and 10-shell MWCNTs at different TSV heights ranging from 50  $\mu$ m to 200  $\mu$ m with a step size of 50  $\mu$ m. Irrespective of heights, it is observed that both the in-phase and the out-phase delays are significantly reduced for MWCNT bundle (number of shells = 10) compared to the SWCNT, DWCNT, and 4-shell and 8-shell MWCNT bundled TSVs. The primary reason behind this reduction is the lower quantitative value of  $C'_{CM}$  (Table 1) that primarily depends on the number of CNTs in peripheral layers ( $N_{\rm periphery}$ ). For a fixed via

radius, the number of 10-shell MWCNTs in periphery is lesser compared to the SWCNT, DWCNT, and 4-shell and 8-shell MWCNT bundled TSVs. Therefore,  $C_{CM}^{\prime}$  is substantially reduced (shown in Table 1) that results in minimum crosstalk delay for the bundled TSV having MWCNTs of 10 shells.

Using different CNT bundles, the percentage reduction of in-phase and out-phase crosstalk delays for the 10-shell MWCNT bundle TSV is presented in Tables 2 and 3, respectively. Compared to bundled SWCNT, the overall reduction of in-phase and out-phase crosstalk delays of MWCNT bundle (shell = 10) is 96.85% and 85.59%, respectively.

#### 4. Conclusion

This research paper presented an equivalent electrical model of a pair of CNT bundle based TSVs. The bundles having SWCNTs, DWCNTs, and MWCNTs with different number of shells are used as filler materials. Using capacitively coupled TSV lines, signal integrity is analyzed for different bundle configurations. Encouragingly, it is observed that the overall in-phase and out-phase crosstalk delays are substantially reduced for the bundled TSV having MWCNTs with higher diameters in comparison to the bundle having SWCNTs, DWCNTs, and MWCNTs of smaller diameters.

### **Conflict of Interests**

The authors declare that there is no conflict of interests regarding the publication of this paper.

### References

- [1] B. Noia and K. Chakrabarty, "Pre-bond probing of TSVs in 3D stacked ICs," in *Proceedings of the International Test Conference (ITC '11)*, pp. 1–10, Anaheim, Calif, USA, September 2011.

- [2] P. Pieters and E. Beyne, "3D wafer level packaging approach towards cost effective low loss high density 3D stacking," in Proceedings of the 7th International Conference on Electronics Packaging Technology (ICEPT '06), pp. 1–4, Sanghai, China, August 2006.

- [3] R. E. Jones, "Technology and application of 3D interconnect," in *Proceedings of the IEEE International Conference on Integrated Circuit Design and Technology (ICICDT '07)*, pp. 1–4, Austin, Tex, USA, May 2007.

- [4] W. C. Lo, S. M. Chang, Y. H. Chen et al., "3D chip-to-chip stacking with through silicon interconnect," in *Proceedings of the IEEE International Symposium on VLSI Technology, System and Applications (VLSI-TSA '07)*, pp. 1–2, Hsinchu, Taiwan, April 2007.

- [5] S. Kannan, A. Gupta, B. C. Kim, F. Mohammed, and B. Ahn, "Analysis of carbon naotube based through silicon vias," in *Proceedings of the IEEE 60th Electronic Components and Technology Conference (ECTC '10)*, pp. 51–57, Las Vegas, Nev, USA, June 2010.

- [6] R. Satio, G. Dresselhaus, and S. Desselhaus, *Physical Properties of Carbon Nanotubes*, Imperial College Press, London, UK, 1998.

- [7] H. Li, C. Xu, N. Srivastava, and K. Banerjee, "Carbon nanomaterials for next-generation interconnects and passives: physics,

- status, and prospects," *IEEE Transactions on Electron Devices*, vol. 56, no. 9, pp. 1799–1821, 2009.

- [8] A. Javey and J. Kong, Carbon Nanotube Electronics, Springer, 2009.

- [9] B. Q. Wei, R. Vajtai, and P. M. Ajayan, "Reliability and current carrying capacity of carbon nanotubes," *Applied Physics Letters*, vol. 79, no. 8, pp. 1172–1174, 2001.

- [10] P. G. Collins, M. Hersam, M. Arnold, R. Martel, and P. Avouris, "Current saturation and electrical breakdown in multiwalled carbon nanotubes," *Physical Review Letters*, vol. 86, no. 14, pp. 3128–3131, 2001.

- [11] S. Berber, Y.-K. Kwon, and D. Tománek, "Unusually high thermal conductivity of carbon nanotubes," *Physical Review Letters*, vol. 84, no. 20, pp. 4613–4616, 2000.

- [12] P. Avorious, Z. Chen, and V. Perebeions, "Carbon-based electronics," *Nature Nanotechnology*, vol. 2, no. 10, pp. 605–613, 2007.

- [13] K. Tsukagoshi, B. W. Alphenaar, and H. Ago, "Coherent transport of electron spin in a ferromagnetically contacted carbon nanotube," *Nature*, vol. 401, no. 6753, pp. 572–574, 1999.

- [14] J. A. Misewich, R. Martel, P. Avouris, J. C. Tsang, S. Heinze, and J. Tersoff, "Electrically induced optical emission from a carbon nanotube FET," *Science*, vol. 300, no. 5620, pp. 783–786, 2003.

- [15] N. Wang, Z. K. Tang, G. D. Li, and J. S. Chen, "Materials science: single-walled 4Å carbon nanotube arrays," *Nature*, vol. 408, no. 6808, pp. 50–51, 2000.

- [16] M.-F. Yu, O. Lourie, M. J. Dyer, K. Moloni, T. F. Kelly, and R. S. Ruoff, "Strength and breaking mechanism of multiwalled carbon nanotubes under tensile load," *Science*, vol. 287, no. 5453, pp. 637–640, 2000.

- [17] F. Lu, L. Gu, M. J. Meziani et al., "Advances in bioapplications of carbon nanotubes," *Advanced Materials*, vol. 21, no. 2, pp. 139– 152, 2009.

- [18] H. Li, W.-Y. Yin, K. Banerjee, and J.-F. Mao, "Circuit modeling and performance analysis of multi-walled carbon nanotube interconnects," *IEEE Transactions on Electron Devices*, vol. 55, no. 6, pp. 1328–1337, 2008.

- [19] C. Huang, Q. Chen, D. Wu, and Z. Wang, "High aspect ratio and low capacitance through-silicon-vias (TSVs) with polymer insulation layers," *Microelectronics Engineering*, vol. 104, pp. 12– 17, 2013.

- [20] D. S. Tezcan, F. Duval, H. Philipsen, O. Luhn, P. Soussan, and B. Swinnen, "Scalable through silicon via with polymer deep trench isolation for 3D wafer level packaging," in *Proceedings* of the 59th Electronic Components and Technology Conference (ECTC '09), pp. 1159–1164, San Diego, Calif, USA, May 2009.

- [21] L. Liang, M. Miao, Z. Li, S. Xu, Y. Zhang, and X. Zhang, "3D modeling and electrical characteristics of through-silicon-via (TSV) in 3D integrated circuits," in *Proceedings of the 12th International Conference on Electronic Packaging Technology and High Density Packaging (ICEPT-HDP '11)*, pp. 471–475, Shanghai, China, August 2011.

- [22] A. Naeemi and J. D. Meindl, "Performance modeling for singleand multiwall carbon nanotubes as signal and power interconnects in gigascale systems," *IEEE Transactions on Electron Devices*, vol. 55, no. 10, pp. 2574–2582, 2008.

- [23] P. J. Burke, "Lüttinger liquid theory as a model of the gigahertz electrical properties of carbon nanotubes," *IEEE Transactions on Nanotechnology*, vol. 1, no. 3, pp. 129–144, 2002.

- [24] A. Srivastava, Y. Xu, and A. K. Sharma, "Carbon nanotubes for next generation very large scale integration interconnects," *Journal of Nanophotonics*, vol. 4, no. 1, Article ID 041690, 2010.

- [25] M. S. Sarto and A. Tamburrano, "Single-conductor transmission-line model of multiwall carbon nanotubes," *IEEE Transactions on Nanotechnology*, vol. 9, no. 1, pp. 82–92, 2010.

- [26] A. Vittal, L. H. Chen, M. Marek-Sadowska, K.-P. Wang, and S. Yang, "Crosstalk in VLSI interconnections," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 18, no. 12, pp. 1817–1824, 1999.

Submit your manuscripts at http://www.hindawi.com