Hindawi Publishing Corporation International Journal of Photoenergy Volume 2013, Article ID 171390, 8 pages http://dx.doi.org/10.1155/2013/171390

# Research Article

# p-Type Quasi-Mono Silicon Solar Cell Fabricated by Ion Implantation

# Chien-Ming Lee, 1 Sheng-Po Chang, 1 Shoou-Jinn Chang, 1 and Ching-In Wu<sup>2</sup>

<sup>1</sup> Institute of Microelectronics & Department of Electrical Engineering, Center for Micro/Nano Science and Technology, Advanced Optoelectronic Technology Center, National Cheng Kung University, Tainan 70101, Taiwan

Correspondence should be addressed to Sheng-Po Chang; changsp@mail.ncku.edu.tw

Received 2 January 2013; Revised 3 March 2013; Accepted 13 March 2013

Academic Editor: Peter Rupnowski

Copyright © 2013 Chien-Ming Lee et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

The p-type quasi-mono wafer is a novel type of silicon material that is processed using a seed directional solidification technique. This material is a promising alternative to traditional high-cost Czochralski (CZ) and float-zone (FZ) material. Here, we evaluate the application of an advanced solar cell process featuring a novel method of ion implantation on p-type quasi-mono silicon wafer. The ion implantation process has simplified the normal industrial process flow by eliminating two process steps: the removal of phosphosilicate glass (PSG) and the junction isolation process that is required after the conventional thermal POCl<sub>3</sub> diffusion process. Moreover, the good passivation performance of the ion implantation process improves  $V_{\rm oc}$ . Our results show that, after metallization and cofiring, an average cell efficiency of 18.55% can be achieved using 156 × 156 mm p-type quasi-mono silicon wafer. Furthermore, the absolute cell efficiency obtained using this method is 0.47% higher than that for the traditional POCl<sub>3</sub> diffusion process.

### 1. Introduction

The photovoltaic (PV) industry has benefited from the policies of many successive governments that have offered incentives for power projects such as rooftop solar systems. The resulting increase in demand has grown the solar energy market by at least 20% per annum over the past ten years. The final target of the PV industry is the achievement of grid parity, and lowering manufacturing costs and increasing efficiency are very important steps in achieving this target. Reducing silicon bulk thickness and substituting alternative cheap materials are just two options available for lowering the initial cost of materials. In particular, reducing silicon bulk thickness will increase the amount of wafer per ingot or brick, thereby reducing the price per watt. However, this could produce a wafer handling issue, resulting in a higher wafer breakage rate during cell and module processing.

Substituting alternative cheap materials is one solution to reduce cost. Multicrystalline silicon (mc-Si) substrates have traditionally been used in industrial solar cells owing

to their relatively low cost, particularly compared to that of Czochralski (CZ) grown monocrystalline material. However, they can suffer from low efficiency due to defects attributed to grain boundaries. In this study, we use a p-type quasimono wafer as the starting material. Single-crystal silicon is produced according to a seed directional solidification technique [1] typically used for multicrystalline ingots. The p-type quasi-mono wafer produces higher cell efficiencies than those of multicrystalline silicon material with the same average minority carrier lifetime [1, 2].

Increasing solar cell efficiency will also leverage cost in the solar chain. Solar cell efficiency can be improved by various process methods, including metal-wrap-through (MWT) solar cells [3, 4], emitter-wrap-through (EWT) cells [5, 6], interdigitated backside contact (IBC) cells [7, 8], laser-fired contact cells [9, 10], and ion-implanted cells [11, 12]. Of these methods, ion implantation is one of the most attractive and cost-effective options.

In the present study, we substitute ion implantation for thermal POCl<sub>3</sub> diffusion in commercial silicon solar cells,

<sup>&</sup>lt;sup>2</sup> Inventec Solar Energy Corporation, Taoyuan 335, Taiwan

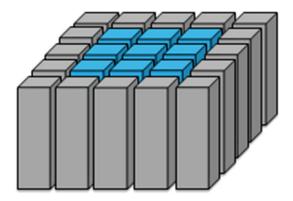

FIGURE 1: The distribution diagram for the 9 ingots used.

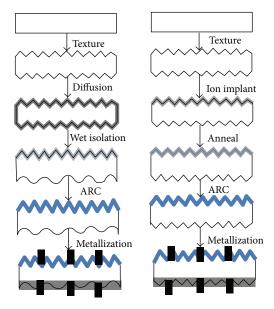

FIGURE 2: Process flow comparison of conventional and ionimplanted solar cell.

which allows us to eliminate two process steps: (1) phosphosilicate glass (PSG) removal and (2) parasitic junction isolation. In the conventional process, PSG is generated on the surface as a result of the reaction between phosphorous and oxygen during the thermal diffusion step. Accordingly, after thermal POCl<sub>3</sub> diffusion, an isolation process is typically required to remove the PSG layer. Moreover, there are two ways to isolate the parasitic junction in the traditional process: wet isolation combined with a PSG clean step and laser isolation. However, both of these isolation processes result in a reduction of the area of the absorption surface; in particular, laser isolation damages the wafer surface and causes lower efficiency.

#### 2. Experiment

Here, we used p-type quasi-mono silicon wafers (GCL-Poly Energy Holdings Limited) with resistivities of  $0.5-3 \Omega cm$ , thicknesses of  $180-200 \mu m$ , and dimensions of  $156 \times 156 mm$ .

A monocrystalline seed was placed at the bottom of a crucible, and polysilicon was then loaded on top of the seed. The underlying seed allowed quasi-mono silicon ingots to grow in the DS furnace. We selected 9 ingots from the center of the brick for use as starting material. These 9 ingots had more than 90% of their area oriented in the (100) direction and less than 10% in other directions. We sliced the 9 ingots into wafers. Figure 1 illustrates the distribution of these 9 ingots within the brick. Figure 2 presents a comparison of the process flow for conventional thermal POCl<sub>3</sub> diffusion with that for ion implantation on quasi-mono silicon wafers. Because the (100) crystalline area constituted more than 90% of ingot area, an alkaline texturing method was used, and processing was conducted using a Rena alkaline machine. First, a saw damage removal step was required in order to reduce surface stress caused by the wire saw used. Wafers were dipped in a batch type system with Teflon material with a high KOH concentration (5.04 wt%) without IPA solution mixing for the saw damage removal process step. Then, anisotropic etching with a KOH: IPA: H<sub>2</sub>O volume ratio of 1:1.6:34 was conducted to produce pyramids on the surface to absorb incoming light and increase the light path in the silicon bulk. In the commercial process, the next step would typically be thermal POCl<sub>3</sub> diffusion to form a p-n junction. Here, a diffusion furnace (Tempress Systems, The Netherlands) was used to perform thermal POCl<sub>3</sub> diffusion. Also, 400 wafers were placed vertically into a quartz boat; then, the boat was moved into a quartz tube and heated to 840°C. The dopant gas reacted with the silicon surface in the presence of O<sub>2</sub> at high temperature, with the following reactions taking place:

$$POCl_3 + O_2 \longrightarrow P_2O_5 + Cl_2 \tag{1}$$

$$P_2O_5 + Si \longrightarrow SiO_2 + P$$

(2)

In the ion implantation process, an inline highthroughput machine (>1000 pcs/hr) from Varian Semiconductor Equipment Associates (VSEA) was used to perform ion implantation. Ion dopant bombarded the wafer surface, subsequently penetrating into the wafer. We selected PH<sub>3</sub> gas as the P<sup>+</sup> ion source for implantation on the surface, with a low beam energy of 10 keV and a dose of  $3.0 \times 10^{15}$ P<sup>+</sup>/cm<sup>2</sup>. However, crystal damage occurred during the ion bombardment procedure. Inclusion of a high-temperature annealing process step can recover this damage. A furnace tube from Tempress Systems was used for thermal annealing. In the annealing step, wafers were placed vertically into a quartz boat, and the boat was moved into a quartz tube. Dry oxide  $(O_2)$  was passed into the tube, activating the dopant. Simultaneously, a thinner silicon oxide formed on the wafer surface according to the following reaction:

$$Si + O_2 \longrightarrow SiO_2$$

(3)

The dry oxide annealing step was conducted to activate the dopant and fabricate the junction. After annealing, the dopant concentration profile was different from that for POCl<sub>3</sub> diffusion [13–16]. According to previous studies, the doping concentration profile of POCl<sub>3</sub> typically ranges from

FIGURE 3: The appearance of quasi-mono silicon after texturing.

an error function complement (erfc) to a Gaussian distribution, with the peak dopant concentration occurring at the surface. Conversely, the profile for ion implantation occurs at a specific depth below the surface. Detailed discussions of these profiles can be found in previous studies [13–16].

After emitter formation, an isolation process was conducted to remove the parasitic junction caused by  $POCl_3$  diffusion during the industrial process flow. A chemical isolation process was performed with an inline roller type transportation system using the InOxSide instrument from Rena GmbH. In this process step, the parasitic junction was removed in an etching bath with  $H_2O:HF:HNO_3:H_2SO_4$  volume ratio of 19:2:11:8.

After the isolation/annealing step,  $\mathrm{SiN}_x$  layer was applied to act as an antireflection coating (ARC). Wafers were automatically placed into a batch type system machine from Centrotherm, and the layer was applied by direct plasma deposition. The  $\mathrm{SiN}_x$  layer not only absorbs more light into silicon, but also passivates the silicon surface. Moreover, the thickness of silicon nitride used in the implantation process in the present study was thinner than that for the conventional  $\mathrm{POCl}_3$  process owing to the thinner silicon oxide layer formed on the wafer surface during the annealing step in the ion implantation process.

After ARC deposition, a metal contact was formed by a Baccini belt type screen printing system and a Despatch cofiring system. During the screen printing process, frontside silver (Ag) paste, Dupont 17F, was printed on the frontside surface to form three bus bars and 83 finger lines. Dupont PV-157 was used as the backside Ag paste and Monocrystal RX-1203 as the backside aluminum (Al) paste.

Berger Lichttechnik single-pulse solar simulators were used to measure the basic parameters and I-V curves of cells under standard test conditions (STCs): irradiance of  $1000 \text{ W/m}^2$ , the AM 1.5 solar spectrum, and temperature of 25°C. Electrical characteristics (including  $V_{\rm oc}$ ,  $I_{\rm sc}$ , FF,  $P_{\rm max}$ , and cell efficiency) were obtained from the I-V curves. The

shunt resistance  $R_{\rm sh}$  was determined from the linear slope of the reverse dark current for each cell. The series resistance  $R_{\rm s}$  was calculated from two I-V curves measured at 1000 W/m<sup>2</sup> and 500 W/m<sup>2</sup>, according to IEC 891.

## 3. Results and Discussion

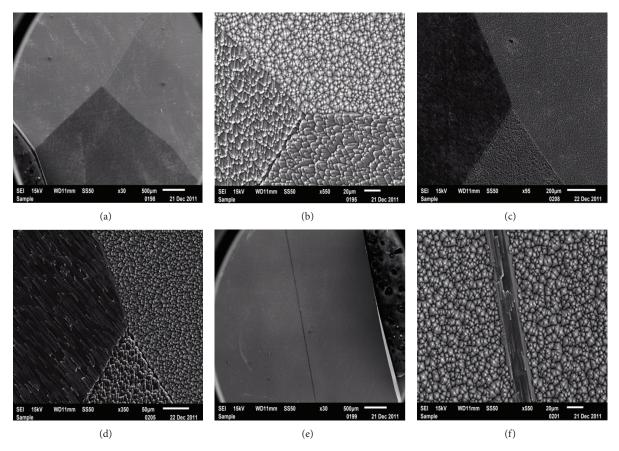

Here, we textured 2000 samples of p-type quasi-mono silicon simultaneously. Figure 3 shows the appearance of the quasimono silicon after texturing, illustrating the many different grains that appear on the surface. Figure 4 illustrates the pyramid topology revealed at different locations within the wafer for 30x (Figure 4(a)) and 550x (Figure 4(b)) SEM at the upper right of the wafer. Three different pyramid orientations are shown. Figures 4(c) and 4(d) also illustrate the pyramid topology for 95x and 350x SEM at the upper right of the wafer, respectively; these are clearly different from Figures 4(a) and 4(b). The figure indicates that quasi-mono silicon wafer exhibits a planar area after alkaline texturing. Figures 4(e) and 4(f) illustrate the pyramid topology for 30x and 550x SEM at the upper left of the wafer and indicate that scrapes have appeared on the quasi-mono silicon wafer. Such differences in topology can be seen clearly after alkaline texturing and are likely due to differences in grain boundaries.

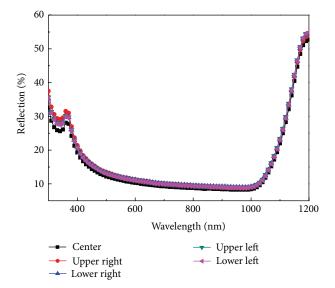

After texturing, a Hitachi U-4100 UV-Vis-NIR spectrophotometer was used to measure the reflection. U-4100 has two light sources that can measure reflection at wavelengths of 240–2600 nm and an integrating sphere that can measure textured wafer. We selected 4 wafers randomly from each group and measured 5 points at 5 different locations within each wafer. Figure 5 illustrates a comparison of the reflection from these different locations after the alkaline texturing process.

As the figure shows, there are small differences in reflections between locations. This is likely due to the different pyramid topologies caused by different grain boundaries. To quantify the performance, we calculated the weighted reflectance  $R_w$ % based on a previously published study [17] as follows:

$$R_{w}\% = \frac{\int_{\lambda_{1}}^{\lambda_{2}} F_{i}(\lambda) Q_{i}(\lambda) R(\lambda) d\lambda}{\int_{\lambda_{1}}^{\lambda_{2}} F_{i}(\lambda) Q_{i}(\lambda) d\lambda},$$

(4)

where  $F_i(\lambda)$  is the photon flux and  $Q_i(\lambda)$  is the cell internal quantum efficiency [18, 19]. Table 1 presents a comparison of  $R_w$ % for 5 different locations within the wafers and indicates that  $R_w$ % is highest for the upper right location at 13.92%. This corresponds to an area with a shiny appearance caused by a different pyramid orientation and planar topology. Conversely, the lowest  $R_w$ % (12.94%) was found for the center location and is thought to be due to the single-crystalline structure in the center.

After texturing, the next step in the ion implantation process was ion implantation itself. For this, 1600 wafers were automatically transferred into the chamber, and  $P^+$  ion sources were implanted onto the wafer surface from the ion source. Then, we divided the 1600 wafers into 4 groups, each with 400 wafers.

FIGURE 4: The pyramid topology shown by SEM at different locations within the wafer.

Table 1: Comparison of  $R_w\%$  of five different locations within the wafer.

| Location | Centre | Upper<br>right | Lower<br>right | Upper<br>left | Lower<br>left |

|----------|--------|----------------|----------------|---------------|---------------|

| $R_w\%$  | 12.94  | 13.92          | 13.88          | 13.87         | 13.71         |

Table 2: Comparison of  $R_{\text{sheet}}$  and uniformity between POCl<sub>3</sub> diffusion and 4 different anneal processes.

| R <sub>sheet</sub> (ohm/sq) | Ave   | MAX   | MIN   | Uniformity |

|-----------------------------|-------|-------|-------|------------|

| POCL <sub>3</sub>           | 64.68 | 67.53 | 61.32 | 4.80%      |

| Anneal_810                  | 70.02 | 73.08 | 68.96 | 2.94%      |

| Anneal_840                  | 65.47 | 67.14 | 63.31 | 2.93%      |

| Anneal_870                  | 61.39 | 63.07 | 59.65 | 2.79%      |

| Anneal_900                  | 57.13 | 59.41 | 56.98 | 2.13%      |

| •                           |       |       |       |            |

These 4 groups were processed at peak temperatures of 810, 840, 870, and 900°C during the subsequent annealing step. A four-point probe was used to measure the sheet resistance ( $R_{\rm sheet}$ ). Table 2 presents a comparison of  $R_{\rm sheet}$  and uniformity for POCl<sub>3</sub> diffusion and the 4 different annealing processes; in particular, the table indicates that  $R_{\rm sheet}$  decreased when the peak temperature was 810–900°C and the baseline  $R_{\rm sheet}$  for the POCl<sub>3</sub> diffusion process was 64.68  $\Omega$ /sq. The  $R_{\rm sheet}$  uniformity for thermal POCl<sub>3</sub>

FIGURE 5: A comparison of the reflection at five different locations within the wafers after the alkaline texturing process.

diffusion was 4.80%, which was worse than that for the implantation process. In fact, the uniformity of the implantation process was below 3%, likely owing to the precise

control exercised over the dose amount by the emitter in the ion implantation apparatus. The good  $R_{\rm sheet}$  uniformity and precise control also enabled a repeatable process for fabrication of lightly doped emitter regions [20–22].

In order to obtain the best performance from the annealing step, 5 p-type quasi-mono wafers, implanted with 2.0 × 10<sup>15</sup> dopant ions at a beam energy of 10 keV on both faces of the wafer, were used to monitor the implied  $V_{\rm oc}$ and carrier lifetime [23] for each condition. The WCT-120 tool from Sinton Instruments uses a quasi-steady-state photoconductance (QSSPC) method to measure implied  $V_{\rm oc}$ and lifetime [24]. Table 3 presents the average implied  $V_{oc}$  and lifetime for each condition. The implied  $V_{\rm oc}$  for wafers doped by thermal POCl $_3$  diffusion was found to be 0.625 V at 1 sun. However, the implied  $V_{oc}$  after high-temperature annealing at 900°C was 0.620 V, the worst among all conditions studied. This was likely because high-temperature annealing can degrade the lifetime and reduce the  $V_{\rm oc}$ . When the annealing temperature was decreased to 840°C, the implied  $V_{oc}$  reached 0.640 V; this higher implied  $V_{\rm oc}$  was likely due to better surface passivation.

In the annealing step, a thinner SiO<sub>2</sub> layer was grown on the wafer surface, and the ion-implanted dopant was activated. The thickness of the SiO<sub>2</sub> was measured by a SemiLab LE-100PV ellipsometer. A single laser wavelength from a 632.8 nm He-Ne laser incident on the wafer surface was used to measure the refractive index and thickness of the dielectric layer. In this study, the (111) silicon polished wafer with a dose of  $3.2 \times 10^{15}$  implanted and a beam energy of 10 keV on its surface was used as the control wafer. During the annealing process, control wafers were processed simultaneously with the experimental p-type quasi-mono silicon wafers in the same tube. Table 4 shows the resulting SiO<sub>2</sub> thickness and uniformity for each condition. The thickness of SiO<sub>2</sub> was found to be around 17 nm and was very similar for all the different conditions. Moreover, the uniformity of SiO<sub>2</sub> was improved at higher annealing temperatures, and we found good SiO<sub>2</sub> thickness uniformity (below 1.3% for each annealing condition).

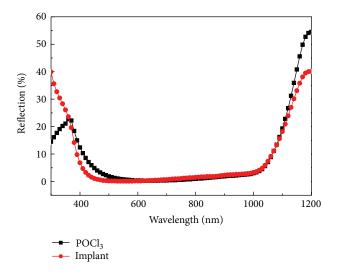

After the junction formation step,  $SiN_x$  was deposited on the silicon surface by PECVD. In contrast to the industrial process, the thickness of the silicon nitride must be modulated during this process owing to the thinner oxide on the surface. In order to minimize the reflection from the frontside of the cell, a 57 nm SiN<sub>x</sub> layer was deposited on top of the SiO<sub>2</sub>. We selected 4 wafers for each condition after the ARC process and measured 5 points at different (100) locations within each p-type quasi-mono wafer. Figure 6 illustrates the comparison of average reflection between POCl<sub>3</sub> diffusion and the ion implantation process after deposition of the ARC. At short wavelengths, the reflection from samples treated by POCl<sub>3</sub> diffusion was lower than that of samples treated by ion implantation. According to the Schuster diagram [25], the optimum refractive index of the inner  $n_1$  and outer  $n_2$  layers of the silicon substrate can be calculated as follows for zero reflection:

$$\frac{AB}{CD} > 0, (5)$$

FIGURE 6: The average reflection for the  $POCl_3$  diffusion and implantation process after  $SiN_x$  deposition.

where

$$A = n_o - n_s, \quad B = n_o n_2^2 - n_s n_1^2,$$

$$C = n_o n_s - n_2^2, \quad D = n_1^2 - n_s n_o.$$

(6)

As explained previously, based on detailed calculations [25], better optical performance can be achieved by using a low-high refractive index design, in which the outer layer has a low refractive index and the inner layer has a high refractive index, on the silicon substrate. However, the design of the ARC in our ion implantation process displayed the opposite characteristics; the outer SiN<sub>x</sub> and inner SiO<sub>2</sub> layers had refractive indexes of 2.03 and 1.46, respectively. Such high-low design tends to cause higher reflection at short wavelengths. In the long-wavelength range, the reflection following implantation was lower than that following POCl<sub>3</sub> diffusion, because the wafer had a planar backside surface owing to the wet chemical isolation process that used HNO<sub>3</sub> and HF to remove the backside p-n junction after POCl<sub>3</sub> diffusion. Table 5 presents a comparison of  $R_w$ % between  $POCl_3$  diffusion and ion implantation after  $SiN_x$  deposition. It is clear that  $R_{uv}$ % resulting from implantation was 4.64%, which is better than that from the POCl<sub>3</sub> process (which was 5.51% after deposition of the ARC).

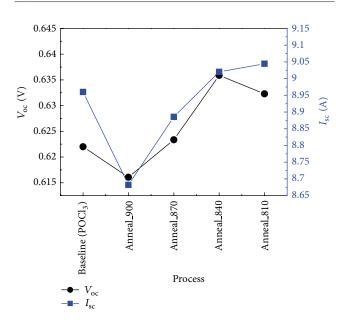

After ARC deposition, the wafers were subjected to screen printing and cofiring processes. Figure 7 illustrates a comparison of  $V_{\rm oc}$  and  $I_{\rm sc}$  between POCl<sub>3</sub> diffusion and the implantation process for each condition and indicates that higher annealing temperatures resulted in lower  $V_{\rm oc}$  and  $I_{\rm sc}$ . The  $V_{\rm oc}$  for the implantation process with an annealing temperature of 900°C was the lowest of all, likely because high-temperature annealing can degrade carrier lifetime and  $V_{\rm oc}$ ; this is in accordance with the results of the WCT-120 measurements. Based on the heavy doping produced by high-temperature annealing,  $I_{\rm sc}$  was lowest following high-temperature annealing at 900°C. When the annealing temperature was reduced to 870°C,  $V_{\rm oc}$  reached 0.623 V,

Table 3: Implied  $V_{oc}$  and lifetime.

|                             | POCl <sub>3</sub> | Anneal_900 | Anneal_870 | Anneal_840 | Anneal_810 |

|-----------------------------|-------------------|------------|------------|------------|------------|

| Implied $V_{\text{oc}}$ (V) | 0.625             | 0.620      | 0.624      | 0.64       | 0.638      |

| Lifetime (μs)               | 30.24             | 24.67      | 29.43      | 53.44      | 50.73      |

TABLE 4: The results of SiO<sub>2</sub> thickness and uniformity.

|                                 | POCl <sub>3</sub> | Anneal_900 | Anneal_870 | Anneal_840 | Anneal_810 |

|---------------------------------|-------------------|------------|------------|------------|------------|

| SiO <sub>2</sub> thickness (nm) | X                 | 17.63      | 17.56      | 17.21      | 17.02      |

| Uniformity (%)                  | X                 | 0.81%      | 0.92%      | 1.05%      | 1.21%      |

Table 5: Comparison of  $R_w$ % between POCl<sub>3</sub> diffusion and implantation after ARC deposition.

|         | POCl <sub>3</sub> | Implant |

|---------|-------------------|---------|

| $R_w$ % | 5.51%             | 4.64%   |

FIGURE 7:  $V_{\rm oc}$  and  $I_{\rm sc}$  for the POCl<sub>3</sub> diffusion and implantation processes.

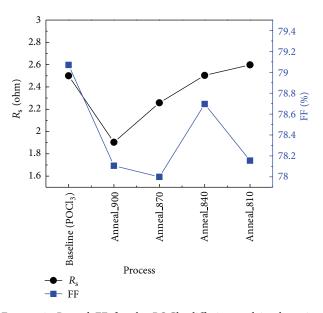

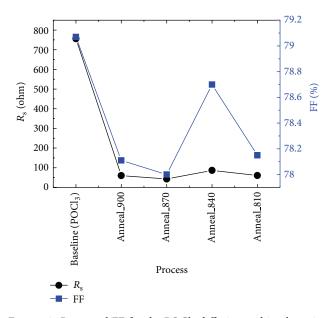

which was higher than that for the POCl<sub>3</sub> diffusion process. However,  $I_{\rm sc}$  was still lower than that for POCl<sub>3</sub>diffusion owing to the lower  $R_{\rm sheet}$  of 61.36  $\Omega/{\rm sq}$ . As the annealing temperature reached 840°C,  $V_{\rm oc}$  reached its highest value of 0.636 V. As shown in Figure 8,  $R_{\rm s}$  was highest for the implantation process with an annealing temperature of 810°C, likely because the highest sheet resistance (70.02  $\Omega/{\rm sq}$ ) would have produced the worst metal contact. Besides the condition of annealing temperature at 810°C, the  $R_{\rm s}$  of the implantation process is lower than that of POCl<sub>3</sub> diffusion process. This was likely due to good  $R_{\rm sheet}$  uniformity caused by precise doping control by the ion implantation instrument. Moreover, higher annealing temperatures can achieve heavy doping and result in good contact with metal. As shown in Figure 9, the higher annealing temperature also caused a lower  $R_{\rm shunt}$ , because a higher annealing temperature

FIGURE 8:  $R_{\rm s}$  and FF for the POCl<sub>3</sub> diffusion and implantation processes.

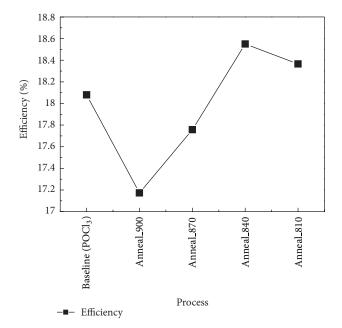

degrades the bulk lifetime, which lowers  $R_{\rm shunt}$ . The FF of the implantation process was highest for an annealing temperature of 840°C owing to the lower  $R_{\rm s}$  and higher  $R_{\rm shunt}$  performances. Moreover, the best average efficiency of 18.55% was found for the implantation process with an annealing temperature of 840°C (Figure 10). All electrical characteristics are presented in Table 6. In general, higher efficiency was found to result from higher  $V_{\rm oc}$  and  $I_{\rm sc}$ . Therefore, our results indicate that quasi-mono silicon wafer produced by ion implantation can improve photovoltaic cell efficiency. Table 7 presents the cell conversion cost per watt for traditional and implant processes for the quasi-mono wafer substrate. It is clear that the cost of the traditional process (0.1664 USD) was much higher than that of the implant process (0.1617 USD).

#### 4. Conclusions

In this study, we investigated a novel type of silicon material, the quasi-mono wafer, for use in high-efficiency solar cells. We produced this material by ion-implanted emitter formation and were able to raise the absolute cell efficiency of a

|                               | $U_{ m oc}$ | $I_{ m sc}$ | $R_{ m s}$ | $R_{ m sh}$ | FF    | $N_{ m Cell}$ | $I_{ m revl}$ |

|-------------------------------|-------------|-------------|------------|-------------|-------|---------------|---------------|

| Baseline (POCl <sub>3</sub> ) | 0.622       | 8.96        | 2.50       | 756         | 79.07 | 18.08         | 0.03          |

| Anneal_900                    | 0.616       | 8.68        | 1.90       | 59.82       | 78.11 | 17.17         | 0.47          |

| Anneal_870                    | 0.623       | 8.89        | 2.26       | 42.71       | 78.00 | 17.76         | 0.65          |

| Anneal_840                    | 0.636       | 9.02        | 2.50       | 86.34       | 78.70 | 18.55         | 0.52          |

| Anneal_810                    | 0.632       | 9.04        | 2.60       | 83.43       | 78.15 | 18.37         | 0.55          |

TABLE 6: Characteristics of POCl<sub>3</sub> diffusion and implantation processes.

FIGURE 9:  $R_{\rm shunt}$  and FF for the POCl<sub>3</sub> diffusion and implantation processes.

FIGURE 10: Efficiency for the  $POCl_3$  diffusion and implantation processes.

Table 7: The cell conversion cost per watt of traditional and implant processes on quasi-mono wafer substrate.

| Station/process                        | Traditional process | Implant process |  |

|----------------------------------------|---------------------|-----------------|--|

| Texturing (USD)                        | 0.07                | 0.07            |  |

| Implant (USD)                          |                     | 0.08            |  |

| Anneal (USD)                           |                     | 0.05            |  |

| Diffusion (USD)                        | 0.068               |                 |  |

| PSG clean (USD)                        | 0.033               |                 |  |

| Wet isolation (USD)                    | 0.036               |                 |  |

| SiN (USD)                              | 0.075               | 0.08            |  |

| Screen printing (USD)                  | 0.45                | 0.45            |  |

| Conversion cost (USD)                  | 0.732               | 0.73            |  |

| Cell efficiency (%)                    | 18.08%              | 18.55%          |  |

| Wafer area (m <sup>2</sup> )           | 0.024336            | 0.024336        |  |

| Watts/wafer                            | 4.40                | 4.51            |  |

| Cell conversion cost<br>Per watt (USD) | 0.1664              | 0.1617          |  |

quasi-mono silicon wafer by 0.47% by following a simplified process flow that eliminates the PSG strip and junction isolation steps. The  $R_{\rm sheet}$  uniformity from implantation was found to be better than that from the POCl<sub>3</sub> diffusion process owing to the precise dopant control exercised by the ion implantation instrument. After activation by an annealing process, the implied  $V_{\rm oc}$  from the implantation process with an annealing temperature less than 900°C was found to be better than that from the POCl<sub>3</sub> diffusion process; this was likely due to the good surface passivation caused by the implantation and annealing processes. However, owing to the thinner SiO<sub>2</sub> formed on the surface by the annealing process, the thickness of the silicon nitride should be modified to minimize  $R_w$ %. After metallization, we achieved an average cell efficiency of 18.55%.

## Acknowledgments

This work was supported by the National Science Council under Contract n. NSC 101-2221-E-006-139. This work was also supported in part by the Center for Frontier Materials and Micro/Nano Science and Technology, National Cheng Kung University, Taiwan. This work was also supported in part by the Advanced Optoelectronic Technology Center, National Cheng Kung University, under projects from the Ministry of Education. The authors wish to thank Professor

S. J. Chang of National Cheng Kung University and Haw Yen, COO of Inventec Solar Energy Corporation, for their assistance in this study. This work is supported in part by Inventec Solar Energy Corporation.

#### References

- N. Stoddard, W. Bei, I. Witting et al., "Casting single crystal silicon: novel defect profiles from BP solar's Mono<sup>2</sup> wafers," *Solid State Phenomena*, vol. 131–133, pp. 1–8, 2008.

- [2] N. Stoddard, R. Sidhu, J. Creager et al., "Evaluating BP solar's Mono<sup>2</sup> material: lifetime and cell electrical data," in *Proceedings* of the 34th IEEE Photovoltaic Specialists Conference (PVSC '09), pp. 001163–001168, June 2009.

- [3] E. Lohmüller, B. Thaidigsmann, M. Pospischil et al., "20% efficient passivated large-area metal wrap through solar cells on boron-doped Cz silicon," *IEEE Electron Device Letters*, vol. 32, no. 12, pp. 1719–1721, 2011.

- [4] B. Thaidigsmann, A. Drews, T. Fellmeth et al., "Synergistic effects of rear-surface passivation and the metal wrap through concept," *IEEE Journal of Photovoltaics*, vol. 2, no. 2, pp. 109–113, 2012.

- [5] F. Kiefer, C. Ulzhöfer, T. Brendemühl et al., "High efficiency Ntype emitter-wrap-through silicon solar cells," *IEEE Journal of Photovoltaics*, vol. 1, no. 1, pp. 49–53, 2011.

- [6] D. Kray, J. Dicker, D. Osswald et al., "Progress in high-efficiency emitter-wrap-through cells on medium quality substrates," in Proceedings of the 3rd World Conference on Photovoltaic Energy Conversion, pp. 1340–1343, Osaka, Japan, May 2003.

- [7] J. Renshaw and A. Rohatgi, "Device optimization for screen printed interdigitated back contact solar cells," in *Proceedings* of the 37th IEEE Photovoltaic Specialists Conference (PVSC '11), 2011.

- [8] F. J. Castaño, D. Morecroft, M. Cascant et al., "Industrially Feasible > 19% efficiency IBC cells for pilot line processing," in Proceedings of the 37th IEEE Photovoltaic Specialists Conference (PVSC '11), 2011.

- [9] T. Böscke, R. Hellriegel, T. Wütherich et al., "Fully screenprinted PERC cells with laser-fired contacts an industrial cell concept with 19.5% efficiency," in *Proceedings of the 37th IEEE Photovoltaic Specialists Conference (PVSC '11)*, 2011.

- [10] P. Ortega, G. López, A. Orpella et al., "Crystalline silicon solar cells beyond 20% efficiency," in *Proceedings of the 8th Spanish Conference on Electron Devices (CDE '11)*, February 2011.

- [11] M. Jeon, J. Lee, S. Kim, W. Lee, and E. Cho, "Ion implanted crystalline silicon solar cells with blanket and selective emitter," *Materials Science and Engineering B*, vol. 176, no. 16, pp. 1285–1290, 2011.

- [12] T. Janssens, N. E. Posthuma, B. J. Pawlak, E. Rosseel, and J. Poortmans, "Implantation for an excellent definition of doping profiles in si solar cells," in *Proceedings of the 25th European Photovoltaic Solar Energy Conference and Exhibition 5th World Conference on Photovoltaic Energy Conversion*, Valencia, Spain, 2010.

- [13] H. F. Wolf, Semiconductors, John Wiley & Sons, 1971.

- [14] A. S. Grove, *Physics and Technology of Semiconductor Devices*, John Wiley & Sons, 1967.

- [15] D. V. Morgan, K. Board, and R. H. Cockrum, An Introduction to Microelectronic Technology, John Wiley & Sons, 1985.

- [16] S. M. Sze, Semiconductor Device Physics and Technology, John Wiley & Sons, 1969.

- [17] D. Redfield, "Method for evaluation of antireflection coatings," Solar Cells, vol. 3, no. 1, pp. 27–33, 1981.

- [18] G. E. Jellison and F. A. Modine, "Optical constants for silicon at 300 and 10 K determined from 1.64 to 4.73 eV by ellipsometry," *Journal of Applied Physics*, vol. 53, no. 5, pp. 3745–3753, 1982.

- [19] E. Palik, *Handbook of Optical Constants of Solids*, Academic Press, New York, NY, USA, 1985.

- [20] R. Low, A. Gupta, N. Bateman et al., "High efficiency selective emitter enabled through patterned ion implantation," in *Proceedings of the 35th IEEE Photovoltaic Specialists Conference (PVSC '10)*, pp. 001440–001445, Honolulu, Hawaii, USA, 2010.

- [21] J. Benick, N. Bateman, and M. Hermle, "Very low emitter saturation current densities on ion implanted boron emitters," in *Proceedings of the 25th European Photovoltaic Solar Energy Conference and Exhibition (EU-PVSEC '10)*, pp. 1169–1173, Valencia, Spain, September 2010.

- [22] T. Janssens, N. E. Posthuma, B. J. Pawlak, E. Rosseel, and J. Poortmans, "Implantation for an excellent definition of doping profiles in si solar cells," in *Proceedings of the 25th European Photovoltaic Solar Energy Conference and Exhibition (EUPVSEC '10)*, pp. 1179–1181, Valencia, Spain, September 2010.

- [23] R. A. Sinton, A. Cuevas, and M. Stuckings, "Quasi-steady-state photoconductance, a new method for solar cell material and device characterization," in *Proceedings of the 25th IEEE Photovoltaic Specialists Conference (PVSC '96)*, pp. 457–460, Washinton, DC, USA, May 1996.

- [24] R. A. Sinton and A. Cuevasa, "Contactless determination of current-voltage characteristics and minority-carrier lifetimes in semiconductors from quasi-steady-state photoconductance data," *Applied Physics Letters*, vol. 69, no. 17, article 2510, 3 pages, 1996.

- [25] B. A. Moys, "The theory of double-layer antireflection coatings," Thin Solid Films, vol. 21, no. 1, pp. 145–157, 1974.

Submit your manuscripts at http://www.hindawi.com