Hindawi Publishing Corporation Journal of Electrical and Computer Engineering Volume 2011, Article ID 507381, 12 pages doi:10.1155/2011/507381

## Review Article

# **Open-Loop Wide-Bandwidth Phase Modulation Techniques**

## Nitin Nidhi,1 Pin-En Su,2 and Sudhakar Pamarti1

<sup>1</sup> Electrical Engineering Department, University of California, Los Angeles, CA 90095-1594, USA

Correspondence should be addressed to Nitin Nidhi, nitin@ee.ucla.edu

Received 31 May 2011; Accepted 16 August 2011

Academic Editor: Kenichi Okada

Copyright © 2011 Nitin Nidhi et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

The ever-increasing growth in the bandwidth of wireless communication channels requires the transmitter to be wide-bandwidth and power-efficient. Polar and outphasing transmitter topologies are two promising candidates for such applications, in future. Both these architectures require a wide-bandwidth phase modulator. Open-loop phase modulation presents a viable solution for achieving wide-bandwidth operation. An overview of prior art and recent approaches for phase modulation is presented in this paper. Phase quantization noise cancellation was recently introduced to lower the out-of-band noise in a digital phase modulator. A detailed analysis on the impact of timing and quantization of the cancellation signal is presented. Noise generated by the transmitter in the receive band frequency poses another challenge for wide-bandwidth transmitter design. Addition of a noise transfer function notch, in a digital phase modulator, to reduce the noise in the receive band during phase modulation is described in this paper.

#### 1. Introduction

The rapid growth of new communication standards like LTE and WiMAX has led to high data rate, wide signal bandwidth, and high peak-to-average-power ratio. Additionally, transmission of 1-2 GHz bandwidth signals in the unlicensed frequency band at 60 GHz is also gaining momentum. Since total power consumption is largely determined by the efficiency of the power amplifier used, high-efficiency architectures, like polar [1–5] and out-phasing [6, 7], are preferable for future designs. Both of these architectures require a phase modulator as one of their key building blocks. The bandwidth of these modulators increases with the bandwidth of the transmitted signal. The concept of a software-defined radio, which can support multiple programmable carrier frequencies and provides maximum flexibility in data rates, is being looked at as a desirable and viable enhancement for future radios. Such a transmitter may also require a widebandwidth phase modulator.

Besides being wideband, a digital implementation of the phase modulator should be favored as it comes with several advantages—it (1) enables implementation of calibration algorithms to correct for transmitter nonlinearity, PVT variations, and, in a polar architecture, AM/PM path delay

mismatch, (2) allows shaping of quantization noise transfer function to reduce in-band noise, (3) allows dynamic element matching to make linearity insensitive to component mismatches, (4) permits reconfigurability to meet the requirements for more than one communication standard, and (5) eases porting of design from one process to the next and hence readily benefits from technology scaling. On the other hand, the digital implementation poses new challenges in terms of quantization noise and spectral images. Furthermore, PVT variation, nonlinearity and power of the front-end digital-to-phase block, although minimized by digital techniques, still require optimization.

Traditionally, phase modulators have been implemented using a phase-locked loop (PLL) for narrow-band modulation [2–5, 8–11]. A second input port, inside a PLL, was employed to enable wideband modulation capability to such modulators [7, 12–17]. But these techniques have not been successful for applications beyond GSM/EDGE [2–5, 13, 17] and WCDMA [7, 12]. LTE and WiMAX both require widerbandwidth modulators. Recently, open-loop phase switching technique, that dynamically selects a signal from a bank of signals at the carrier frequency but with different phase offsets, was proposed for digital wide-bandwidth phase modulation. Quadrature signals at the output of a frequency

<sup>&</sup>lt;sup>2</sup> Broadcom Corporation, Irvine, CA 92617-3038, USA

divider [18], output signals of a ring oscillator [19], and phase interpolation [20] were used to form the bank of reference signals. An overview of both open-loop and closed-loop techniques for phase modulation is presented in this paper, contrasting their performance limitations. Finite resolution in the digital phase modulator results in phase quantization noise (PQN). A PQN cancellation technique was proposed in [20] to reduce the out-of-band emission from the phase modulator. The signal processing details of this technique along with methods to further improve its effectiveness are described in this paper.

The quantization noise added by the modulator must not violate the transmit spectrum mask and the receive band noise requirement of a frequency division duplexing (FDD) system. FDD is commonly employed in cellular systems like GSM/EDGE, WCDMA, and LTE. Recent advances towards a software-defined radio (SDR) promotes coexistence of multiple radios on an integrated circuit. This trend will further increase the requirements on emission in the receive band frequencies. The noise component due to PLL phase noise can be reduced to meet the receive band noise requirements for WCDMA without requiring additional filtering. However, a high Q band pass filter, like a SAW filter, will be required to filter out the quantization noise component. Such a filter is costly and must be avoided to achieve a fully integrated transmitter. A more elegant solution will be to reduce the noise at the receive band frequency by design. This will not only save the cost of an additional costly board component but also provide the flexibility in changing the position and order of the notch. A detailed description of this approach is presented in this paper.

The paper is organized as follows. Section 2 presents an overview of prior art on phase modulation techniques and describes the concept of digital phase modulation. Section 3 describes the concept and analysis of a phase quantization noise cancellation technique, and Section 4 describes a solution to meet the receive band noise specification. A conclusion is given in Section 5.

## 2. Wide-Bandwidth Digital Phase Modulation

In one of the simplest implementations of phase or frequency modulation, the modulation data is applied to the control voltage of a voltage-controlled oscillator (VCO). Although, this technique is open-loop and wideband, it suffers from frequency drift, VCO transfer function nonlinearity and variations over PVT, high close-in phase noise, and loss of transmission during periods of frequency lock. In order to find a solution for these problems, broadly two categories of phase modulators have emerged—closed-loop and open-loop phase modulation.

2.1. Closed-Loop Phase Modulation. If continuous feedback control is applied to a VCO, to arrive at a conventional PLL, close-in phase noise is improved and carrier frequency is tightly controlled. In this case, modulation data has been successfully applied using a multimodulus feedback divider (MMD) in a fractional-N PLL [8, 9]. In this technique,

FIGURE 1: Block diagram of DCO gain calibration as used in [21].

however, the high-frequency content of the modulation data is filtered out by the loop filter of the PLL making it unsuitable for wide-bandwidth phase modulation. Bandwidth extension methods like phase noise cancellation [10, 22–26], multiphase fractional-N PLL [27], type I fractional-N PLL with sharp loop filter [28], and digital pre-emphasis [11] have been applied, but even the best in state-of-theart designs have not exceeded 3 MHz. Additionally, this technique can create low-frequency fractional spurs at PLL output.

In order to obtain further increase in bandwidth, the so-called two-point modulation has been often used [12–17]. Since the injection of modulation data at any node of the PLL loop is either high-pass filtered or low-pass filtered, it is injected at two nodes simultaneously such that the sum of the two transfer functions becomes wideband. The most commonly used injection nodes are the MMD and the VCO control voltage to achieve wide-bandwidth FM. A common problem encountered in this approach is the loss in SNR due to gain and phase mismatch between the two paths. Since  $K_{VCO}$  must be known for gain matching, an on-chip  $K_{VCO}$  estimation method becomes important. Nonetheless, this technique has been successfully used to generate transmit signals meeting GSM/EDGE and WCDMA requirements.

In [29], gain matching was obtained by applying a square wave input to the two modulation input nodes. The calibration loop then minimizes the error voltage developed across the loop filter zero setting resistor. The approach taken in [21] to measure digitally controlled oscillator (DCO) gain and PLL loop gain was to measure the phase error in response to a DCO control change (Figure 1). The PLL loop, reduced to type I operation by holding the digital integral path, compensates for the frequency error by adjusting the phase error at phase detector input. The calibration loop then senses the phase error using a bang-bang PFD and modulates the fractional part of the feedback divider until the phase error is reduced to a very small value. Using the new frequency divider value so obtained, the DCO gain was calculated.

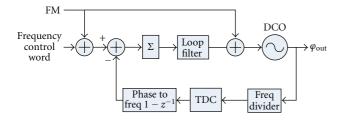

FIGURE 2: Two-point FM in an all-digital PLL [13].

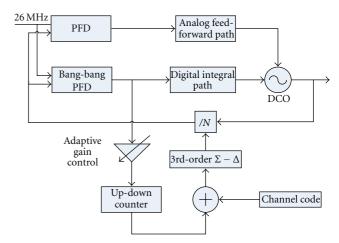

The development of an all-digital PLL (ADPLL) [13, 30–33] has opened up new possibilities for accomplishing phase modulation, as the signals within the PLL loop have become more predictable. Besides this, injection of digital data can be readily achieved in the digital domain, at most of the internal nodes of the PLL. The design presented in [13] took advantage of this feature of a digital PLL and injected the frequency modulation data to the control word of DCO and the carrier frequency control word of the PLL (Figure 2).

The design presented in [12] introduced VCO transfer function linearization technique for two-point modulation for WCDMA. It utilized a local negative feedback loop around the VCO to obtain a fairly constant K<sub>VCO</sub>. This local loop employed an analog technique to measure the VCO frequency, which forms the feedback signal. Although gain and phase calibration techniques have helped to increase the robustness and bandwidth of phase modulators, to the best of the authors' knowledge, their application have not been demonstrated on even wider modulation standards such as WLAN, WiMAX, and LTE.

2.2. Open-Loop Phase Modulation. The bandwidth limitation and gain and phase mismatch issue associated with two-point modulation techniques can be avoided by using open-loop modulation techniques, where modulation is performed outside the frequency synthesizer loop. Essentially, it isolates the carrier frequency generation block from the data modulation block, yielding a modulator which does not involve a low-pass filter (the loop filter) in its path. Hence, these modulators can achieve very wide bandwidth.

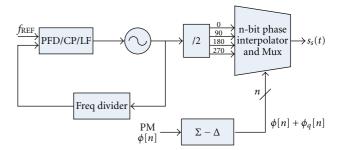

In a typical open-loop phase modulator, a phase generator block produces multiple phases at the carrier frequency. It is followed by a phase multiplexer whose output is controlled by the phase modulation data. For a given sequence of desired digital phase values  $\varphi[n]$ , a  $\Sigma - \Delta$  modulator quantizes each phase sample  $\varphi[n]$  to one of the M available phases,  $2\pi \times k/M$ ,  $k=0,1,\ldots,M-1$ . The output of the  $\Sigma-\Delta$  modulator controls a digital-to-phase converter, whose inputs are M phase signals,  $s_k = \cos(\omega_c + 2\pi \times k/M)$ . Note that  $\omega_c$  is the carrier frequency in rad/s. The digital-to-phase converter can be a phase multiplexer with M phase inputs or a digital phase interpolator. The resultant synthesized signal can be written as

$$s_s(t) = \cos\left(\omega_c t + \sum_{n=1}^{\infty} \left(\phi[n] + \phi_q[n]\right) \cdot p(t - nT_s)\right), \quad (1)$$

FIGURE 3: Open-loop phase modulator [18].

where pulse-shaping function, p(t), is nominally a rectangular pulse of unit amplitude with duration  $T_s$  and  $\phi_q[n]$  is the error in quantizing  $\phi[n]$ . The synthesized signal  $s_s(t)$  well approximates the desired phase modulated carrier signal for large M and a high switching frequency,  $F_s = 1/T_s$ . The ability to dynamically switch between multiple phases can be easily extended to synthesize a frequency at a small offset from the VCO frequency by applying a ramp signal as input to the  $\Sigma - \Delta$  modulator, with the appropriate slope.

This approach for phase modulation suffers from three critical issues—phase quantization noise (PQN), nonlinearity of digital-to-phase converter, and spectral images. Phase quantization noise arises due to the quantization process involved in the generation of output phases. Simple truncation results in white quantization noise and a flat power spectral density (PSD) stretching over a band  $[-F_s/2, F_s/2]$ around the carrier frequency, resulting in poor in-band signal-to-noise ratio (SNR) and error vector magnitude (EVM). Using a  $\Sigma - \Delta$  modulator to quantize  $\phi[n]$  imparts a high-pass shape [32] to  $\phi_a[n]$ , thereby suppressing the closein PQN and improving EVM. However, the PQN at offsets of  $F_s/2$  from the carrier frequency are amplified resulting in elevated out-of-band noise that can violate the spectral mask requirements for the transmitter. The PQN can be reduced by increasing the phase switching speed and/or by increasing the resolution of the digital phase interpolator. The discrete-time nature of the phase modulator causes spectral images to appear at integer multiples of  $F_s$ . The zeroth-order hold operation results in only modest filtering  $(\sin c^2(\cdot))$  of these images, and hence a high oversampling factor or interpolation is required to reduce them. At most, 5-10 dB of further suppression results from the LC tanks typically employed in a tuned power amplifier.

Due to a digital implementation of the modulator, this technique easily lends itself for quantization noise shaping, digital predistortion to compensate for errors due to PVT variation, dynamic element matching, and other similar digital techniques.

The design presented in [18] used four quadrature phases at the output of a frequency divider and digitally switched between them to realize phase modulation (Figure 3). Since only four-level quantization was used, the noise floor was quite high. With  $\Sigma - \Delta$  quantization noise shaping, the inband noise was lowered at the expense of large out-of-band noise (-25 dBr observed from the measured spectrum). While transmitting at 403.2 MHz, the measured FSK errors

FIGURE 4: Block diagram of phase quantization noise cancellation technique [20].

at 6 Mb/s data rate was 4.1% and 11.6% for 2-FSK and GFSK modulations, respectively.

In [7], a hybrid of many of the techniques mentioned earlier was designed for GSM and WCDMA. The outphasing angle was generated using an 8-bit phase interpolator, while phase modulation was generated by two-point modulation. However, it also used phase-to-digital converters in a negative feedback loop to correct for the nonlinearity of phase interpolators, thereby reducing the available bandwidth. Phase modulation techniques at 60 GHz are also being researched. Reference [34] implemented a novel method to obtain phase modulation at 60 GHz by digitally controlling the effective dielectric constant of a differential transmission line. This was achieved by digitally switching in and out a 4-bit bank of floating M6 and M7 strips placed underneath the transmission line, which leads to a digitally variable phase of S21. However, its dynamic performance under data transmission was not presented.

### 3. Quantization Noise Cancellation

PQN can be contrasted with the quantization noise added by baseband DACs in an I–Q architecture. In the latter, out-of-band quantization noise and spectral images of baseband DACs can be removed by baseband low-pass filters, although the total power consumption also gets increased. Furthermore, the noise generated by the low-pass filters adds on top of the contributions from the mixer and amplifiers in the transmit chain. Such a filter in a digital phase modulator will have to be RF band pass, requiring high Q passive components or a SAW filter. A PQN cancellation technique can, therefore, significantly improve the performance of the phase modulator.

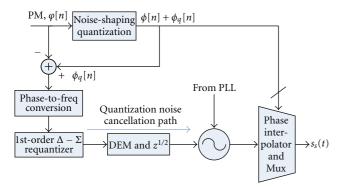

Through a second VCO control port, a quantization noise cancellation signal was added to the modulator output in [20], as shown in Figure 4. The required cancellation signal is obtained by first subtracting the input signal,  $\phi[n]$ , from the quantized signal,  $\phi[n] + \phi_q[n]$ . Thus, the quantized phase data  $\phi[n] + \phi_q[n]$  is applied through the digital-to-phase converter, while the PQN cancellation signal of  $-\phi_q[n]$  is applied through a cancellation path through the VCO.

In the cancellation path, frequency of the VCO can be controlled in a straightforward manner through an analog

FIGURE 5: Eye diagram of the transmitted signal.

control signal, or through a digital word in the case of a digitally controlled oscillator. Its phase, on the other hand, is the outcome of an integration of the resultant frequency. Since the cancellation signal is a phase quantity, while the VCO input port controls its frequency, the required cancellation phase is differentiated,  $(1-z^{-1})$  to obtain an equivalent VCO frequency deviation. It must also be attenuated by VCO control voltage-to-frequency gain,  $K_{\text{VCO}}$ .

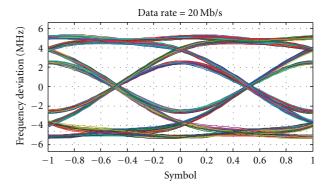

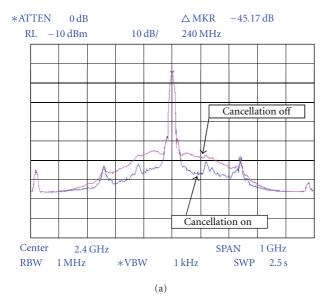

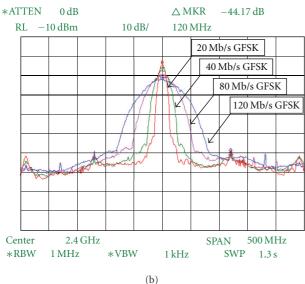

In [20], a state-of-the-art implementation of PQN cancellation was presented on a 2.4 GHz wide-bandwidth openloop GFSK transmitter IC. The phase cancellation path was implemented by adding a second VCO port to control a 4-bit capacitor bank, with DEM logic incorporated in the selection process. Figure 5 shows the GFSK transmitted eye diagram at 20 Mb/s GFSK modulation. Figure 6(a) shows 9 dB improvement in the measured output spectrum, after enabling the phase noise cancellation technique. The corresponding GFSK transmitted modulation rms error is 3.2% rms at 20 Mb/s. The wide-bandwidth capability of the transmitter is demonstrated in Figure 6(b), which shows overlaid spectrum of transmitter output under 20, 40, 80, and 120 Mb/s rates.

It should be noted that the normal functioning of the PLL is not impacted by the cancellation path. The cancellation signal at the VCO input port goes through the same transfer function as seen by the VCO phase noise, resulting in its high-pass filtering. The crucial difference being that, as opposed to VCO phase noise, the high-frequency content of the cancellation signal is a desired signal which lowers the quantization noise added from phase interpolator input. It may be perceived that since the low-frequency content of the cancellation signal is filtered out, it will degrade the efficacy of the technique. But, since quantization noise is already low at these frequencies, this results in negligible loss in effectiveness.

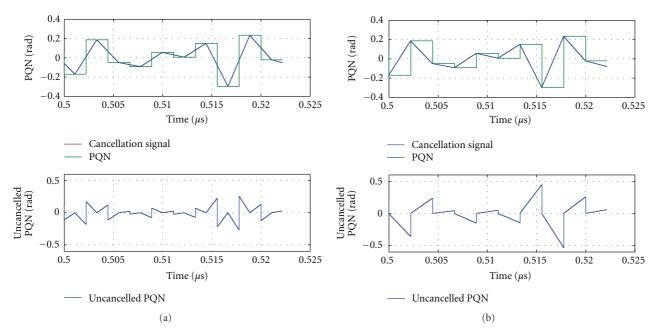

One of the subtle features of the cancellation path is the implication of discrete-time differentiation applied to obtain the required VCO frequency deviation. The integration of frequency inherent in a VCO is, on the other hand, continuous. Consider the case of rectangular pulse shape for the input phase and cancellation signal, where both of them are applied at a frequency,  $F_s = 1/T_s$ . Since the cancellation signal is updated every  $T_s$  time period, while VCO frequency is continuously being integrated, perfect cancellation is

FIGURE 6: Transmitter output spectrum (a) with noise cancellation ON and OFF; (b) under high speed data transmission [20].

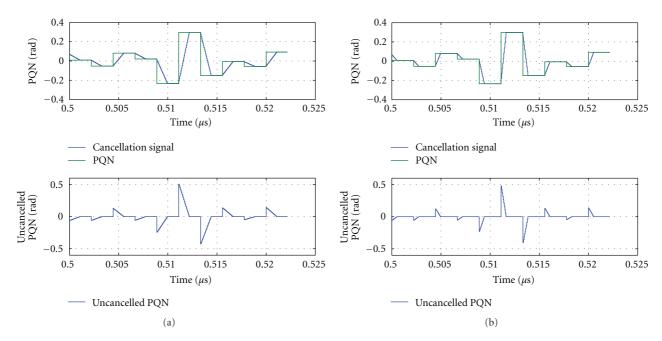

obtained only at the end of each time period, which is not very effective. Figure 8(b) depicts the timing diagram of phase quantization noise, the applied cancellation signal, and the uncancelled PQN. In [20], the cancellation signal was advanced by  $T_s/2$  to improve the effectiveness of noise cancellation. In the following subsections, results from detailed system simulation are used to illustrate this technique and bring up the associated trade-off, along with mathematical expressions for residual quantization noise. It will also be shown how the effectiveness of cancellation changes with a reduction in integration time and after quantization of the cancellation signal. Since the techniques are applicable to all forms of PQN shaping algorithm and for any resolution in the phase data path, a 2nd-order  $\Sigma - \Delta$  noise shaping with a 5-bit quantizer in the forward path is used to illustrate these

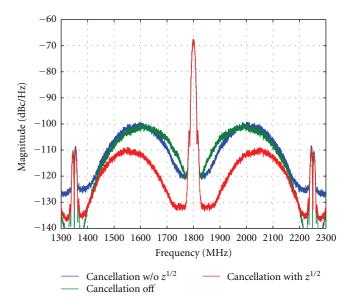

FIGURE 7: The simulated PSD of a GFSK-modulated signal showing PQN cancellation obtained with and without  $T_s/2$  advancement.

techniques. For all system simulations, input data is 20 Mb/s GFSK modulated.

3.1. Advancement of Cancellation Signal. The control voltage-to-frequency response of VCO to a cancellation signal was found to be low pass with a very high cutoff frequency ( $>F_s$ ). Hence, the cancellation frequency can be modeled as a rectangular pulse shape, and the cancellation phase becomes its integrated form. The transfer function of the uncancelled PQN can be expressed mathematically as

$$S_{\phi_n, \text{un-cancel}} = \text{NTF}_1(f) \times P_1(f) \times K_1(f),$$

(2)

where  $NTF_1(f)$  is the NTF of  $\Sigma - \Delta$  modulator quantizing  $\phi[n]$ ,  $P_1(f)$  models the pulse-shaping function of uncancelled  $\phi_q[n]$ , and  $K_1(f)$  models the effect of PQN cancellation. When PQN cancellation is off,  $P_1(f)$  is a sinc function,  $\sin(\pi f T s)/(\pi f T s)$ , representing the zeroth-order hold, and  $K_1(f)$  is 1. However, when a cancellation signal is applied through the VCO control port, two changes take place: (1) pulse shape of uncancelled quantization noise becomes saw-tooth and (2) magnitude of quantization noise becomes a first-order difference,  $(1 - z^{-1})$  of the initial quantization noise. These changes can be easily observed in the timing plot of Figure 8(b). As a result,  $P_1(f)$ , for a saw-tooth pulse shape, attains a DC value of -6 dB and  $K_1(f)$  becomes  $4 \times \sin^2(\pi f T s)$ . Saw-tooth pulse shape for PQN and the additional first-order noise shaping results in lower quantization noise at low frequencies, but higher noise at high frequencies (Figure 7). Hence noise cancellation is limited to frequencies below 40 MHz offset; while it increased by 2 dB at higher offset frequencies due to the additional firstorder noise shaping.

In order to improve the PQN cancellation mechanism, the cancellation signal can be advanced by  $T_s/2$ . As a result, the residual quantization noise rises to only half of the value

FIGURE 8: Timing diagram for PQN cancellation technique for (a)  $T_s/2$  advancement in cancellation signal and (b) no advancement in cancellation signal.

attained in the earlier case and afterwards its sign gets flipped (Figure 8(a)). Hence,  $P_1(f)$  has a zero at DC and  $K_1(f)$  is reduced by 6 dB. The combined effect of these two changes is a reduction in peak quantization noise by 10 dB, along with a maximum improvement of 17 dB, at a lower frequency (Figure 7).  $P_1(f)$  and the expression of uncancelled PQN,  $S_{\phi_n, \text{un-cancel}}(f)$ , for the three cases are plotted in the appendix. It should be noted that half-period advancement results in the highest achievable noise cancellation, compared to other values for signal advancement.

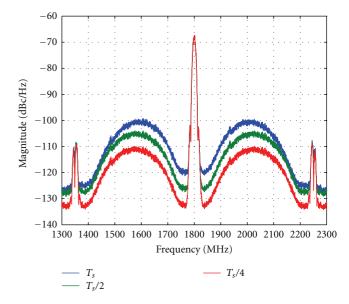

3.2. Reduction in Integration Time. Further improvement in PQN cancellation can be obtained by using a return-to-zero (RZ) DAC or an equivalent DCO to control the deviations in VCO frequency. In this case, integration of frequency input to the VCO is performed for a shorter duration of time, and hence perfect phase cancellation is obtained for a longer duration as opposed to one time instant. The required frequency deviation must also be increased in proportion to the reduction in integration time, such that the phase accumulated in one time period equals the required cancellation phase value. Figures 9(a) and 9(b) depict the time waveforms for the cases when integration time is reduced to  $T_s/2$  and  $T_s/4$ , respectively.

The resultant improvement in PQN cancellation is 6 dB for an integration time of  $T_s/2$  as shown in Figure 10. If the integration time is reduced further while simultaneously increasing the cancellation frequency signal, output PQN reduces by 6 dB for each octave reduction in integration time. In the limit of an impulse in frequency cancellation signal, perfect cancellation is obtained at all times. Since shorter integration time requires a larger frequency deviation from the VCO, there exists a trade-off between noise cancellation

and VCO frequency deviation. The minimum integration time and the resultant noise cancellation are limited by the maximum frequency deviation that can be linearly obtained from the VCO. For instance, for a maximum achievable frequency deviation of 100 MHz and a 4-bit phase interpolator, the maximum cancellation phase required is 0.4 radians, and hence the minimum integration time allowed becomes 625 ps.

3.3. Combination of Cancellation Signal Advancement and Reduction in Integration Time. The improvement in noise cancellation can be further increased by combining both signal advancement and reduction in integration time. When integration time is reduced to  $T_s/2$ , the optimal signal advancement changes from  $T_s/2$  to  $T_s/4$  so that the peak magnitude of PQN splits equally in its positive and negative cycle.

In general, the optimal clock advancement reduces by a factor of 2 when the integration time is reduced by a factor of 2. The PSD of the output signal when  $T_s/4$  clock advancement and  $T_s/2$  integration time are used is plotted in Figure 12. For comparison, PSD plots for zero clock advance and  $T_s$  integration time and  $T_s/2$  clock advance and  $T_s/2$  integration time are also plotted. The peak PQN has reduced by an additional amount of 10 dB due to simultaneous application of the two techniques.

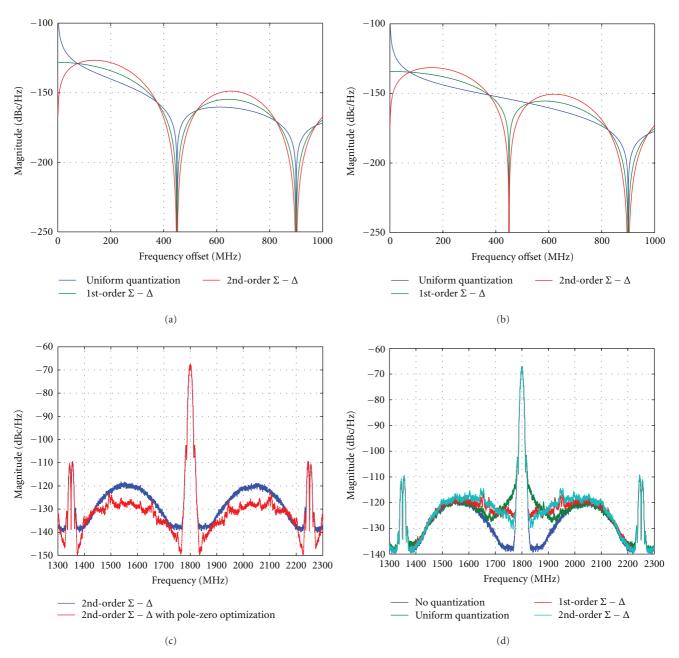

3.4. Optimized Modulator for PQN Shaping. A second-order  $\Sigma - \Delta$  modulator results in excessive quantization noise at a frequency offset of  $F_s/2$ . This increase can lead to spectral mask violation. By including a pair of complex poles in the NTF [35], the high-frequency noise can be reduced at the expense of higher noise at low frequencies. The improvement in noise reduction after the inclusion of a pair of complex

FIGURE 9: Timing diagram for PQN cancellation technique for (a) integration time of  $T_s/2$  and (b) integration time of  $T_s/4$ , within each time period.

poles in the NTF is depicted in Figure 11(c). In addition, the low frequency noise degradation observed in 2nd-order  $\Sigma$  –  $\Delta$  modulator due to the advancement of cancellation signal has also improved resulting in lower noise for the optimized NTF.

3.5. Quantization of Cancellation Signal. Since, in a digital implementation of the cancellation path, the frequency data fed to the second VCO port must go through a quantization process, its impact also requires a careful attention. If the frequency data is uniformly quantized within the input dynamic range of VCO control port, its quantization noise has a constant PSD between  $-F_s/2$  and  $+F_s/2$ . Within the loop bandwidth of PLL, this noise will be tracked by the negative feedback loop and its impact will be nullified. Outside the loop bandwidth, VCO integrates this noise due to frequency to phase conversion, and hence an amplified version will appear at its output. Mathematically, the PSD of quantization noise at VCO output can be expressed as

$$S_{\varphi_{n,\text{freq}}}(f) = \frac{1}{4} \frac{\Delta^2}{12F_s} \sin c^2 \left(\frac{\pi f}{F_s}\right) \frac{K_{\text{VCO}}^2}{f^2} \text{NTF}_2(f), \qquad (3)$$

where  $\Delta$  is quantization step size in VCO control voltage,  $F_s$  is sampling frequency, f is frequency offset from carrier,  $K_{\text{VCO}}$  is VCO gain, and NTF<sub>2</sub>(f) is noise transfer function. For an example case with  $K_{\text{VCO}}$  of 100 MHz/V,  $F_s$  of 450 MHz, and  $\Delta$  of 41 mV (5-bit quantization), the calculated output noise is plotted in Figure 11(a) for uniform quantization and 1st-order and 2nd-order  $\Sigma - \Delta$  noise shaping. If the integration time is reduced to  $T_s/2$ , the expression for quantization noise changes to (Figure 11(b))

$$S_{\varphi_{n,\text{freq}}}(f) = \frac{1}{16} \frac{\Delta^2}{12F_s} \sin c^2 \left(\frac{\pi f}{2 \times F_s}\right) \frac{K_{\text{VCO}}^2}{f^2} \text{NTF}_2(f). \quad (4)$$

FIGURE 10: The simulated PSD of a GFSK-modulated signal showing PQN reduction with decrease in integration time.

Clearly, for both cases, the noise at VCO output will suffer from both EVM and ACPR degradation if uniform quantization is applied. In order to cancel the pole in the VCO transfer function, a first- or higher-order zero is required in the NTF of the cancellation signal quantizer. First-order noise shaping results in a flat noise PSD close to DC, while second-order noise shaping has a zero at DC in its noise transfer function. Hence, the noise shaping employed must be of at least second order.

FIGURE 11: Plot of analytical expression for output quantization noise due to quantization in the cancellation path for (a) integration time of  $T_s$  and (b) integration time of  $T_s$ /2. The simulated PSD of a GFSK-modulated signal showing (c) PQN reduction with poles in the NTF of phase path and (d) impact of quantization in the cancellation path using three types of quantizers.

The PSD of a GFSK-modulated signal with quantized cancellation signal is shown in Figure 11(d). Clearly, the residual quantization noise matches the behavior expected for uniform, 1st-order and 2nd-order  $\Sigma - \Delta$  noise shaping in the cancellation path, from the preceding analysis.

The overall improvement obtained from the cancellation technique can now be compared with the case when it is off. From Figure 11(d), it can be observed that the peak quantization noise is  $-128\,\mathrm{dBc/Hz}$ , which is 27 dB lower than the modulator with cancellation off (Figure 7).

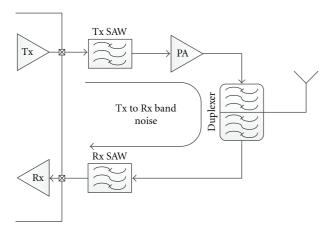

#### 4. Receive Band Noise

In a Frequency division duplexing (FDD) system, both transmitter and receiver are operational simultaneously. For instance, in the LTE-FDD frequency planning Tx-Rx separation varies from 30 MHz in band XII (700 MHz) to 400 MHz in band X (Tx in 1710–1770 MHz and Rx in 2110–2170 MHz). Due to a finite duplexer Tx to Rx isolation, the transmitter noise in the receive frequency band leaks into the receiver, which can desensitize the receiver (Figure 13). If the transmitter noise in the receive band is  $-160\,\mathrm{dBc/Hz}$  and

FIGURE 12: The simulated PSD of a GFSK-modulated signal showing PQN reduction with optimized cancellation signal advancement and integration time.

FIGURE 13: Diagram showing Tx signal leakage in a conventional transceiver.

the duplexer Tx-to-Rx isolation in the receive band is 47 dB, then noise power at LNA input is given by

$$N_{\rm Rx} = -160 \,\mathrm{dBc}/Hz - 47 \,\mathrm{dB} + (24 + 1.5 + 1.0) \,\mathrm{dBm}, \quad (5)$$

assuming 24 dBm power at the antenna, 1.5 dB of duplexer Tx insertion loss, and 1.0 dB of antenna switch insertion loss. As a result of this additional noise at LNA input, the receiver noise figure can degrade by 0.5 dB if it was 3 dB in the beginning (without including switch and duplexer loss). In the phase path of a polar transmitter, this noise is composed of PLL phase noise and quantization noise added by the digital phase modulator. In practice, the phase noise of the PLL can be reduced to meet the requirement in the receive band. Consequently, the quantization noise of the modulator becomes the dominant source of noise, requiring additional filtering by off-chip components.

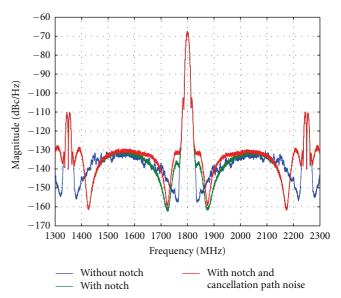

FIGURE 14: The simulated PSD of a GFSK-modulated signal before and after the inclusion of a notch at 80 MHz offset. Degradation by 2 dB is observed due to quantization noise in the cancellation path.

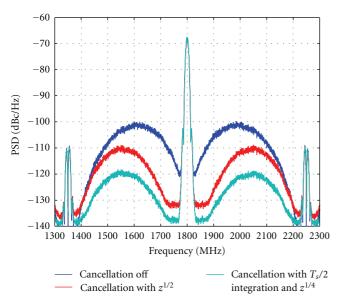

However, the additional components can be avoided by positioning a quantization noise transfer function (NTF) notch at the receive band frequency. The quantizer of the phase modulator can be modified to include a zero in the quantization noise transfer function. Due to high-pass shaping of quantization noise, the 30–70 MHz Rx band offset poses less design challenge. Improvement in noise at the receive band due to NTF notch at 80 MHz is shown in Figure 14. The resolution of digital phase modulator was increased from 5 bits to 6 in this simulation, to lower its noise contribution. The modulator also employs PQN cancellation technique with  $T_s/4$  advancement in the cancellation path for an integration time of  $T_s/2$ . For comparison, the transfer function without the notch, but including the same PQN cancellation technique, is also shown. An improvement of 12 dB is obtained due to the notch in the transfer function. When the cancellation path is quantized to 5 bits, the noise performance degrads by 2 dB due to the additional noise of the cancellation path. The ACPR performance of the modulator is better than 62 dB in the out-of-band region which meets the requirement of both LTE and WiMAX. Although the ACPR specification can be met with a lower resolution, at least 4 bits are generally required to keep the frequency deviation in the cancellation path within a reasonable range.

#### 5. Conclusion

Transmitters for upcoming wireless standards, 60 GHz band, and software-defined radio require a digital wide-bandwidth phase modulator for a reduction in power consumption and for achieving maximum flexibility in transmission. Several circuit and system techniques for designing such a modulator were reviewed in this paper. Signal processing details of

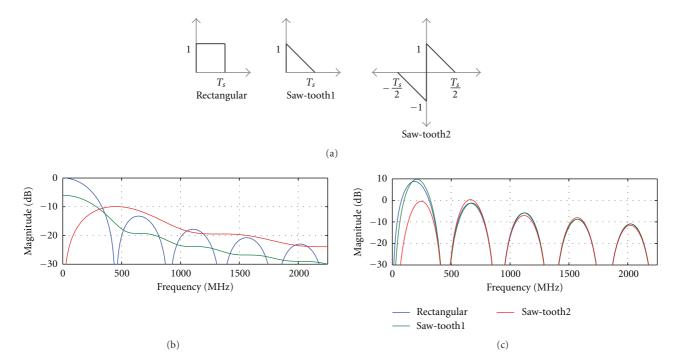

FIGURE 15: (a) Pulse shapes for rectangular, saw-tooth1, and saw-tooth2 functions. (b) Pulse-shaping function  $P_1(f)$  for rectangular, saw-tooth, and modified saw-tooth functions. (c) Calculated transfer function of uncancelled PQN for the three cases ( $T_s = 1/450 \,\text{MHz}$ ).

phase quantization noise cancellation were presented with emphasis on advancement of cancellation signal, reduction in integration time, and impact of quantization in the cancellation signal. In the final system, the residual PQN for a 2nd-order  $\Sigma-\Delta$  quantized digital phase modulator was lower by 27 dB. Inclusion of a noise transfer function notch was presented to meet the specification of receive band noise in a digital phase modulator.

## **Appendix**

Pulse-shaping function for a rectangular pulse, saw-tooth pulse (saw-tooth1), and modified saw-tooth pulse is obtained after advancing cancellation signal by  $T_s/2$  (saw-tooth2):

$$P_1(f)_{\text{rect}} = \sin c^2(\pi f T_s),$$

$$P_1(f)_{\text{saw-tooth1}} = \frac{1}{4\pi^2 f^2 T_s^2} \left( \left( 1 - \sin c(\pi f T_s) \right)^2 + 4 \right)$$

$$\times \sin c(\pi f T_s) \sin^2 \left( \frac{\pi f T_s}{2} \right),$$

$P_1(f)_{\text{saw-tooth2}} = \frac{4}{4\pi^2 f^2 T_s^2} (1 - \sin c(\pi f T_s))^2.$ (A.1)

For a 2nd-order  $\Sigma - \Delta$  modulator quantizing  $\phi[n]$ , NTF<sub>1</sub>(f) is given by

$$NTF_1(f) = 16 \times \sin^4(\pi f T_s).$$

(A.2)

$K_1(f)$ , which models the effect of noise cancellation, for the three cases can be written as

$$K_1(f)_{\text{rect}} = 1,$$

$$K_1(f)_{\text{saw-tooth1}} = 4 \times \sin^2(\pi f T_s),$$

$$K_1(f)_{\text{saw-tooth2}} = \frac{4 \times \sin^2(\pi f T_s)}{4}.$$

(A.3)

Figure 15(b) depicts the pulse-shaping functions  $P_1(f)_{\text{rect}}$ ,  $P_1(f)_{\text{saw-tooth1}}$ , and  $P_1(f)_{\text{saw-tooth2}}$ . Figure 15(c) depicts the calculated transfer function of uncancelled PQN  $P_1(f) \times \text{NTF}_1(f) \times K_1(f)$  for the three cases.

## Acknowledgment

This research was funded in parts by National Science Foundation awards ECCS-0824279 and ECCS-0955330.

#### References

- [1] V. Petrovic and W. Gosling, "Polar-loop transmitter," *Electronics Letters*, vol. 15, no. 10, pp. 286–288, 1979.

- [2] M. R. Elliott, T. Montalvo, B. P. Jeffries et al., "A polar modulator transmitter for GSM/EDGE," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 12, pp. 2190–2199, 2004.

- [3] T. Sowlati, D. Rozenblit, R. Pullela et al., "Quad-band GSM/GPRS/EDGE polar loop transmitter," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 12, pp. 2179–2189, 2004.

- [4] A. W. Hietala, "A quad-band 8PSK/GMSK polar transceiver," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 5, pp. 1133–1141, 2006.

- [5] Y. Akamine, S. Tanaka, M. Kawabe et al., "A polar loop transmitter with digital interface including a loop-bandwidth calibration system," in *Proceedings of the IEEE International Solid-State Circuits Conference: Digest of Technical Papers (ISSCC '07)*, pp. 348–349, San Francisco, Calif, USA, February 2007.

- [6] D. C. Cox, "Linear amplification with nonlinear components," *IEEE Transactions on Communications*, vol. 22, no. 12, pp. 1942–1945, 1974.

- [7] M. E. Heidari, M. Lee, and A. A. Abidi, "All-digital outphasing modulator for a software-defined transmitter," *IEEE Journal* of Solid-State Circuits, vol. 44, no. 4, Article ID 4804977, pp. 1260–1271, 2009.

- [8] T. A. D. Riley and M. A. Copeland, "A simplified continuous phase modulator technique," *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, vol. 41, no. 5, pp. 321–328, 1994.

- [9] N. M. Filiol, T. A. D. Riley, C. Plett, and M. A. Copeland, "An agile ISM band frequency synthesizer with built-in GMSK data modulation," *IEEE Journal of Solid-State Circuits*, vol. 33, no. 7, pp. 998–1008, 1998.

- [10] S. Pamarti, L. Jansson, and I. Galton, "A wideband 2.4-GHz delta-sigma fractional-N PLL with 1-Mb/s in-loop modulation," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 1, pp. 49– 62, 2004.

- [11] M. H. Perrott, T. L. Tewksbury III, and C. G. Sodini, "A 27-mW CMOS fractional-N synthesizer using digital compensation for 2.5-Mb/s GFSK modulation," *IEEE Journal of Solid-State Circuits*, vol. 32, no. 12, pp. 2048–2059, 1997.

- [12] M. Youssef, A. Zolfaghari, H. Darabi, and A. Abidi, "A low-power wideband polar transmitter for 3G applications," in *Proceedings of the IEEE International Solid-State Circuits Conference: Digest of Technical Papers (ISSCC '11)*, pp. 378–379, San Francisco, Calif, USA, February 2011.

- [13] R. B. Staszewski, J. L. Wallberg, S. Rezeq et al., "All-digital PLL and transmitter for mobile phones," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 12, pp. 2469–2482, 2005.

- [14] S. A. Yu and P. Kinget, "A 0.65-V 2.5-GHz fractional-N synthesizer with two-point 2-Mb/s GFSK data modulation," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 9, Article ID 5226689, pp. 2411–2425, 2009.

- [15] W. W. Si, D. Weber, S. Abdollahi-Alibeik et al., "A single-chip CMOS bluetooth v2.1 radio SoC," *IEEE Journal of Solid-State Circuits*, vol. 43, no. 12, Article ID 4684630, pp. 2896–2904, 2008.

- [16] K. C. Peng, C. H. Huang, C. J. Li, and T. S. Horng, "High-performance frequency-hopping transmitters using two-point delta-sigma modulation," *IEEE Transactions on Microwave Theory and Techniques*, vol. 52, no. 11, pp. 2529–2535, 2004.

- [17] S. Lee, J. Lee, H. Park, K. Y. Lee, and S. Nam, "Self-calibrated two-point delta-sigma modulation technique for RF transmitters," *IEEE Transactions on Microwave Theory and Techniques*, vol. 58, no. 7, Article ID 5481987, pp. 1748–1757, 2010.

- [18] Y. H. Liu and T. H. Lin, "A wideband PLL-based G/FSK transmitter in 0.18 μm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 9, Article ID 5226692, pp. 2452–2462, 2009.

- [19] H. Mair and L. Xiu, "Architecture of high-performance frequency and phase synthesis," *IEEE Journal of Solid-State*

- Circuits, vol. 35, no. 6, pp. 835-846, 2000.

- [20] P. E. Su and S. Pamarti, "A 2.4 GHz wideband open-loop GFSK transmitter with phase quantization noise cancellation," *IEEE Journal of Solid-State Circuits*, vol. 46, no. 3, pp. 615–626, 2011

- [21] P. Y. Wang, J. H. C. Zhan, H. H. Chang, and H. M. S. Chang, "A digital intensive fractional-N PLL and all-digital self-calibration schemes," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 8, Article ID 5173739, pp. 2182–2192, 2009.

- [22] K. J. Wang, A. Swaminathan, and I. Galton, "Spurious tone suppression techniques applied to a wide-bandwidth 2.4 GHz fractional-N PLL," *IEEE Journal of Solid-State Circuits*, vol. 43, no. 12, Article ID 4684634, pp. 2787–2797, 2008.

- [23] E. Temporiti, G. Albasini, I. Bietti, and R. Castello, "A 700-kHz bandwidth ΣΔ fractional synthesizer with spurs compensation and linearization techniques for WCDMA applications," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 9, pp. 1446–1454, 2004.

- [24] M. Gupta and B. S. Song, "A 1.8-GHz spur-cancelled fractional-N frequency synthesizer with LMS-based DAC gain calibration," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 12, pp. 2842–2851, 2006.

- [25] A. Swaminathan, K. J. Wang, and I. Galton, "A wide-bandwidth 2.4 GHz ISM-band fractional-N PLL with adaptive phase-noise cancellation," *IEEE Journal of Solid-State Circuits*, vol. 42, no. 12, pp. 2639–2650, 2007.

- [26] S. E. Meninger and M. H. Perrott, "A 1-MHZ bandwidth 3.6-GHz 0.18-\(\mu\mathrm{m}\) CMOS fractional-N synthesizer utilizing a hybrid PFD/DAC structure for reduced broadband phase noise," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 4, pp. 966–980, 2006.

- [27] P. E. Su and S. Pamarti, "A 2-MHz bandwidth Δ—Σ fractional-N synthesizer based on a fractional frequency divider with digital spur suppression," in *Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC '10)*, pp. 413–416, Anaheim, Calif, USA, May 2010.

- [28] H. Hedayati, W. Khalil, and B. Bakkaloglu, "A 1 MHz bandwidth, 6 GHz 0.18  $\mu$ m CMOS type-I  $\delta\sigma$  fractional-N synthesizer for WiMAX applications," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 12, Article ID 5342360, pp. 3244–3252, 2009.

- [29] M. Nilsson, S. Mattisson, N. Klemmer et al., "A 9-band WCDMA/EDGE transceiver supporting HSPA evolution," in *Proceedings of the IEEE International Solid-State Circuits Conference: Digest of Technical Papers (ISSCC '11)*, pp. 366–367, San Francisco, Calif, USA, February 2011.

- [30] C. M. Hsu, M. Z. Straayer, and M. H. Perrott, "A low-noise wide-BW 3.6-GHz digital ΔΣ fractional-N frequency synthesizer with a noise-shaping time-to-digital converter and quantization noise cancellation," *IEEE Journal of Solid State Circuits*, vol. 43, no. 12, Article ID 4684627, pp. 2776–2786, 2008.

- [31] M. Lee, M. E. Heidari, and A. A. Abidi, "A low-noise wideband digital phase-locked loop based on a coarse-fine time-to-digital converter with subpicosecond resolution," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 10, pp. 2808–2816, 2009.

- [32] M. Zanuso, S. Levantino, C. Samori, and A. Lacaita, "A 3MHz-BW 3.6 GHz digital fractional-N PLL with sub-gatedelay TDC, phase-interpolation divider, and digital mismatch cancellation," in *Proceedings of the IEEE International* Solid-State Circuits Conference: Digest of Technical Papers (ISSCC '10), pp. 476–477, San Francisco, Calif, USA, February 2010.

- [33] R. B. Staszewski, K. Muhammad, D. Leipold et al., "All-digital TX frequency synthesizer and discrete-time receiver for Bluetooth radio in 130-nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 12, pp. 2278–2291, 2004.

- [34] T. LaRocca, J. Liu, F. Wang, and F. Chang, "Embedded DiCAD linear phase shifter for 57–65 GHz reconfigurable direct frequency modulation in 90nm CMOS," in *Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC '09)*, pp. 219–222, Boston, Mass, USA, June 2009.

- [35] *Delta-SigmaToolBox*,http://www.mathworks.com/matlab-cen-tral/fileexchange/19.

Submit your manuscripts at http://www.hindawi.com