Hindawi Publishing Corporation Mathematical Problems in Engineering Volume 2014, Article ID 731574, 9 pages http://dx.doi.org/10.1155/2014/731574

## Research Article

# An Improved Phase Disposition SPWM Strategy for Cascaded Multilevel Inverter

# Jinbang Xu,<sup>1</sup> Zhizhuo Wu,<sup>1</sup> Xiao Wu,<sup>2</sup> Fang Wu,<sup>1</sup> and Anwen Shen<sup>1</sup>

<sup>1</sup> Huazhong University of Science and Technology, Wuhan, Hubei 430074, China

Correspondence should be addressed to Anwen Shen; sawyi@mail.hust.edu.cn

Received 21 August 2013; Revised 2 December 2013; Accepted 4 December 2013; Published 19 March 2014

Academic Editor: Tao Li

Copyright © 2014 Jinbang Xu et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

The Carrier Phase Shifted (CPS) strategy is conventional for cascaded multilevel inverter, because it can naturally ensure all cascaded cells to output balanced power. However, in point of spectra of the output line voltage, CPS is suboptimal to Phase Disposition (PD) strategy, because the latter can not naturally ensure power balance. This paper presents an improved PD strategy, inspiration from the disposition of CPS strategy triangle carriers. Just reconstructing the triangle carriers of PD strategy, it can not only reserve the waveform quality of the line voltage to be optimal, but also naturally ensure the output power of each cascaded cells to be balanced.

#### 1. Introductions

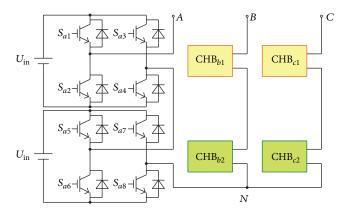

The cascaded multilevel inverters are widely implemented in the high power AC drivers and power management systems with a medium or high voltage level [1–5]. The structure of the cascaded multilevel inverters is shown in Figure 1. It is constructed with several full bridge inverters with the same topology. The advantages of the cascaded multilevel inverters include being simple to control, being easy in output voltage level extension, modular design and implementation, and the fault tolerance control realization [6–10].

The Carriers Phase Shift (CPS) control is one of the conventional control schemes employed in the cascaded multilevel inverters. The control signals for each cascaded unit are generated by comparison between N (N is the number of cascaded units) triangle carrier and the modulated signal. The carrier waveform is chosen with a phase shift of 360/N degree. The fundamental component amplitude of each unit driving signal is the same. So the output power of each unit is balanced [11–14].

Except for the CPS control method, Phase Disposition (PD), Phase Opposite Disposition (POD), and Alternative Phase Opposite Disposition (APOD) are three other carry deposition control strategies used in multilevel inverters [15]. In [10], under the condition of same switching frequency, the output line voltage waveforms with both the CPS and

PD control methods are compared. It is indicated that the experiment result with the PD control method is better than that with the CPS control. However, PD cannot achieve power balance spontaneously. According to [16], each cascaded unit outputs the PWM under the previous setting cycle and the output power will be balanced after N/2 output periods. This balance strategy is easy, but the power balance time increases with the cascade units increasing.

To shorten the time of power balance, this paper proposes an improved PD control strategy. By improving the carrier wave for modulation, the output power of each cascaded unit can be balanced in an output cycle, and the switching frequency of each switch tube is equal to each other at the same time. The output line voltage waveform quality is maintained to be optimized as that of the PD control. An experimental prototype of a 5 kW three-phase cascaded multilevel inverter is designed to verify the validity of this improved PD control.

### 2. CPS and PD Control Strategy

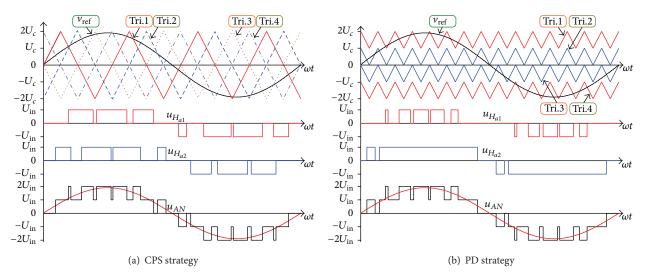

2.1. Principle. The principle of the CPS control strategy based on a two-unit cascaded multilevel inverter is shown in Figure 2(a). The triangular carrier of tri.1~tri.4 and the reference signal  $\nu_{\rm ref}$  are combined to generate the control

<sup>&</sup>lt;sup>2</sup> Guangdong University of Technology, Guangzhou, Guangdong 510006, China

FIGURE 1: Cascaded five-level inverter.

signal for the bridges. The triangular carrier signal is arranged with 90 degree phase shift between the adjacent ones. The control signal modulation is performed with the following principle.

The drive signal for  $H_{a1}$  is generated by comparing  $v_{\rm ref}$  with tri.1 and tri.3. And the drive signal for  $H_{a2}$  is generated by comparing  $v_{\rm ref}$  with tri.2 and tri.4. As is shown in Figure 2(a), the  $u_{Ha1}$  and  $u_{Ha2}$  are the output voltage of the full bridges, respectively. And the  $u_{AN}$  is the output voltage of phase A.

In Figure 2(b), the modulation principle of the PD control strategy is illustrated. Like that of CPS, a combination of four triangular carrier signals is implemented with the same phase but different amplitude range. The amplitude of the carrier is distributed evenly in the whole carrier amplitude. The modulation of PD strategy is comparing the  $v_{\rm ref}$  with tri.1 and tri.4 to obtain the drive signal of  $H_{a1}$  and with tri.2 and tri.3 to obtain the drive signal of  $H_{a2}$ . In Figure 2(b), the full bridge output voltage of each inverter unit is shown as  $u_{Ha1}$  and  $u_{Ha2}$ . And the output voltage of phase A is shown as  $u_{AN}$ .

It is obvious that the switching frequencies of the two units are identical in the CPS strategy. But with the PD strategy, the drive signal shows much difference between the two units. The switching frequencies of the two bridges are different. And at the same time, when the PD strategy is employed, the amplitudes of fundamental component in the output voltage of the two units are different. This means that the output power of the two units is not balanced. So when the PD strategy is directly implemented in the cascaded multilevel inverter, the output power and the switching frequency of the cascaded units are not the sameThis brings a lot of practical design problems. The rated power and the cooling design of the power units is hard to determine.

2.2. Voltage Harmonics Comparison. With the different triangular carrier waveform used in the two modulation strategies of PD and CPS, the output voltage of phase A,  $u_{AN}$  produced is different. The voltage harmonic is analyzed to reveal the difference and the Flourier transformation is implemented to illustrate the spectral characteristics of the two voltage waveforms.

The modulation of the SPWM control is performed by comparison between the reference signal and the triangular carrier. The Flourier expression of the phase voltage can be divided into three parts: The first part is the integer order harmonics of the reference signal; the second part is the integer order harmonics of the triangular carrier signal; the third part is the sideband harmonics which are centralized to integer order harmonics of the carrier signal.

The extended Flourier expression of the voltage waveform is shown in

$$u_{AN}(t) = \frac{A_{00}}{2} + \sum_{n=1}^{\infty} \left[ A_{0n} \cos \left( n\omega_o t \right) + B_{0n} \sin \left( n\omega_o t \right) \right] + \sum_{m=1}^{\infty} \sum_{n=-\infty}^{\infty} \left[ A_{mn} \cos \left( n\omega_o t + m\omega_c t \right) + B_{mn} \sin \left( n\omega_o t + m\omega_c t \right) \right],$$

(1)

in which  $\omega_o$  and  $\omega_c$  are the frequency of the sinusoidal reference signal and the triangular carrier, m and n are integer, and  $A_{00}$  is the dc component, while  $A_{mn}$  and  $B_{mn}$  are the harmonic coefficient of the integer order harmonics and the sideband harmonics.

Then the output voltage of PD modulation is analyzed with Double Fourier series expansion as follows:

$$\begin{split} u_{\text{PD-AN}}(t) = &N M_r U_{\text{in}} \sin \left(\omega_o t\right) \\ &+ \sum_{m=1}^{\infty} \sum_{n=-\infty}^{+\infty} \left\{ B_{p1}\left(m,n\right) \right. \\ &\quad \times \sin \left[ \left(2m-1\right) \omega_c t + 2n \omega_o t \right] \right\} \\ &\quad + \sum_{m=1}^{\infty} \sum_{n=-\infty}^{\infty} \left\{ C_{p1}\left(m,n\right) \right. \\ &\quad \times \sin \left[ 2m \omega_c t + \left(2n-1\right) \omega_o t \right] \right\}, \end{split}$$

in which N is the cascaded unit number and  $U_{\rm in}$  is the input voltage. Assuming that  $U_{om}$  is the amplitude of the fundamental component in the output voltage of each unit, the voltage transfer ratio of each unit  $M_r$  can be calculated as

$$M_r = \frac{U_{om}}{U_{in}}. (3)$$

The  $B_{p1}(m, n)$  and  $C_{p1}(m, n)$  in (2) are the amplitude of the odd harmonics and the even harmonics

FIGURE 2: Modulation of CPS and PD control strategy.

(4)

of the reference signal. The value can be expressed as follows:

$B_{v1}(m,n)$

$$\sum_{k=0}^{N} \left\{ \frac{4U_{\text{in}}(-1)^{k} J_{(2k+1)} \left[ (2m-1) \pi N M_{r} \right]}{\pi^{2} (2m-1)} \cdot \left[ \frac{1}{2n-2k-1} \times \left( -\sin \left[ (2n-2k-1) \frac{\pi}{2} \right] + 2 \sum_{h=0}^{N-1} \left\{ \cos (h\pi) \cdot \sin \left[ (2n-2k-1) \times \arccos \left( \frac{h}{N M_{r}} \right) \right] \right\} \right) + \frac{1}{2n+2k+1} \times \left( -\sin \left[ (2n+2k+1) \frac{\pi}{2} \right] + 2 \sum_{h=0}^{N-1} \left\{ \cos (h\pi) \cdot \sin \left[ (2n+2k+1) \frac{\pi}{2} \right] \right\} \cdot \sin \left[ (2n+2k+1) \cdot \sin \left[ (2n+2k+1) \times \arccos \left( \frac{h}{N M_{r}} \right) \right] \right\} \right) \right\} ,$$

$C_{p1}(m,n) = \frac{U_{\text{in}}}{\pi m} J_{(2n-1)}(2m\pi N M_r).$

In accordance with the phase voltage, the line voltage  $u_{PD\_AB}$  can be expressed as follows:

$$u_{\text{PD\_AB}}(t) = \sqrt{3}NM_{r}U_{\text{in}}\sin\left(\omega_{o}t + \frac{\pi}{6}\right)$$

$$+ \sum_{m=1}^{\infty} \sum_{n=-\infty}^{+\infty} \left\{ B_{l1}(m,n) \right\}$$

$$\times \sin\left[ (2m-1)\omega_{c}t \right]$$

$$+ 2n\omega_{o}t - \frac{2n\pi}{3} \right]$$

$$+ \sum_{m=1}^{\infty} \sum_{n=-\infty}^{\infty} \left\{ C_{l1}(m,n) \right\}$$

$$\times \sin\left[ 2m\omega_{c}t + (2n-1)\omega_{o}t \right]$$

$$- \frac{(2n-1)\pi}{3} \right]$$

In which,  $B_{l1}(m, n)$  and  $C_{l1}(m, n)$  are the amplitude of the line voltage harmonics. The value can be express in (6) and (7)

$$B_{l1}(m,n) = 2\sin\left(\frac{2n\pi}{3}\right) \cdot B_{p1}(m,n),$$

(6)

$$C_{l1}(m,n) = 2 \sin \left[ \frac{(2n-1)\pi}{3} \right] \cdot C_{p1}(m,n).$$

(7)

With the same principle, the phase voltage of CPS control strategy  $u_{\rm CPS\_AN}$  can be expanded as follows:

$$u_{\text{CPS\_AN}}(t)$$

$$= NM_r U_{\text{in}} \sin (\omega_o t)$$

$$+ \sum_{m=1}^{\infty} \sum_{n=-\infty}^{\infty} \left\{ B_{p2}(m, n) \sin \left[ 2mN\omega_c' t + (2n-1)\omega_o t \right] \right\},$$

(8)

in which,  $B_{p2}(m,n)$  is the amplitude of the integer multiple harmonics with carrier frequency. The value can be expressed:

$$B_{p2}(m,n) = \frac{2U_{\text{in}}}{\pi m} J_{(2n-1)}(m\pi N M_r).$$

(9)

And the output line voltage  $u_{\text{CPS\_AB}}$  can be expressed as follows:

$$\begin{aligned} u_{\text{CPS\_AB}}(t) &= NM_r U_{\text{in}} \sin \left( \omega_o t \right) \\ &+ \sum_{m=1}^{\infty} \sum_{n=-\infty}^{\infty} \left\{ B_{l2} \left( m, n \right) \right. \\ &\left. \times \sin \left[ 2mN\omega_c' t + (2n-1) \left( \omega_o t - \frac{\pi}{3} \right) \right] \right\}, \end{aligned}$$

$$(10)$$

in which

$$B_{l2}(m,n) = 2\sin\left[\frac{(2n-1)\pi}{3}\right] \cdot B_{p2}(m,n).$$

(11)

It is shown, through the comparison of (5) and (8), that when the following situation is satisfied, the major harmonics of the two control methods will appear with the same frequency

$$\omega_c = 2N\omega_c'. \tag{12}$$

When m is 1, the harmonics of PD and CPS control with the highest amplitude are around the carrier frequency  $\omega_c$ . The high frequency filter design can be directly determined by the amplitude of the harmonic at this frequency. So the carrier frequency harmonics are compared. And for

convenience, the amplitude with the carrier frequency of both two control strategies is defined as follows:

$$H_{\text{PD\_AN}} = \frac{\sqrt{\sum_{n=1}^{10} B_{p1}^{2}(1, n)}}{NM_{r}U_{\text{in}}},$$

$$H_{\text{PD\_AB}} = \frac{\sqrt{\sum_{n=1}^{10} B_{l1}^{2}(1, n)}}{\sqrt{3}NM_{r}U_{\text{in}}},$$

$$H_{\text{CPS\_AN}} = \frac{\sqrt{\sum_{n=1}^{10} B_{p2}^{2}(1, n)}}{NM_{r}U_{\text{in}}},$$

$$H_{\text{CPS\_AB}} = \frac{\sqrt{\sum_{n=1}^{10} B_{l2}^{2}(1, n)}}{\sqrt{3}NM_{r}U_{\text{in}}}.$$

(13)

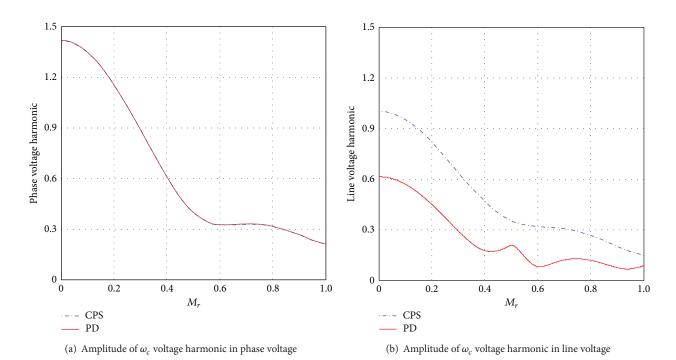

Taking two unit cascaded inverters as an example (N = 2), (13) is calculated to obtain the relationship between the amplitude of the carrier harmonic and the voltage transfer ratio  $M_r$  in the range of [0, 1]. The result is shown in Figure 3.

Figure 3(a) shows that the phase voltage harmonics produced by the two control strategies are with the same amplitude. And in Figure 3(b), it is indicated that with both the two control schemes, the line voltage of is better than the phase voltage. This can be verified by (6) and (11). For that when n is an integral multiple of 3 in (6), the harmonic amplitude is 0, the harmonics with these frequencies are naturally eliminated in the line voltage. The same situation can be observed in (11), assuming that (2n-1) is an integral multiple of 3.

And in Figure 3(b), the line voltage of the PD control method contains fewer harmonic than that of the CPS control. For a multilevel cascaded inverter implementation in the three-phase-three-wire system, the quality of the line voltage is an important performance requirement. And PD control method shows obvious advantages with this consideration.

## 3. Improved PD Control

As is analyzed above, although the line voltage quality of PD control is better than that of a CPS control, the PD control cannot be directly implemented. Because the disadvantages of the PD control method are unbalanced output power and different switching frequencies of the cascaded units. The PD control method has to be improved to be implemented in the multi-level cascaded inverter.

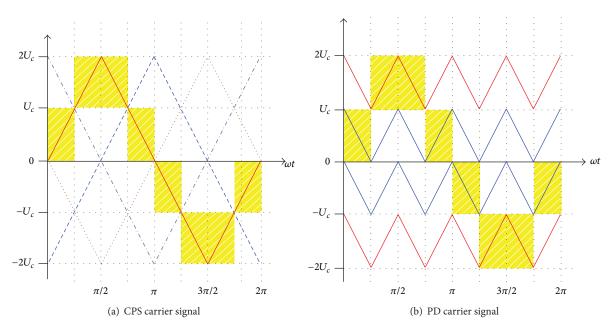

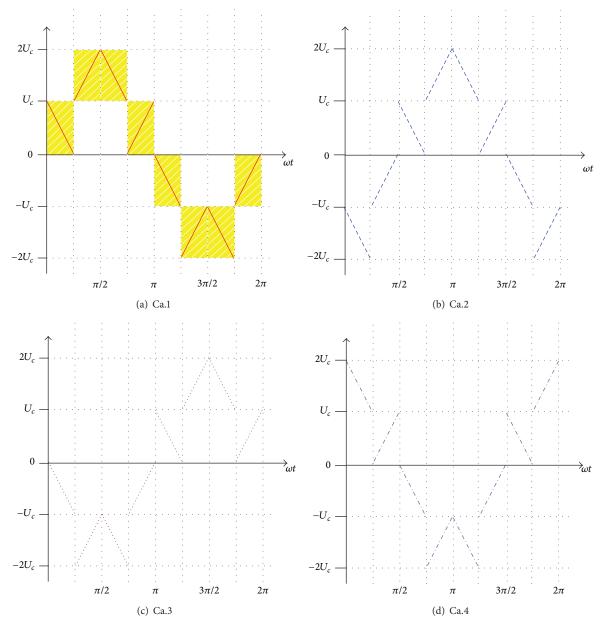

The improvement of the PD control can be done by changing the carrier signal waveform with observation of the difference between the PD and CPS modulation. The carrier signal of the CPS control in a carrier period is shown in Figure 4 for comparison.

As is shown in Figures 4(a) and 4(b), the waveform of the carrier signals in both CPS and PD control is equally divided into 8 parts, which is shown in dash grid in Figures 4(a) and 4(b). Through comparison of the carrier signal in the corresponding parts of the period, the following pattern can be discovered.

Figure 3: Amplitude of  $\omega_c$  voltage harmonic comparison of PD and CPS control.

FIGURE 4: Carrier signal comparison of CPS and PD control.

- (1) In the parts of  $\omega t \in [0, \pi/4] \cup [3\pi/4, \pi] \cup [5\pi/4, 7\pi/4]$ , the slope of the CPS and PD carrier signal is the same.

- (2) In the part of  $\omega t \in [\pi/4, 3\pi/4] \cup [\pi, 5\pi/4] \cup [7\pi/4, 2\pi]$ , the slope of the CPS and PD carrier signal is the opposite.

The shadow part of Figure 4(b) carrier waveform is separately arranged as a set of carriers, which is shown in Figure 5(a). Defined as Ca.1, compared with tri.1 in CPS control, the carrier signal set is no longer a triangular carrier. And the frequency of this carrier signal is the same as that of the CPS triangular carrier. The same separation can be done in the other parts of the PD carrier signal with the same

FIGURE 5: Carrier signal sets of the improved PD control method.

principle. The results are shown in Figures 5(b), 5(c), and 5(d), which are defined as Ca.2, Ca.3, and Ca.4. It is obvious that the phase shift of 90 degrees is the same pattern of that in the CPS control.

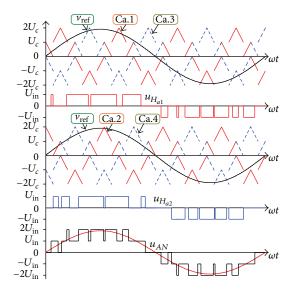

Then, the modulation of the improved PD control is designed to be similar to that of CPD control. The reference signal  $v_{\rm ref}$  is compared with Ca.1 and Ca.3 to generate the drive signal for full bridge unit  $H_{a1}$ . The reference signal  $v_{\rm ref}$  is compared with Ca.2 and Ca.4 to generate the drive signal for full bridge unit  $H_{a2}$ . The  $u_{Ha1}$  and  $u_{Ha2}$  are the output voltage of the full bridge unit, and  $u_{AN}$  is the output phase voltage of the cascaded inverter, which has been shown in Figure 6.

It can be observed in Figure 6 that the switching frequencies of the two bridge units are the same. This is important for heat dissipation design of the power unit. At the same time, the fundamental component of the output voltage for each unit can be measured to be the same. The reason is that the four sets of carrier signals are developed from CPS control, only with different sequence. It means that the output power of each unit is balanced. These two factors are essential for practical implementation of this modulation method. Because only with the balanced output power and equal switching frequency, the practical consideration of rated power and heat cooling design of the power unit can be determined. So this improved PD control method can be used in cascaded multilevel inverter. In the following section, the experimental prototype and measured results will verify the theory.

Figure 6: Modulation of improved PD control.

## 4. Experiment Results and Analysis

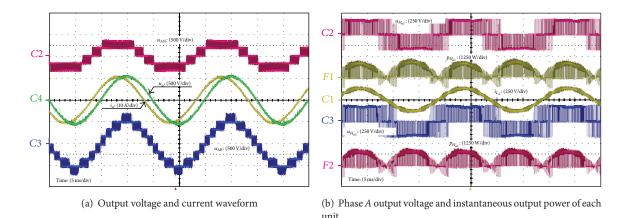

To verify the conclusion above, a five-level three phase cascaded inverter is built with two cascaded units, which is shown in Figure 7. The microcontroller is the TMS320LF2812 from Taxes Instruments. The rated power is 5 kW and the switching frequency is 5 kHz. The input dc voltage for each bridge unit is 180 V. The rated output phase voltage is 220 V, with the frequency of 50 Hz. The output filter inductor is  $400\,\mu\text{H}$ , and the output filter capacitor is  $15\,\mu\text{F}$ .

The experiment result is shown is Figure 8 with measured output voltage, output current, and the instantaneous power waveform. In Figure 8(a), the  $u_{AN}$  represents the phase voltage in the inverter side, while the filtered output line voltage is defined as  $u_o$ . The load current  $i_o$  is shown in the brown color. The inverter output line voltage  $u_{AB}$  is also shown in Figure 8(a). The spectrum analysis of the phase voltage shows that the highest amplitude of phase voltage harmonic is at the switching frequency. But in the line voltage, this harmonic is naturally eliminated. It means that the improved PD control method remains the advantage of PD control. The harmonic of output line voltage is optimized. In Figure 8(b), the output instantaneous power waveform under rated power condition is measured and shown. The driving signals of both units are shown in Figure 8(b). The output inductor current is also shown in Figure 8(b). The average output power of bridge units is measured using a power analyzer and shown in Table 1. It is clear that the improved PD control method can balance the output power of each unit.

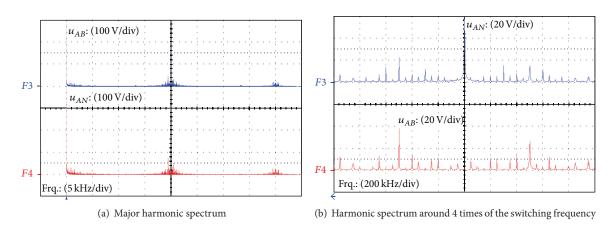

Figure 9 shows the spectrum analysis results of the phase voltage and line voltage with the improved PD method. In Figure 9(a), major harmonics below 50 kHz are shown for the phase voltage and line voltage separately. The highest amplitude harmonics around the 4 times of the switching frequency (20 kHz) are magnified in Figure 9(b) for a clearer view. The analysis result for phase voltage is shown in the

FIGURE 7: Three phase cascaded multilevel inverter experimental prototype.

TABLE 1: Output power measure in different situations.

| Output power | Output power of unit 1 | Output power of unit 2 |

|--------------|------------------------|------------------------|

| 1.5 kW       | 750 w                  | 751 w                  |

| 2 kW         | 999 w                  | 1001 w                 |

up side and line voltage in the low side. It can be observed that, in the situation of phase voltage, the highest amplitude voltage harmonic appears with the frequency of  $20~\rm kHz$ , while in the situation of line voltage, the voltage harmonic at  $20~\rm kHz$  is naturally eliminated with inconsiderable amplitude. The analysis result shows clearly that the improved PD control method retains the PD control's advantage of optimized line voltage harmonic.

## 5. Conclusions

In this paper, a Fourier series expansion method is used to analyze the output phase voltage and line voltage of the PD and CPS control. The spectrum character of the two control methods is analyzed to come to the conclusion that in the range of the whole modulation ratio, the line voltage quality of PD control is better than that of CPS control. The carrier signals of CPS and PD control are compared and an improved PD control method is discussed in this paper. The new method can be practically implemented in the cascaded multilevel invert. With the improved PD control method, the output power of each full bridge unit is balanced and the switching frequencies of the units are kept the same. At the same time, the improved PD method retains the advantage of PD control, the optimized line voltage harmonic. To verify the theory, a 5 kW three phase cascaded multilevel inverter prototype is built in the laboratory. The experiment results show the feasibility of the improved PD control method and the advantages of this novel control method.

FIGURE 8: Experiment waveform for improved PD control method.

FIGURE 9: Spectrum analysis result of output phase voltage and line voltage.

### **Conflict of Interests**

The authors declare that there is no conflict of interests regarding the publication of this paper.

## References

- [1] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez, "A survey on cascaded multilevel inverters," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 7, pp. 2197–2206, 2010.

- [2] J. Ebrahimi, E. Babaei, and G. B. Gharehpetian, "A new multilevel converter topology with reduced number of power electronic components," *IEEE Transactions on Industrial Electronics*, vol. 59, no. 2, pp. 655–667, 2012.

- [3] Z. Du, B. Ozpineci, and L. M. Tolbert, "Modulation extension control of hybrid cascaded H-bridge multilevel converters with 7-level fundamental frequency switching scheme," in *Proceedings of the 38th IEEE Annual Power Electronics Specialists Conference (PESC '07)*, pp. 2361–2366, June 2007.

- [4] C. Buccella, C. Cecati, and H. Latafat, "Digital control of power converters—a survey," *IEEE Transactions on Industrial Informatics*, vol. 3, no. 8, pp. 437–4447, 2012.

- [5] R. Rathore, H. Holtz, and T. Boller, "Generalized optimal pulsewidth modulation of multilevel inverters for low switching frequency control of medium voltage high power industrial ac

- drives," *IEEE Transactions on Industrial Electronics*, vol. 10, no. 60, pp. 4215–4224, 2013.

- [6] L. M. Tolbert, F. Z. Peng, and T. G. Habetier, "A multilevel converter-based universal power conditioner," *IEEE Transac*tions on Industry Applications, vol. 36, no. 2, pp. 596–603, 2000.

- [7] Z. Wu, Y. Zou, and K. Ding, "Analysis of output voltage spectra in a hybrid diode-clamp cascade 13-level inverter," in *Proceedings of the 36th IEEE Power Electronics Specialists Conference (PESC '05)*, pp. 873–8879, 2005.

- [8] J. Wang and F. Z. Peng, "Unified power flow controller using the cascade multilevel inverter," *IEEE Transactions on Power Electronics*, vol. 19, no. 4, pp. 1077–1084, 2004.

- [9] H. Akagi, S. Inoue, and T. Yoshii, "Control and performance of a transformerless cascade PWM STATCOM with star configuration," *IEEE Transactions on Industry Applications*, vol. 43, no. 4, pp. 1041–1049, 2007.

- [10] S. Yin, H. Luo, and S. X. Ding, "Real-time implementation of fault-tolerant control systems with performance optimization," *IEEE Transactions on Industrial Electronics*, vol. 61, no. 5, pp. 2402–2411, 2014.

- [11] X. Wang, Y. Zang, B. Xu, and J.-Q. Lin, "Research on switch-based control method for cascaded H-bridge inverter failures," Proceeding of the CSEE, vol. 27, no. 7, pp. 76–81, 2007.

- [12] P. W. Hammond, "Enhancing the reliability of modular medium-voltage drives," *IEEE Transactions on Industrial Electronics*, vol. 49, no. 5, pp. 948–954, 2002.

- [13] Y.-F. Sun and X.-B. Ruan, "Power balance control schemes for cascaded multilevel inverters," *Proceeding of the CSEE*, vol. 26, no. 4, pp. 126–133, 2006.

- [14] Y.-F. Sun and X.-B. Ruan, "Power balance control schemes for cascaded multilevel inverters," *Proceeding of the CSEE*, vol. 26, no. 4, pp. 126–133, 2006.

- [15] Z.-Y. Yang, J.-F. Zhao, X.-J. Ni, J.-M. Lu, and B. Chen, "Eliminating common-mode voltage of cascaded medium-voltage variable frequency driver with phase-difference STS-SVM," *Proceeding of the CSEE*, vol. 28, no. 15, pp. 32–38, 2008.

- [16] P. Lezana and G. Ortiz, "Extended operation of cascade multicell converters under fault condition," *IEEE Transactions on Industrial Electronics*, vol. 56, no. 7, pp. 2697–2703, 2009.

Submit your manuscripts at http://www.hindawi.com