# Power Electronic Converters and Control for PV Applications

Lead Guest Editor: Abdullah M. Noman Guest Editors: Abdullrahman Alshammaa, Hadeed Ahmed Sher, Hassan Farh, and Mohamed A. Mohamed

# **Power Electronic Converters and Control for PV Applications**

# **Power Electronic Converters and Control for PV Applications**

Lead Guest Editor: Abdullah M. Noman Guest Editors: Abdullrahman Alshammaa, Hadeed Ahmed Sher, Hassan Farh, and Mohamed A. Mohamed

Copyright © 2022 Hindawi Limited. All rights reserved.

This is a special issue published in "International Journal of Photoenergy." All articles are open access articles distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

### **Chief Editor**

Giulia Grancini 🕞, Italy

#### **Academic Editors**

Mohamed S.A. Abdel-Mottaleb (D), Egypt Angelo Albini, Italy Mohammad Alghoul (D, Malaysia Alberto Álvarez-Gallegos (D, Mexico Vincenzo Augugliaro (D), Italy Detlef W. Bahnemann, Germany Simona Binetti, Italy Fabio Bisegna (D), Italy Thomas M. Brown (D, Italy Joaquim Carneiro (D, Portugal Yatendra S. Chaudhary D, India Kok-Keong Chong (D), Malaysia Věra Cimrová 🕞, Czech Republic Laura Clarizia (D, Italy Gianluca Coccia (D, Italy Daniel Tudor Cotfas (D, Romania P. Davide Cozzoli (D, Italy Dionysios D. Dionysiou (D, USA Elisa Isabel Garcia-Lopez (D, Italy Wing-Kei Ho 🕞, Hong Kong Siamak Hoseinzadeh, Italy Jürgen Hüpkes (D), Germany Fayaz Hussain 🕞, Brunei Darussalam Mohamed Gamal Hussien (D), Egypt Adel A. Ismail, Kuwait Chun-Sheng Jiang, USA Zaiyong Jiang, China Yuanzuo Li 🝺, China Manuel Ignacio Maldonado, Spain Santolo Meo (D), Italy Claudio Minero, Italy Regina De Fátima Peralta Muniz Moreira D, Brazil Maria da Graça P. Neves (D, Portugal Tsuyoshi Ochiai 🕞, Japan Kei Ohkubo 🕞, Japan Umapada Pal, Mexico Dillip K. Panda, USA Carlo Renno (D), Italy Francesco Riganti-Fulginei (D, Italy Leonardo Sandrolini (D, Italy Jinn Kong Sheu 🕞, Taiwan Kishore Sridharan (D, India

Elias Stathatos (), Greece Jegadesan Subbiah (), Australia Chaofan Sun (), China K. R. Justin Thomas (), India Koray Ulgen (), Turkey Ahmad Umar, Saudi Arabia Qiliang Wang (), China Xuxu Wang, China Huiqing Wen (), China Weijie Yang (), China Jiangbo Yu (), USA

### Contents

# Optimal Sizing of a Hybrid Renewable Photovoltaic-Wind System-Based Microgrid Using Harris Hawk Optimizer

Abdullrahman A. Al-Shamma'a (D, Hassan M. Hussein Farh (D, Abdullah M. Noman, Abdullah M. Al-Shaalan (D, and Abdulaziz Alkuhayli (D Research Article (13 pages), Article ID 4825411, Volume 2022 (2022)

#### Design of Boosted Multilevel DC-DC Converter for Solar Photovoltaic System

R. Uthirasamy, V. Kumar Chinnaiyan, S. Vishnukumar, Alagar Karthick (D), V. Mohanavel (D), Umashankar Subramaniam, and M. Muhibbullah (D) Research Article (23 pages), Article ID 1648474, Volume 2022 (2022)

# Design of a High Step-Up DC-DC Converter with Voltage Doubler and Tripler Circuits for Photovoltaic Systems

Muhammad Yaseen, Ajmal Farooq, Muhammad Zeeshan Malik (b), Muhammad Usman, Ghulam Hafeez (b), and Muhammad Ali Research Article (11 pages), Article ID 8993598, Volume 2021 (2021)

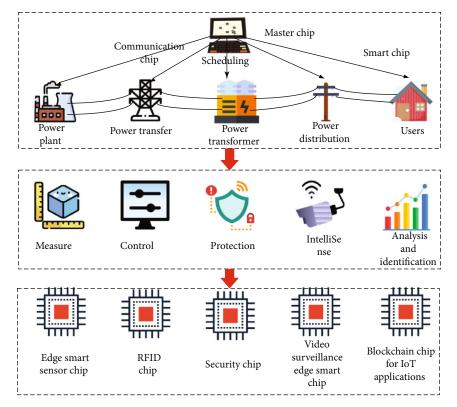

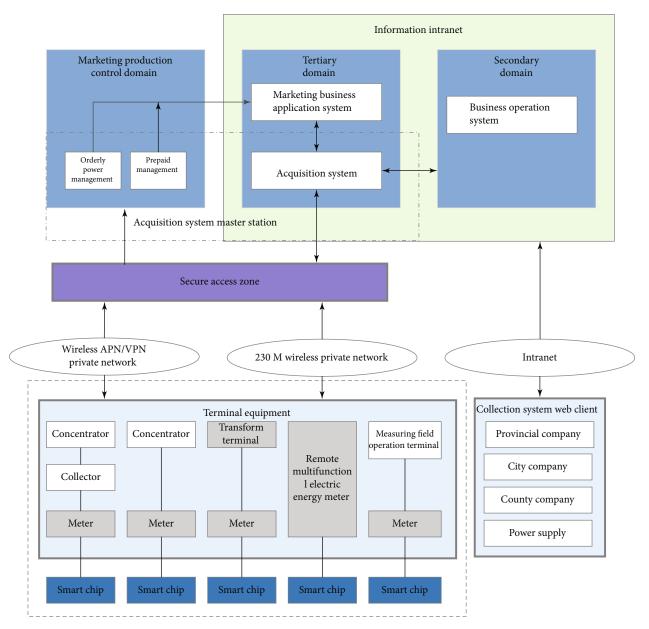

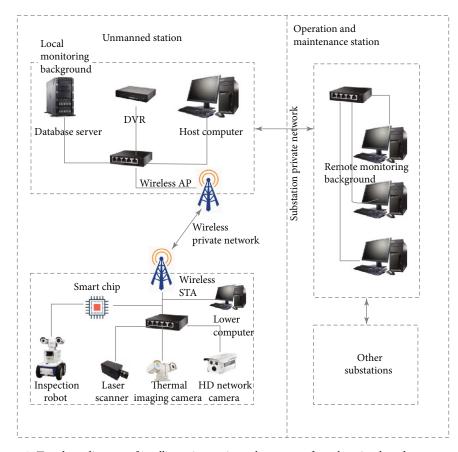

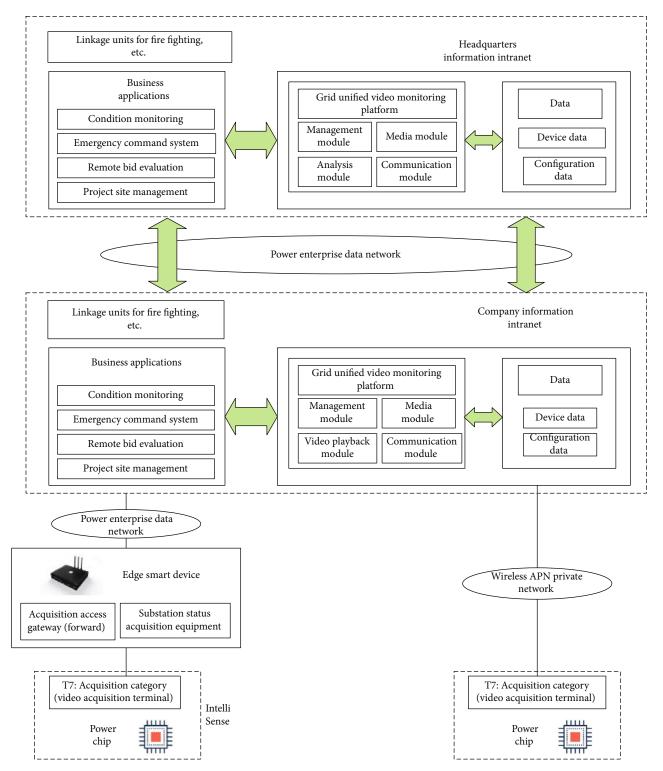

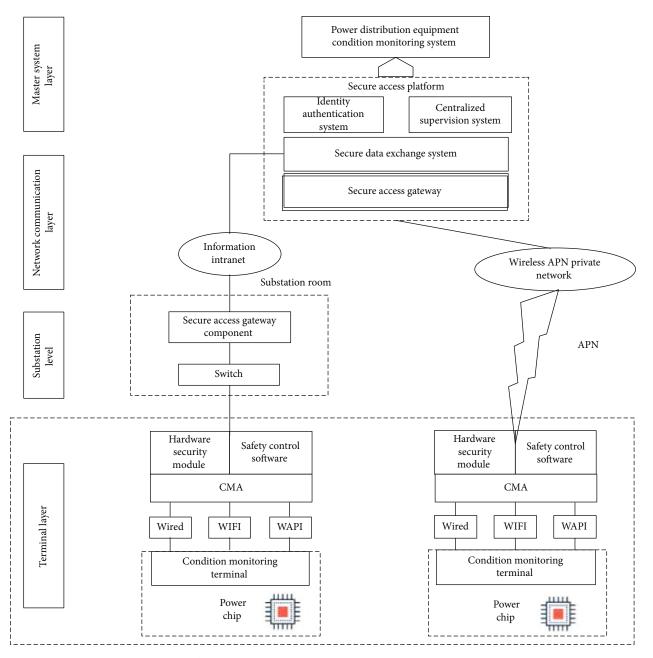

#### Thinking and Prospect of Power Chip Specificity

Fuqi Ma, Min Li (), Xuzhu DONG, Bo WANG (), Yinyu ZHOU, Jincan Li, Lei FENG, and Mohamed A. Mohamed () Review Article (14 pages), Article ID 1512629, Volume 2021 (2021)

### Research Article

## Optimal Sizing of a Hybrid Renewable Photovoltaic-Wind System-Based Microgrid Using Harris Hawk Optimizer

#### Abdullrahman A. Al-Shamma'a , Hassan M. Hussein Farh , Abdullah M. Noman, Abdullah M. Al-Shaalan , and Abdulaziz Alkuhayli

Department of Electrical Engineering, College of Engineering, King Saud University, Riyadh 11421, Saudi Arabia

Correspondence should be addressed to Hassan M. Hussein Farh; hfarh1@ksu.edu.sa

Received 19 November 2021; Revised 9 May 2022; Accepted 7 June 2022; Published 23 June 2022

Academic Editor: Alberto Álvarez-Gallegos

Copyright © 2022 Abdullrahman A. Al-Shamma'a et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Hybrid renewable energy microgrid has become an attractive solution to electrify urban areas. This research proposes a microgrid design problem including photovoltaic (PV) arrays, wind turbine, diesel, and batteries for which Harris hawk optimization (HHO), a metaheuristic technique, is applied. Based on a long-term techno-economic assessment, the HHO approach is used to determine the best hybrid microgrid size for a community in Saudi Arabia's northern region. The efficacy of HHO is investigated, and its performance was compared with seven metaheuristic techniques, grasshopper optimization algorithm (GOA), cuckoo search optimizer (CSO), genetic algorithm (GA), Big Bang–Big Crunch (BBBC), coyote optimizer, crow search, and butterfly optimization algorithm (BOA), to attain the HRE microgrid optimal sizing based on annualized system cost (ASC) reduction. Some benchmarks (optimum and worst solutions, mean, median, standard deviation, and rate of convergence) are used to distinguish and analyze the performance of these eight metaheuristic-based approaches. The HHO surpassed the other seven metaheuristic techniques in achieving the best HRE microgrid solution with the lowest ASC (USD 149229.9) followed by GOA (USD 149380.5) and CSO (USD 149382.5). The findings revealed that the HHO, GOA, CSO, and coyote have acceptable performance in terms of capturing the global solution and the speed of convergence, with only minimal oscillations. The BBBC, crow search, GA, and BA, on the other hand, have unacceptably poor performance, trapping to the local solution, oscillations, and a long convergence time. In terms of optimal solution and convergence rate, the BBBC and GA both perform poorly when compared to the other metaheuristic techniques.

#### 1. Introduction

Renewable energy is the energy generated from naturally renewed resources. Unlike conventional resources, renewable energy resources are nondepletable energy sources. Renewable and reliable energy supplies are required by the world since they are significantly cleaner and create energy without polluting the environment [1]. Wind turbine (WT) generators, solar photovoltaic (PV), geothermal, biomass, and other renewable energy sources exist. Aside from their benefits like environmental friendliness and sustainability, wind and solar PV became increasingly popular because of lower production costs and increased applications for both commercial and residential [2]. These sources of power can be used independently or in combination to supply the utility grid with electrical power. Furthermore, renewable energy system-based microgrid is utilized to electrify remote locations that are not serviced by the utility grid. Owing to the unreliability and large size of employing a single source to supply electricity to remote sites, hybrid energy technologies have been intended to address these difficulties [3]. PVs, WTs, batteries, diesel generators, and fuel cells (FCs) are examples of hybrid renewable energy resources (HRERs). However, when renewable energy resources are employed to supply the off-grid sites with electricity, a challenge can be increased due to their nonlinear and erratic behavior [4]. Diminished reliability, control complexity, design considerations, instability, and lower energy are only a few of the challenges [5]. These problems are nonlinear and complicated optimization problems. The action of making the best or most effective use of HRERs with the least cost is known as optimization [6, 7].

On hybrid renewable energy systems, a variety of optimization strategies are applied, including classical techniques and artificial intelligence (AI) techniques [8-10], hybrid techniques [11, 12], and software programs [13-15]. Analytical techniques [16, 17], graphical techniques [18, 19], statistics techniques [20], and numericalbased techniques [21] are examples of classical techniques. Although classical methods are straightforward, they have some constraints for defining the optimization issue. Graphical techniques, for example, rely on solar irradiance and wind speed information to estimate system sizing, which can lead to size issues (oversizing or undersizing) [22]. Analytical techniques are incapable of dealing with a lot of energy sources, and they take longer to compute than AI algorithms. On the other hand, other optimization algorithms like AI, hybrid computing, and software programs do not have the same constraints as classical techniques and can effectively tackle the optimization problems. The researchers are motivated to learn more about technical and economic feasibility difficulties by promoting more use of HRERs to supply the off-grid and ongrid rural remote regions. The HOMER PRO software application in [13-15] was used to conduct a technoeconomic analysis. In [13], the authors investigated, assessed, and designed a technical and economic viability of solar PV-diesel-batteries for electrifying a town in Pakistan. Their approach makes use of the national grid's time-constrained availability. The HOMER PRO software tool was used to estimate the system optimal size and assess its techno-economic viability. According to the findings of this study, grid-integrated systems have a lower Cost of Energy (COE) than off-grid systems. The study in [14] used HOMER software program for remodeling and refinancing a rural microgrid on a Thai island. The system was designed to offer the lowest COE. In Benin, a research was conducted to look into the powering of rural villages; the hybrid PV-diesel-batteries was proven to be the most cost-effective [15].

The appropriate HRER sizing is unavoidable since oversizing increases the initial cost while undersizing reduces the shared power from the HRERs and, as a result, reduces system reliability. The use of AI approaches to size HRERs optimally has recently piqued the interest of most experts across the world. Some research examined single-objective models, whereas others investigated multiobjective models [8] [23-25]. To lower the annual cost of a hybrid PV-WTbattery system, the authors utilized a model based on a fuzzy logic [23]. The sizing of storage energy systems in renewable energy networks was optimized using a genetic algorithm (GA) in [8], limiting expected energy not supplied and power losses (PL). In [24], this study proposed an effective sizing technique for the component of the hybrid photovoltaic-WT-battery system according to GA and combined with an energy management strategy. The economic model/predictive control technique [26] was used to develop an energy management technique. The authors in [25] pro-

posed a quasisteady operating approach combined with GA to achieve the best size of a PV-pump storage hydroelectric system according to both the loss of power supply probability (LPSP) and investment cost. In [27], a MATLAB framework for optimal size of a wind-hydro system based on lower COE and CO<sub>2</sub> emissions was developed. In order to reduce the total net present value, the authors implemented a model based on a mixed-integer linear programming modeling framework for attaining technical and economic optimum design of PV and energy storage systems [28]. The authors in [29] employed Particle Swarm Optimization (PSO) to design the best PV-WT-battery system according to reducing the total annual cost (TAC). Based on net present cost (NPC) minimization, GA was employed to address a multiobjective sizing issue for a PV-WT-battery-solar collector [30]. In [9], the authors modified a cuckoo search optimizer (CSO) for sizing PV-battery, WT-battery, and PV-WT-battery systems with the purpose of lowering overall system costs. The results revealed that the CSO generates higher-quality solutions and is faster to convergence than the PSO and GA approaches. The Pareto evolutionary algorithm was used by the authors in [31] to reduce the LCOE and CO<sub>2</sub> life cycle emissions (LCE) for a WT-PV-diesel-battery system. The PV-biogas-pump storage-battery system was designed using the Water Cycle Algorithm (WSA) and Moth-Flame Optimization (MFO) in [32]. The MFO approach and the WSA are assessed and compared to the GA. The differential evolution (DE) was combined with a fuzzy control by the authors in [33] to optimize the design of a PV-WT-diesel-hydrogen-battery system according to the least cost, emission, and unmet load. The authors in [34] proposed an improved Fruit Fly Optimizer (FFO) for designing a hybrid PV-WT-diesel-battery system with the lowest pollutant emission and TAC. The line-up competition algorithm was used in [35] to build an optimal PV-WT-diesel-battery system that minimized TAC and emissions of CO<sub>2</sub>. In [36], the author used Grey Wolf Optimization (GWO) to determine the best size for a photovoltaic-WT-biomass system while reducing the TNPC and LPSP. The GWO method's results were compared to those of the GA and Simulated Annealing (SA) methods, demonstrating that the GWO method is superior. For attaining optimal sizing of the PV-WT-battery system, a hybrid Big Bang-Big Crunch (BBBC) was proposed in [37]. To identify the appropriate size for a PV-WT system by reducing the TAC, the authors of [38] employed an Ant Colony Optimization (ACO) algorithm. The authors of [39] applied a hybrid optimizer technique using two well-known metaheuristics: SA and Tabu Search to attain the best size of a small selfcontained PV-WT-diesel-biodiesel generator-FC-battery power system to minimize the system's COE. The equilibrium optimizer performed well compared to bat optimizer, and Black Hole (BH) optimization was applied to size the energy systems a microgrid of a photovoltaic with FCs and battery storage energy systems to minimize the COE [40]. In [41], the best size of a PV/WT/battery/diesel microgrid has been attained using Bonobo optimization algorithm based on ASC reduction. The optimal sizing of a microgrid consisting of PV/WT/battery/diesel while satisfying the

LPSP and REF reliability measures was achieved by using an artificial ecosystem-based optimization algorithm [42]. In [43], a modified African vulture optimizer (IAVO) is proposed to identify the optimal configuration for a HRERs. The structure is composed of fuel cell, WT, and PV and its auxiliaries that include the electrolyzer and the storage system. The main target is to find the optimal configuration to minimize the LPSP and TNPC. In [44], a new optimization algorithm called converged krill herd (CKH) has been proposed for optimal size of a HRERs including battery and fuel cell to supply the driving force of a locomotive. The main goal is to minimize the total cost of the system while dealing with various constraints such as the battery capacity constraint and the fuel cell state-of-charge limit.

Based on the previous literature, this article was considered an early attempt to apply the Harris hawk optimization (HHO) technique to tackle the optimal design optimization problem in standalone microgrid. The HHO is applied to a highly constrained objective function that considers several important constraints, including power balancing, generation power capacities, LPSP, and renewable energy fraction (REF) restrictions. The effectiveness of applied HHO was investigated, and its performance was compared to that of seven metaheuristic techniques: grasshopper optimization algorithm (GOA), CSO [9], BBBC [37], coyote [45], crow search [46], GA [8], and butterfly optimization algorithm (BOA) [47] to achieve HRE microgrid optimal sizing with a quick convergence rate and the lowest annualized system cost (ASC). To empirically evaluate this, the following research questions were formulated: Does any algorithm perform significantly better than others for solving the optimal sizing problem? Is there any dependency between algorithm used and the initial population? Some benchmarks are used to distinguish and analyze the performance of these metaheuristic-based techniques. The HHO outperformed the other seven metaheuristic techniques in achieving the best HRE microgrid solution, with the lowest ASC (USD 149229.9) followed by GOA (USD 149380.5) and CSO (USD 149382.5), respectively. The proposed HHO technique could be useful for a wide range of optimization challenges in the power and energy industries. According to the findings, the HHO, GOA, CSO, and coyote have appropriate global solution capture and convergence rates with low oscillations. The BBBC, crow search, GA, and BA, on the other hand, perform poorly, with trapping to the local solution, oscillations, and a long convergence time. The BBBC and GA both perform poorly in terms of optimal solution and convergence rate when compared to other metaheuristic approaches.

The remainder of the paper is organized as follows. The PV, WT, battery, and diesel generators are all mathematically modelled in Section 2. The objective function and constraints of the problem formulation are presented in Section 3. The proposed HHO technique is discussed in Section 4. Section 5 includes the simulation results as well as discussions. The article is finally concluded in Section 6.

#### 2. Proposed Hybrid Photovoltaic-Wind Energy Microgrid

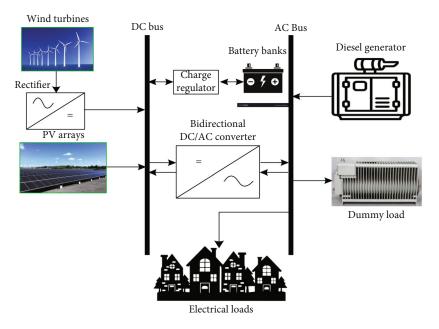

The proposed microgrid configuration is shown in Figure 1. WT and PV arrays are the system's principal energy sources. The AC bus bar is connected to the WTs and diesel generator, while the DC bus bar is interconnected to the PV arrays and battery banks. The bidirectional DC/AC converter serves as both an inverter and a rectification bridge, converting DC to AC power and AC to DC power. When renewable generation sources cannot fully meet the load, the battery banks are used to provide backup power. Diesel generators serve as a backup power source when neither the WTs nor the PV arrays can generate output power, and the batteries are depleted. The load to be supplied is assessed using real-world data collected in an isolated community named Al-Sulaymaniyah (within Arar region in Saudi Arabia), where the load is currently served by diesel generator units. The optimization trend tries to reduce the planned proposed hybrid microgrid net present cost (NPC).

The NPC can be estimated using the following formula:

NPC = ASC

$$\frac{(1+i)^{Y_{\text{proj}}}-1}{i(1+i)^{Y_{\text{proj}}}},$$

(1)

where *i* is the interest rate per year and  $Y_{\text{proj}}$  is the lifetime of the project.

The annualized cost of each unit is equivalent to the annualized costs of its capital investment ( $C_{\text{acap}}$ ), as well as its annualized operating and maintenance cost ( $C_{\text{amain}}$ ) and annualized replacement costs ( $C_{\text{arep}}$ ) as shown in the following equation [48]:

$$ASC = C_{acap} + C_{arep} + C_{amain}.$$

(2)

The capital cost can be expressed as in the following form:

$$C_{\text{acap}} = (C_{\text{ren.}} + C_{\text{Batt}} + C_{\text{DG}}) \frac{i(1+i)^{Y_{\text{proj}}}}{(1+i)^{Y_{\text{proj}}} - 1},$$

(3)

where  $C_{\text{ren.}}$  is the renewable capital costs,  $C_{\text{Batt}}$  is the battery capital costs, and  $C_{\text{DG}}$  is the capital costs of the diesel generator.

The mathematical modelling for each of the microgrid components used in this study is described in the subsections below.

2.1. Modeling of the PV Array. The PV array's output power is determined by incident solar radiation, temperature, and the PV array's manufacturer's data as follows [48]:

$$P_{\rm PV} = P_r f_{\rm PV} \left( \frac{\overline{G_T}}{\overline{G_{T,\rm STC}}} \right) (1 + \alpha_P (T_c - T_{c,\rm STC})), \qquad (4)$$

FIGURE 1: Configuration of the proposed PV-WT-diesel-battery microgrid.

where  $P_r$  is the nominal photovoltaic power.  $\overline{G_{T,\text{STC}}}$  is the global photovoltaic irradiance under STCs.  $\overline{G_T}$  is the global solar irradiance under normal conditions.  $T_{c,\text{STC}}$  is the PV temperature under STCs.  $T_c$  is the PV temperature under

normal conditions.  $f_{\rm PV}$  is the derating coefficient.  $\alpha_P$  is the temperature coefficient of power.

The PV's steady-state temperature is calculated using the following equation [48]:

$$T_{c} = \frac{T_{a} + (\text{NOCT} - T_{a,\text{NOCT}})(1 - 1.11\eta_{\text{MPP}}(1 - \alpha_{P}T_{c,\text{STC}}))(\overline{G_{T}}/G_{T,\text{NOCT}})}{1 + 1.11(\alpha_{P}\eta_{\text{MPP}\text{STC}})(\text{NOCT} - T_{a,\text{NOCT}})(\overline{G_{T}}/G_{T,\text{NOCT}})},$$

(5)

where  $T_a$  is the PV ambient operating cell temperature. NOCT is the PV nominal operating cell temperature.  $T_{a,\text{NOCT}}$  is the PV ambient temperature under NOCT.  $G_{T,\text{NOCT}}$  is the solar irradiance under NOCT.  $\eta_{\text{MPP,STC}}$  is the MPP efficiency of PV under STCs.  $\eta_{\text{MPP}}$  is the PV-MPP efficiency.

2.2. Modeling of the Wind Generator. The WTs' output power is determined by the following equation:

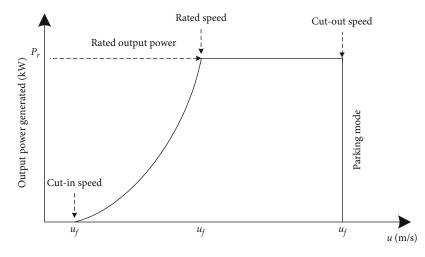

$$P_{\rm WT}(u) = P_r \times \begin{cases} 0, & u < u_c \text{ or } u > u_f, \\ \frac{u^2 - u_c^2}{u_r^2 - u_c^2}, & u_c \le u \le u_r, \\ 1, & u_r \le u \le u_f, \end{cases}$$

(6)

where  $P_r$  is WT rated power,  $u_c$  is the starting speed,  $u_r$  is the rated speed, and  $u_f$  is the furling speed. The power generated by WT is dependent on four parameters:  $P_r$ ,  $u_c$ ,  $u_r$ , and  $u_f$  as shown in Equation (6). The WT power curve based on a nonlinear model is shown in Figure 2. There is no power generated when the wind speed is less than  $u_c$  or greater than

$u_c$ . The WT generator starts to generate power once the wind speed becomes greater than  $u_c$  and reaches to the rated power at the rated speed. The power generated from the WT becomes fixed at the rated power when the wind speed is greater than  $u_r$  and less than  $u_f$ .

2.3. Modeling of the Battery Bank. All hybrid microgrids require some form of energy storage. This is attributed to the reason that renewable energy resources' output power is uncertain due to their erratic and intermittent climatic conditions. The total amount of energy supplied determines the state of charge (SOC), which can be calculated by the following formula [49, 50]:

$$SOC(t) = SOC(t-1)(1-\sigma) + \left(E_{GA}(t) - \frac{E_L(t)}{\eta_{inv}}\right) \eta_{battery},$$

(7)

where  $\sigma$  is the rate of self-discharging; E(t) is the overall output power;  $E_L(t)$  is the load demand; and  $\eta_{inv}$  and  $\eta$  are the inverter efficiency and battery's charge efficiency, respectively. The SOC limit cannot be smaller than the battery's minimum permitted level (SOC<sub>min</sub>). The SOC cannot exceed

FIGURE 2: Power characteristic curve of a WT.

the maximum allowable level  $(SOC_{max})$  during a charging process. These SOC constraints can be expressed as follows:

$$SOC(t) = \begin{cases} SOC_{\min}, & SOC(t) < SOC_{\min}, \\ SOC(t) & SOC_{\min} < SOC(t) < SOC_{\max}, \\ SOC_{\max} & SOC(t) > SOC_{\max}. \end{cases}$$

(8)

2.4. Modeling of the Diesel Generator. A diesel generator performs the role of the tertiary source in a hybrid microgrid, eliminating the necessity for storing energy. As a result, it is crucial for regional and remote load systems to keep running. It also helps make the system more reliable and costeffective. The diesel generator is primarily used during periods of peak demand and battery depletion due to its low efficiency load rate. Therefore, when constructing a hybrid microgrid, it is important to keep in mind that the diesel generator should not run under low load or at all. The annual fuel cost and power generated can be estimated using the following equation:

$$C_{\rm DG} = C_F \sum_{t=1}^{8760} AP_{\rm DG}(t) + BP_R, \tag{9}$$

where  $P_{DG}$  and  $P_R$  are the rated power and power generated of the diesel generator, respectively. The values of *A* and *B* in this investigation are 0.246 and 0.08415, respectively.

2.5. Energy Management Strategy. The proposed hybrid microgrid is regulated by the following conditions:

- (a) PV and WT are the microgrid's principal sources of power

- (b) When the power generated from PV and WT surpasses the capacity demands, the batteries are charged. The excess power is discharged after the battery is fully charged. If the demand is more than

the generated power from the renewable energy resources, the load that is not provided is met by the battery if its available energy is more than its minimum capacity

- (c) As a last choice, a diesel generator is used, if

- (i) the load shortage is less than the diesel generator's minimum permitted power, diesel generator will serve at its minimum permissible power, and the excess power will be dumped

- (ii) the load not supplied is delivered by the diesel generator if it is higher than the minimum permissible level and less than its nominal power. If the remaining load is higher than the nominal power, diesel generator will function at that power level, and the load not delivered will come from the battery if the storage capacity is sufficient

Based on these conditions, Algorithm 1 presents the appropriate energy management technique.

#### 3. Problem Formulation

The objective of the microgrid optimization problem is to lower the ASC while maintaining a specific level of reliability, in this case LPSP. In this study, the best microgrid design has been defined as a constrained objective function:

subject to :

$$\begin{cases}

min ASC \\

LPSP \leq LPSP_{desired} \\

REF \leq REF_{desired} \\

0 \leq P_{PV} \leq P_{PV,max} \\

0 \leq P_{WT} \leq P_{WTG,max} \\

0 \leq P_{Batt} \leq P_{Batt,max} \\

0 \leq P_{Del} \leq P_{Del max}

\end{cases}$$

(10)

```

IF energy generated E(t) is enough to supply load E_L(t), THEN

Supply the load and charge the battery if possible

ELSE

IF battery is charged (SOC > SOC<sub>min</sub>), THEN

Use battery banks to supply the load

IF battery is not enough (SOC < SOC<sub>min</sub>), THEN

Run diesel generator along with battery

END

ELSE

Run diesel generator only to supply the load

END

END

```

ALGORITHM 1: Pseudocode of the proposed energy management algorithm.

where LPSP<sub>desired</sub> and REF<sub>desired</sub> are the reliability and REF levels selected by the user. The rated power of the PV, WT, and diesel generator (in kW) is represented by  $P_{\rm PV}$ ,  $P_{\rm WTG}$ , and  $P_{\rm Dsl}$ , respectively. The capacity of the battery bank is  $P_{\rm Bat}$  (in kWh). The maximum rating of the PV, WTs, batteries, and diesel is represented by  $P_{\rm PV,max}$ ,  $P_{\rm WT,max}$ ,  $P_{\rm Bat,max}$ , and  $P_{\rm Diesel,max}$ . The optimal values of the PV, WT, and nominal power of the diesel generator, as well as battery storage capacity, are determined based on the minimum ASC value as follows:

$$x = [P_{\rm PV}, P_{\rm WT}, P_{\rm Diesel}, P_{\rm Bat}].$$

(11)

3.1. Modeling of LPSP. The LPSP is a vital aspect in establishing the microgrid's successful reliability. The risk that the microgrid's available power will be insufficient to fulfill the total demand level is specified as the LPSP. The following equation is a representation of the LPSP:

$$LPSP = \frac{\sum_{t=0}^{T} Power \text{ outage Time}}{T}.$$

(12)

A LPSP value of zero means the load has always been delivered, whereas a value of one means the load will not be supplied. The duration of time during which a load demand is not met is known as the power outage time (POT).

*3.2. Renewable Energy Fraction.* The renewable energy fraction (REF) is a terminology that refers to the total amount of renewable energy delivered to load demand, as seen in the following equation [48]:

$$\text{REF} = \left(1 - \frac{E_{\text{diesel}}}{E_{L,\text{served}}}\right) \times 100,\tag{13}$$

where  $E_{\text{diesel}}$  is the total amount of power generated by diesel. A classical diesel generator system is equal to 0% of a REF, while a clean system is equal to 100% of a REF. The hybrid energy system is represented by the values ranging from 0% to 100%.

#### 4. Harris Hawk Optimization Technique

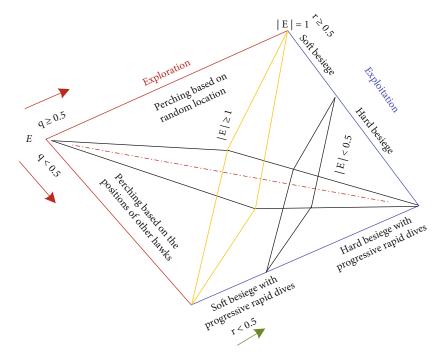

The algorithm of HHO's exploitative and exploratory technique is used to solve the hybrid microgrid optimal design [51], which is inspired by the Harris hawk's aggressive attitude. Depending on the appropriate formulation problem, the HHO approach can be utilized to tackle a range of optimization problems. The various phases of HHO are depicted in Figure 3 [51], which are covered in the following subsections.

4.1. Exploratory Phase. Harris' hawks use their strong eyes to follow and detect prey; the prey may not always be easy to spot. As a result, the hawks wait, watch, and monitor the desert for long times in order to track a prey. The Harris' hawks are candidate solutions, and the best solution in each phase is regarded the intended prey or nearly so. Harris' hawks sit at random spots and wait for prey using one of two tactics. They roost in accordance with the positions of other members of the family and the rabbit, as represented in Equation (14) for q < 0.5, or roost on tall trees at random within the range, as formulated in Equation (14) for  $q \ge 0.5$  [51].

$$X(t+1) = \begin{cases} X_{\text{rand}}(t) - r_1 | X_{\text{rand}}(t) - 2r_2 X(t) |, & q \ge 0.5, \\ (X_{\text{rabbit}}(t) - X_m(t)) - r_3 (LB + r_4 (\text{UB} - \text{LB})), & q < 0.5, \end{cases}$$

(14)

where X(t+1) is the location of the hawks in the next iteration t.  $X_{\text{rabbit}}(t)$  is the location of the rabbit. X(t) is the current location of the hawks,  $r_1, r_2, r_3, r_4$ . q is random numbers between [0, 1]. LB and UB are upper and lower boundaries.  $X_{\text{rand}}(t)$  is a random selection from the current population of hawks.  $X_m$  is the average position of hawks in the present population.

4.2. Exploitative Phase. The Harris hawks attack the targeted prey spotted in the prior phase in this phase, which is known as the surprise pounce. Preys, on the other hand, frequently strive to flee perilous situations. As a result, different chasing styles emerge in real-life settings. To represent the tackling stage, the HHO proposes four alternative techniques based on prey escaping performances and Harris' hawk pursuit

FIGURE 3: The Harris hawk optimization phases.

tactics. Preys are continually trying to flee from hazardous situations. Assume that r is the probability of a prey successfully fleeing (r < 0.5) or failing to flee ( $r \ge 0.5$ ) before a surprise pounce. Hawks will engage in a harsh or soft besiege to capture the prey, regardless of what the prey does. It means they will surround the prey in a variety of ways, softly or forcefully, depending on how much energy the prey has saved. In actual life, the hawks go nearer and nearer to their selected prey to enhance their chances of hunting the rabbit collectively by conducting a surprise pounce. Short time after, the fleeing prey will gradually lose its energy, and the hawks will strengthen the besiege to easily catch the weary prey. The E parameter is used to model this strategy and allow the HHO to flip between soft and harsh besiege processes. When |E| $\geq 0.5$ , the soft surround occurs, and when |E| < 0.5, the hard surround occurs [51].

#### 5. Simulation Results and Discussions

The proposed Harris hawk optimization (HHO) technique is utilized to attain the best size for a hybrid microgrid system that comprises PV, WT, diesel, and batteries to provide electricity for Al Sulaymaniyah hamlet in Arar, Saudi Arabia. The HHO is compared to seven metaheuristic techniques: GOA, CSO, BBBC, coyote, crow search optimizer, genetic algorithm, and BOA to validate its performance. The optimization issue was implemented using MATLAB R2019b/ 64-bit/Windows 10 with 500 iterations and 50 runs for all eight metaheuristic-based techniques. In this investigation, the values of average hourly irradiance and wind speed have been used.

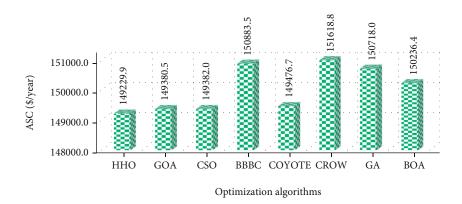

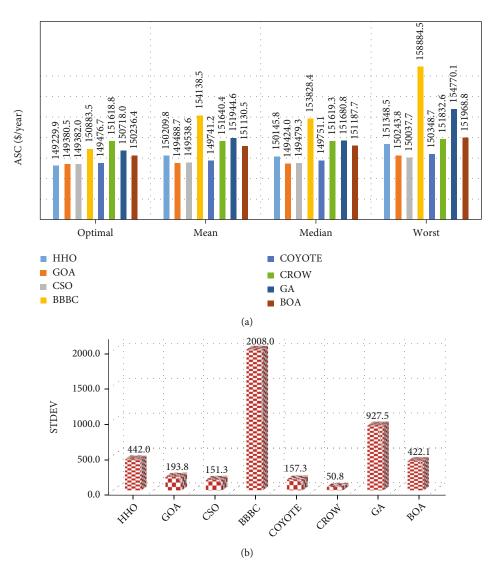

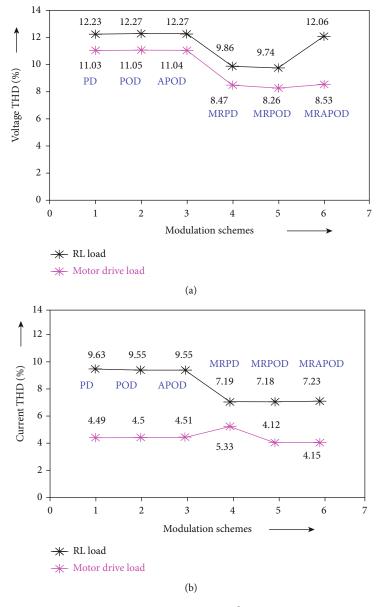

Table 1 shows the simulation findings of the HHO with seven recent metaheuristics for tackling the best size of the

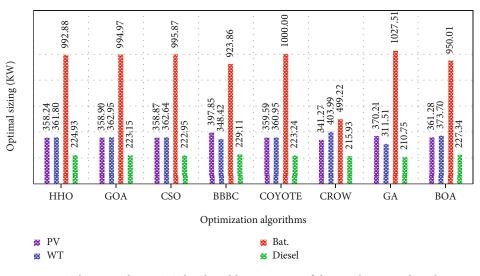

proposed HES microgrid with a 0% of LPSP in terms of the best solution, worst, average, and standard deviation (STDEV). According to these results, the HHO performed better than any of the other seven metaheuristics tested: GOA, CSO, BBBC, coyote, crow search, genetic algorithm, and BOA in achieving the best size of the HES microgrid with the lowest cost. This is obvious by looking at Figure 4, which compares the optimal ASC calculated using the HHO to the results obtained by employing seven other metaheuristic-based techniques. This figure proved the HHO efficacy to attain the optimal solution followed by GOA, CSO, and coyote.

Figure 4 reveals that crow search and BBBC have the lowest performance among the other metaheuristic-based techniques. Figure 5 depicts the optimum combination of the WT, PV, batteries, and diesel generator for each of the eight metaheuristic algorithms. This figure proves that the renewable energy (PV and WT) participates higher than the diesel where the diesel sizing is minimized, and the renewable sizing is increased as the diesel price increases. Figures 6(a) and 6(b) also illustrate the five-performance metrics that are employed to assess the performance of the eight techniques. Compared to the other seven optimization strategies, HHO has the best performance, whereas the BBBC and genetic algorithm have the worst performance based on these five-performance metrics, as shown in Figure 6. Furthermore, based on these five-performance metrics, it can be revealed that the four metaheuristicbased optimization techniques (HHO, GOA, CSO, and coyote) have an acceptable performance whereas the remaining four metaheuristic-based techniques (BBBC, crow search, genetic algorithm, and BOA) have poor performance. The BBBC has the worst performance compared to the other seven optimization techniques.

| TABLE 1: Results of the HHC | compared with seven | metaheuristic optimization algorithms. |

|-----------------------------|---------------------|----------------------------------------|

|                             |                     |                                        |

| Algorithm                                                                         | Performance indicators | $P_{PV}$ (kW) | $P_{WT}$ (kW) | $P_{Bat}$ (kW) | $P_{Diesel}$ (kW) | ASC (USD/year) | REF (%)  |

|-----------------------------------------------------------------------------------|------------------------|---------------|---------------|----------------|-------------------|----------------|----------|

|                                                                                   | Optimal                | 358.24        | 361.80        | 992.88         | 224.93            | 149229.9       | 86.30694 |

|                                                                                   | Worst                  | 406.5051      | 339.3375      | 562.0104       | 209.5526          | 151348.5       | 82.46066 |

| ННО                                                                               | Mean                   | 356.4754      | 345.0759      | 829.1315       | 216.8645          | 150209.8       | 84.1395  |

|                                                                                   | STDEV                  | 39.18455      | 46.1519       | 220.7427       | 9.658326          | 442.0191       | 1.652636 |

|                                                                                   | Optimal                | 358.90        | 362.95        | 994.97         | 223.15            | 149380.5       | 86.36665 |

| CO.4                                                                              | Worst                  | 308.8779      | 383.4638      | 835.64         | 216.0318          | 150243.8       | 84.52918 |

| GOA                                                                               | Mean                   | 357.2016      | 362.815       | 975.8187       | 222.7259          | 149488.7       | 86.15532 |

|                                                                                   | STDEV                  | 12.37447      | 5.529344      | 80.77056       | 3.248609          | 193.8246       | 0.810537 |

|                                                                                   | Optimal                | 358.87        | 362.64        | 995.87         | 222.95            | 149382         | 73.76322 |

| CSO                                                                               | Worst                  | 351.4298      | 375.2112      | 882.0394       | 232.8948          | 150037.7       | 99.06436 |

| CSO                                                                               | Mean                   | 359.7846      | 363.0136      | 985.4449       | 225.0616          | 149538.6       | 84.39674 |

|                                                                                   | STDEV                  | 2.705516      | 5.21919       | 20.49994       | 3.396348          | 151.2683       | 10.83353 |

|                                                                                   | Optimal                | 397.85        | 348.4         | 923.9          | 229.1             | 150883.5       | 64.55    |

|                                                                                   | Worst                  | 293.95        | 434.95        | 1436.3         | 248.06            | 158884.5       | 70.52    |

| BBBC                                                                              | Mean                   | 372.75        | 364.27        | 844.21         | 239.71            | 154138.5       | 86.67    |

|                                                                                   | STDEV                  | 72.14         | 69.41         | 293.67         | 7.45              | 2007.99        | 10.379   |

|                                                                                   | Optimal                | 359.59        | 360.95        | 1000.00        | 223.24            | 149476.7       | 86.42048 |

| Correto                                                                           | Worst                  | 338.064       | 396.3999      | 919.5867       | 230.7491          | 150348.7       | 86.34566 |

| Coyote                                                                            | Mean                   | 359.1265      | 363.0383      | 990.8932       | 224.8782          | 149741.2       | 80.31711 |

|                                                                                   | STDEV                  | 4.173589      | 7.046377      | 13.62386       | 3.152154          | 157.3429       | 16.49967 |

|                                                                                   | Optimal                | 341           | 404           | 499            | 216               | 151619         | 82.7     |

| CDOW                                                                              | Worst                  | 359           | 405.8         | 498.86         | 221.7             | 151833         | 83.05    |

| CROW                                                                              | Mean                   | 341.8         | 405.          | 499.11         | 216               | 151640         | 82.77    |

|                                                                                   | STDEV                  | 4.57          | 2.93          | 0.3925         | 0.884             | 50.77          | 0.098    |

|                                                                                   | Optimal                | 370.2         | 311.5         | 1028           | 211               | 15072          | 85.2     |

| $C_{\text{constitution}} = 1 - c_{\text{constitution}} (C_{\text{constitution}})$ | Worst                  | 496.3         | 260.5         | 1356           | 204.2             | 15477          | 88.3     |

| Genetic algorithm (GA)                                                            | Mean                   | 375.6         | 346.9         | 940.6          | 219.1             | 151945         | 85.6     |

|                                                                                   | STDEV                  | 45.9          | 52.92         | 161.4          | 21.4              | 927.5          | 1.627    |

|                                                                                   | Optimal                | 361.28        | 373.70        | 950.01         | 227.34            | 150236.4       | 63.31917 |

| DOA                                                                               | Worst                  | 352.0645      | 331.3051      | 657.5377       | 228.0661          | 151968.8       | 61.28074 |

| BOA                                                                               | Mean                   | 343.8703      | 353.6341      | 850.2741       | 214.0609          | 151130.5       | 66.92574 |

|                                                                                   | STDEV                  | 26.3586       | 27.9817       | 161.5311       | 11.46092          | 422.1061       | 6.236738 |

FIGURE 4: The optimal ASC utilizing HHO when compared to the other seven metaheuristic techniques.

FIGURE 5: The optimal PV, WT, diesel, and battery sizing of the metaheuristic algorithms.

FIGURE 6: The five-performance metrics: (a) optimal, worst, median, and mean and (b) STDEV.

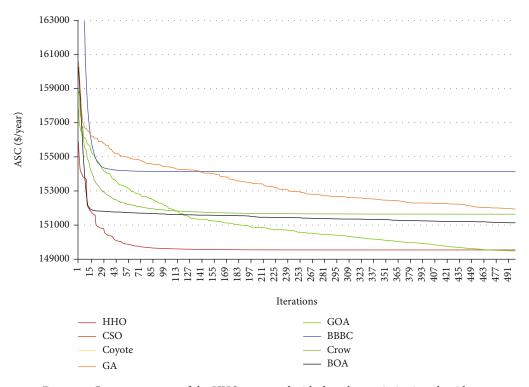

FIGURE 7: Convergence rate of the HHO compared with the other optimization algorithms.

Computational time (s)

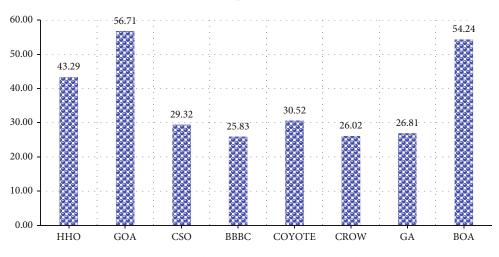

FIGURE 8: The computational time of the eight metaheuristic algorithms under consideration.

The convergence rate of all metaheuristic techniques: HHO, GOA, CSO, BBBC, coyote, crow search, genetic algorithm (GA), and BOA, is shown in Figure 7. As demonstrated in this figure, the four metaheuristic-based techniques (HHO, GOA, CSO, and coyote) have a higher rate of convergence than the other four metaheuristicbased methods while tracking the global solution. This graph also demonstrates that BBBC and GA have the slowest convergence rates, which implies they might become stuck in a local solution and take a long time to achieve a steady state. This is because BBBC and GA both have a high STDEV. As a result, the best solutions are broadly distributed, and both techniques could end up with a local solution.

The computational time required by each algorithm to obtain the optimum solution is depicted in Figure 8. Although the BBBC, GROW, and GA were the quickest to discover the best solution in almost all experiment runs, one must bear in mind that these algorithms provided the worst findings. As shown in Figure 8, the HHO, GOA, and BOA algorithms have been shown to be nondominant. Although the HHO can find the best optimal solution compared to the seven algorithms, it needs improvement related

FIGURE 9: The ASC vs. run number for metaheuristic algorithms.

to the reduction of the computational time. Figure 9 illustrates the ASC versus the run number for the HHO method compared with the other seven metaheuristic-based optimization approaches. The four metaheuristic-based approaches (HHO, GOA, CSO, and coyote) can abide the global solution and attain the optimal design of the HES microgrid with the lowest ASC, less oscillation, and quick convergence, while the four metaheuristic-based optimization approaches (BBBC, crow search, BOA, and genetic algorithm) may be trapped to the local solution and have clear oscillations, as shown in Figure 9. Furthermore, this graph indicates that both BBBC and genetic algorithm are unable to capture the global solution, resulting in noticeable steady-state oscillations.

#### 6. Conclusions

The Harris hawk optimization (HHO) technique has been used to find out the best design for a HRE microgrid, which includes PV, WT, diesel, and batteries to provide electricity for Al Sulaymaniyah hamlet in Arar, Saudi Arabia. The HHO is compared to seven metaheuristic-based techniques for validation: GOA, CSO, BBBC, coyote, crow search, genetic algorithm, and BOA to achieve the best size of the HES microgrid based on minimizing the annualized system cost. To discern and assess the performance of these eight metaheuristic algorithms, five-performance benchmarks (optimal and worst solution, STDEV, mean, and median)

are utilized. The HHO surpassed the other seven metaheuristic-based techniques: GOA, CSO, BBBC, coyote, crow search, genetic algorithm, and BOA, in achieving the best size of the HES microgrid with the lowest ASC (USD 149229.9) and convergence rate. The four metaheuristicbased techniques (HHO, GOA, CSO, and coyote) exhibit an acceptable performance in terms of global solution capture with fewer oscillations and convergence rate, whereas the four metaheuristic-based techniques (BBBC, crow search, genetic algorithm, and BOA) have poor and unacceptable performance, resulting in local solution trapping instead of global solution, obvious oscillations to find solution, and a high convergence rate. In terms of optimal solution and convergence rate, the BBBC and GA have bad performance in comparison to other metaheuristic-based optimization approaches. The reason behind this is that both BBBC and GA have a high standard deviation. The high standard deviation indicates that the best solutions are widely dispersed, and both techniques could end up with a local solution. Future work necessitates the improvement of the HHO to increase population diversity in the search space while decreasing consumption time.

#### **Data Availability**

The data used to support the findings of this study are available from the corresponding author upon request.

#### **Conflicts of Interest**

The authors declare that they have no conflicts of interest.

#### Acknowledgments

The authors would like to acknowledge the Researchers Supporting Project number RSP-2021/337, King Saud University, Riyadh, Saudi Arabia.

#### References

- H. Wang, Z. Lei, X. Zhang, B. Zhou, and J. Peng, "A review of deep learning for renewable energy forecasting," *Energy Con*version and Management, vol. 198, p. 111799, 2019.

- [2] P. Arévalo-Cordero, D. J. Benavides, J. L. Espinoza, L. Hernández-Callejo, and F. Jurado, "Optimal energy management strategies to reduce diesel consumption for a hybrid off-grid system," *Revista Facultad de Ingeniería Universidad de Antioquia*, no. 98, pp. 47–58, 2021.

- [3] J. Lian, Y. Zhang, C. Ma, Y. Yang, and E. Chaima, "A review on recent sizing methodologies of hybrid renewable energy systems," *Energy Conversion and Management*, vol. 199, p. 112027, 2019.

- [4] L. G. Acuna, R. V. Padilla, and A. S. Mercado, "Measuring reliability of hybrid photovoltaic-wind energy systems: a new indicator," *Renewable Energy*, vol. 106, pp. 68–77, 2017.

- [5] S. Twaha and M. A. Ramli, "A review of optimization approaches for hybrid distributed energy generation systems: off-grid and grid-connected systems," *Sustainable Cities and Society*, vol. 41, pp. 320–331, 2018.

- [6] A. Bouabdallah, J. Olivier, S. Bourguet, M. Machmoum, and E. Schaeffer, "Safe sizing methodology applied to a standalone photovoltaic system," *Renewable Energy*, vol. 80, pp. 266–274, 2015.

- [7] H. Belmili, M. Haddadi, S. Bacha, M. F. Almi, and B. Bendib, "Sizing stand-alone photovoltaic-wind hybrid system: techno-economic analysis and optimization," *Renewable and Sustainable Energy Reviews*, vol. 30, pp. 821–832, 2014.

- [8] C. Delgado-Antillón and J. Domínguez-Navarro, "Probabilistic siting and sizing of energy storage systems in distribution power systems based on the islanding feature," *Electric Power Systems Research*, vol. 155, pp. 225–235, 2018.

- [9] S. Sanajaoba and E. Fernandez, "Maiden application of cuckoo search algorithm for optimal sizing of a remote hybrid renewable energy system," *Renewable Energy*, vol. 96, pp. 1–10, 2016.

- [10] H. M. Farh, A. M. Al-Shaalan, A. M. Eltamaly, and A. A. Al-Shamma'a, "A novel severity performance index for optimal allocation and sizing of photovoltaic distributed generations," *Energy Reports*, vol. 6, pp. 2180–2190, 2020.

- [11] A. Berrueta, M. Heck, M. Jantsch, A. Ursúa, and P. Sanchis, "Combined dynamic programming and region-elimination technique algorithm for optimal sizing and management of lithium-ion batteries for photovoltaic plants," *Applied Energy*, vol. 228, pp. 1–11, 2018.

- [12] H. M. Farh, A. M. Eltamaly, A. M. Al-Shaalan, and A. A. Al-Shamma'a, "A novel sizing inherits allocation strategy of renewable distributed generations using crow search combined with particle swarm optimization algorithm," *IET Renewable Power Generation*, vol. 15, no. 7, pp. 1436–1450, 2021.

- [13] F. Ali, M. Ahmar, Y. Jiang, and M. AlAhmad, "A technoeconomic assessment of hybrid energy system in rural Pakistan," *Energy*, vol. 215, article 119103, 2021.

- [14] G. Veilleux, T. Potisat, D. Pezim et al., "Techno-economic analysis of microgrid projects for rural electrification: a systematic approach to the redesign of Koh Jik off-grid case study," *Energy for Sustainable Development*, vol. 54, pp. 1–13, 2020.

- [15] O. D. T. Odou, R. Bhandari, and R. Adamou, "Hybrid off-grid renewable power system for sustainable rural electrification in Benin," *Renewable Energy*, vol. 145, pp. 1266–1279, 2020.

- [16] A. Q. Jakhrani, A.-K. Othman, A. R. H. Rigit, S. R. Samo, and S. A. Kamboh, "A novel analytical model for optimal sizing of standalone photovoltaic systems," *Energy*, vol. 46, no. 1, pp. 675–682, 2012.

- [17] D. Q. Hung, N. Mithulananthan, and R. Bansal, "Analytical strategies for renewable distributed generation integration considering energy loss minimization," *Applied Energy*, vol. 105, pp. 75–85, 2013.

- [18] S. Sinha and S. Chandel, "Review of recent trends in optimization techniques for solar photovoltaic-wind based hybrid energy systems," *Renewable and Sustainable Energy Reviews*, vol. 50, pp. 755–769, 2015.

- [19] T. Markvart, "Sizing of hybrid photovoltaic-wind energy systems," *Solar Energy*, vol. 57, no. 4, pp. 277–281, 1996.

- [20] S. Upadhyay and M. Sharma, "A review on configurations, control and sizing methodologies of hybrid energy systems," *Renewable and Sustainable Energy Reviews*, vol. 38, pp. 47– 63, 2014.

- [21] C. V. T. Cabral, D. Oliveira Filho, A. S. A. C. Diniz, J. H. Martins, O. M. Toledo, and B. Lauro de Vilhena, "A stochastic method for stand-alone photovoltaic system sizing," *Solar Energy*, vol. 84, no. 9, pp. 1628–1636, 2010.

- [22] T. Khatib, I. A. Ibrahim, and A. Mohamed, "A review on sizing methodologies of photovoltaic array and storage battery in a standalone photovoltaic system," *Energy Conversion and Management*, vol. 120, pp. 430–448, 2016.

- [23] A. Giallanza, M. Porretto, G. L. Puma, and G. Marannano, "A sizing approach for stand-alone hybrid photovoltaic-windbattery systems: a Sicilian case study," *Journal of Cleaner Production*, vol. 199, pp. 817–830, 2018.

- [24] P. Rullo, L. Braccia, P. Luppi, D. Zumoffen, and D. Feroldi, "Integration of sizing and energy management based on economic predictive control for standalone hybrid renewable energy systems," *Renewable Energy*, vol. 140, pp. 436–451, 2019.

- [25] J. Mahmoudimehr and M. Shabani, "Optimal design of hybrid photovoltaic-hydroelectric standalone energy system for north and south of Iran," *Renewable Energy*, vol. 115, pp. 238–251, 2018.

- [26] Y. Zhang, C. Ma, J. Lian, X. Pang, Y. Qiao, and E. Chaima, "Optimal photovoltaic capacity of large-scale hydrophotovoltaic complementary systems considering electricity delivery demand and reservoir characteristics," *Energy Conversion and Management*, vol. 195, pp. 597–608, 2019.

- [27] U. Portero, S. Velázquez, and J. A. Carta, "Sizing of a windhydro system using a reversible hydraulic facility with seawater. A case study in the Canary Islands," *Energy Conversion and Management*, vol. 106, pp. 1251–1263, 2015.

- [28] O. Erdinc, N. G. Paterakis, I. N. Pappi, A. G. Bakirtzis, and J. P. Catalão, "A new perspective for sizing of distributed

generation and energy storage for smart households under demand response," *Applied Energy*, vol. 143, pp. 26–37, 2015.

- [29] A. Maleki, M. G. Khajeh, and M. Ameri, "Optimal sizing of a grid independent hybrid renewable energy system incorporating resource uncertainty, and load uncertainty," *International Journal of Electrical Power & Energy Systems*, vol. 83, pp. 514– 524, 2016.

- [30] M. J. Mayer, A. Szilágyi, and G. Gróf, "Environmental and economic multi-objective optimization of a household level hybrid renewable energy system by genetic algorithm," *Applied Energy*, vol. 269, article 115058, 2020.

- [31] R. Dufo-López, J. L. Bernal-Agustín, J. M. Yusta-Loyo et al., "Multi-objective optimization minimizing cost and life cycle emissions of stand-alone PV-wind-diesel systems with batteries storage," *Applied Energy*, vol. 88, no. 11, pp. 4033–4041, 2011.

- [32] M. Das, M. A. K. Singh, and A. Biswas, "Techno-economic optimization of an off-grid hybrid renewable energy system using metaheuristic optimization approaches - case of a radio transmitter station in India," *Energy Conversion and Management*, vol. 185, pp. 339–352, 2019.

- [33] S. Abedi, A. Alimardani, G. Gharehpetian, G. Riahy, and S. Hosseinian, "A comprehensive method for optimal power management and design of hybrid RES- based autonomous energy systems," *Renewable and Sustainable Energy Reviews*, vol. 16, no. 3, pp. 1577–1587, 2012.

- [34] J. Zhao and X. Yuan, "Multi-objective optimization of standalone hybrid PV-wind-diesel-battery system using improved fruit fly optimization algorithm," *Soft Computing*, vol. 20, no. 7, pp. 2841–2853, 2016.

- [35] B. Shi, W. Wu, and L. Yan, "Size optimization of stand-alone PV/wind/diesel hybrid power generation systems," *Journal of the Taiwan Institute of Chemical Engineers*, vol. 73, pp. 93– 101, 2017.

- [36] A. Tabak, E. Kayabasi, M. T. Guneser, and M. Ozkaymak, "Grey wolf optimization for optimum sizing and controlling of a PV/WT/BM hybrid energy system considering TNPC, LPSP, and LCOE concepts," *Energy Sources, Part A: Recovery, Utilization, and Environmental Effects*, vol. 44, no. 1, pp. 1508– 1528, 2022.

- [37] S. Ahmadi and S. Abdi, "Application of the hybrid Big Bang-Big Crunch algorithm for optimal sizing of a stand-alone hybrid PV/wind/battery system," *Solar Energy*, vol. 134, pp. 366–374, 2016.

- [38] A. Fetanat and E. Khorasaninejad, "Size optimization for hybrid photovoltaic-wind energy system using ant colony optimization for continuous domains based integer programming," *Applied Soft Computing*, vol. 31, pp. 196–209, 2015.

- [39] Y. A. Katsigiannis, P. S. Georgilakis, and E. S. Karapidakis, "Hybrid simulated annealing-tabu search method for optimal sizing of autonomous power systems with renewables," *IEEE Transactions on Sustainable Energy*, vol. 3, no. 3, pp. 330– 338, 2012.

- [40] A. A. Z. Diab, A. M. El-Rifaie, M. M. Zaky, and M. A. Tolba, "Optimal sizing of stand-alone microgrids based on recent metaheuristic algorithms," *Mathematics*, vol. 10, no. 1, p. 140, 2022.

- [41] H. M. Farh, A. A. Al-Shamma'a, A. M. Al-Shaalan, A. Alkuhayli, A. M. Noman, and T. Kandil, "Technical and economic evaluation for off-grid hybrid renewable energy system using novel Bonobo optimizer," *Sustainability*, vol. 14, no. 3, p. 1533, 2022.

- [42] H. O. Omotoso, A. M. Al-Shaalan, H. M. Farh, and A. A. Al-Shamma'a "Techno-economic evaluation of hybrid energy

- Shamma'a, "Techno-economic evaluation of hybrid energy systems using artificial ecosystem-based optimization with demand side management," *Electronics*, vol. 11, no. 2, p. 204, 2022.

- [43] Y. Wang, J. Wang, L. Yang, B. Ma, G. Sun, and N. Youssefi, "Optimal designing of a hybrid renewable energy system connected to an unreliable grid based on enhanced African vulture optimizer," *ISA Transactions*, 2022.

- [44] Y. Guo, X. Dai, K. Jermsittiparsert, and N. Razmjooy, "An optimal configuration for a battery and PEM fuel cell-based hybrid energy system using developed krill herd optimization algorithm for locomotive application," *Energy Reports*, vol. 6, pp. 885–894, 2020.

- [45] J. Pierezan and L. D. S. Coelho, "Coyote optimization algorithm: a new metaheuristic for global optimization problems," in 2018 IEEE congress on evolutionary computation (CEC), pp. 1–8, Rio de Janeiro, Brazil, 2018.

- [46] A. Elbaz and M. T. Güneşer, "Using crow algorithm for optimizing size of wind power plant/hybrid PV in Libya," in 2019 3rd International Symposium on Multidisciplinary Studies and Innovative Technologies (ISMSIT), pp. 1–4, Ankara, Turkey, 2019.

- [47] S. Arora and S. Singh, "Butterfly optimization algorithm: a novel approach for global optimization," *Soft Computing*, vol. 23, no. 3, pp. 715–734, 2019.

- [48] F. A. Alturki, H. M. H. Farh, A. A. Al-Shamma'a, and K. AlSharabi, "Techno-economic optimization of small-scale hybrid energy systems using manta ray foraging optimizer," *Electronics*, vol. 9, no. 12, p. 2045, 2020.

- [49] F. A. Alturki, A. A. Al-Shamma'a, H. M. Farh, and K. AlSharabi, "Optimal sizing of autonomous hybrid energy system using supply-demand-based optimization algorithm," *International Journal of Energy Research*, vol. 45, no. 1, pp. 605–625, 2021.

- [50] A. A. Al-Shamma'a, F. A. Alturki, and H. M. Farh, "Technoeconomic assessment for energy transition from diesel-based to hybrid energy system-based off-grids in Saudi Arabia," *Energy Transitions*, vol. 4, no. 1, pp. 31–43, 2020.

- [51] A. A. Heidari, S. Mirjalili, H. Faris, I. Aljarah, M. Mafarja, and H. Chen, "Harris hawks optimization: algorithm and applications," *Future Generation Computer Systems*, vol. 97, pp. 849–872, 2019.

### Research Article

## Design of Boosted Multilevel DC-DC Converter for Solar Photovoltaic System

# R. Uthirasamy,<sup>1</sup> V. Kumar Chinnaiyan,<sup>1</sup> S. Vishnukumar,<sup>2</sup> Alagar Karthick,<sup>1</sup> V. Mohanavel,<sup>3</sup> Umashankar Subramaniam,<sup>4</sup> and M. Muhibbullah,<sup>5</sup>

<sup>1</sup>Renewable Energy Lab, Department of Electrical and Electronics Engineering, KPR Institute of Engineering and Technology, 641407, Coimbatore, Tamilnadu, India

<sup>2</sup>Department of Electronics and Communication Engineering Vel Tech Rangarajan Dr. Saguthala R&D Institute of Science and Technology, 600062, Chennai, Tamilnadu, India

- <sup>3</sup>Centre for Materials Engineering and Regenerative Medicine, Bharath Institute of Higher Education and Research, 600073 Chennai, Tamilnadu, India

- <sup>4</sup>Department of Communications and Networks, Renewable Energy Laboratory, College of Engineering, Prince Sultan University, Riyadh 11586, Saudi Arabia

<sup>5</sup>Department of Electrical and Electronic Engineering, Bangladesh University, Dhaka 1207, Bangladesh

Correspondence should be addressed to M. Muhibbullah; m.muhibbullah@bu.edu.bd

Received 13 October 2021; Revised 11 November 2021; Accepted 15 November 2021; Published 5 January 2022

Academic Editor: Abdullrahman Alshammaa

Copyright © 2022 R. Uthirasamy et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

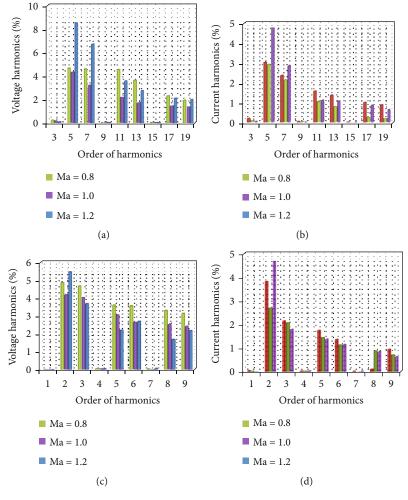

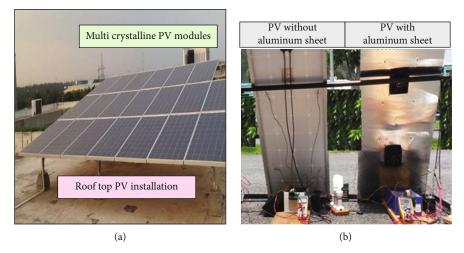

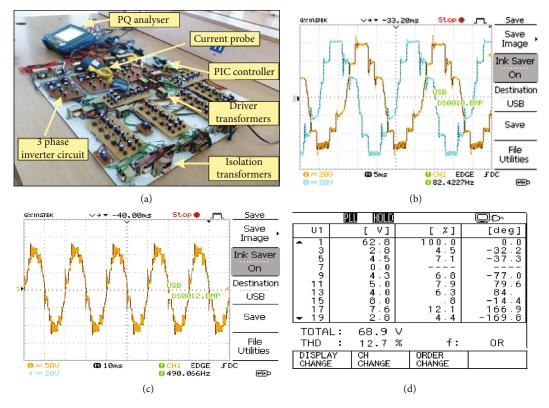

Integration of renewable energy sources to the grid-connected system has influenced scholarly research in recent times to evolve solutions for power electronic conversion. Particularly, solar photovoltaic (SPV), being a resource available throughout the year, demands needful research to meet the demand for industrial applications. To facilitate SPV, multilevel inverters (MLIs) and cascaded H-bridge inverters (CHBIs) are proposed in the literature to meet the power requirement. However, these circuits suffer from efficiency loss, economic aspects of DC sources usage, and switching losses. Hence, in this research, a new power converter topology is projected to improve the overall efficiency of SPV systems. Further, a three-level approach involving (i) SPV Panel-Temperature Reduction (SPV-PTR) Setup, (ii) Boost Multilevel Direct Current Link Converter (BMLDCLC), and (iii) use of effective snubber modules (SM) are effectively handled to promote the industry readiness of the proposed system. From a detailed system investigation, it is seen that the proposed arrangement has minimized the power loss to ensure better quality in output. Furthermore, the software-based results and hardware setup of the planned comprehensive converter have shown promising results in terms of (i) reduced voltage stress, (ii) reduced total harmonic distortion (THD) without filter component, and (iii) reduced power loss. It is observed that the experimental setup has reported a 12.9% of excess heat removal, 5% decrease in harmonics, and 33% switch reduction than the existing MLI schemes. In addition, the proposed setup is suggested to apply for industrial purposes indicate its efficacy to be a solution in real time.

#### 1. Introduction

Alarming environmental concerns and exhaustion of fossil fuels have invoked the necessity of eco-friendly power generation via renewable energy resources [1]. Having the superiority to reduce greenhouse emissions, renewable energy is considered as one of the essential tools to avoid energy import. In particular, SPV systems have gained monumental recognition to emerge as a resource of the decade. Zero maintenance, harmless operation, abundant availability, and easy portability are its inherent merits over other renewable energy resources.

In general, SPV modules are constant voltage sources fed to a load via power conditioning circuits. However, fabricating an efficient and cost-effective converter prototype model is really challenging. Since the power conditioning circuitries are implemented over two or three-level converters, interfacing PV panels for high power application become complex and uncertain. More importantly, sequential power electronic switching with three-level converters renders excessive voltage stress across the converter. This results in stressed transmission. Therefore, a supplementary snubber circuit at the output is mandated to reduce the transient power loss [2]. In addition, bulky filter components are also used to tap the hassle-free sinusoidal output. However, the system cost is increased beside the additional usage of transformers on the output side [3].

As an alternative to three-level converters, researchers have used multiple topologies with multilevel inverters (MLIs). It is important to note here that the advent of MLIs has enabled the efficient interface with multiple electrical applications such as (i) uninterrupted power supply (UPS) systems, (ii) motor drives, (iii) integration of renewable energy systems, (iv) static compensator, and (v) renewable energy sources [4-8]. Though MLIs have exhibited their significant merits from the end-user side, they are penalized with the necessity of high (i) power-switching components, (ii) regulator units, (iii) power supply units, (iv) gate driver circuits, (v) protection units, and (vi) DC sources to reduce its popularity [9-16]. This certainly increases the manufacturing cost of the system. Out of many configurations in MLI, a few important works in literature are presented as the review in the following. A typical nine-level multilevel inverter for induction motor application is presented in [9]. Also, the importance of high-frequency switches to control uncertainty and voltage diversity factor is critically analyzed in this research. With an objective to reduce power electronic switches, a seven-level MLI with three sources is presented in [10]. Alternatively, a nine-level MLI design with four DC sources is presented in [11]. Notably, usage of limited (twelve) Metal Oxide Semiconductor Field Effective Transistor (MOSFET) switch has gained research interest to reduce THD. However, all the aforementioned works have the drawbacks of (i) design of control circuit, (ii) elimination of lower-order harmonics, and (iii) requirement of high switching devices. Hence, a novel H-bridge-based MLI system has been proposed in [12]. But then, the research necessitates an additional DC source which remains an important downside of the topology. Sequentially to limit the source count with MLI, a seven-level MLI with only three DC sources is proposed in [13]. However, twelve controlled semiconductor switches are used. With a motive to reduce power electronic switches, a similar MLI design with eight controlled semiconductor switches is proposed in [14]. Using only three sources, the same seven-level MLI topologies are presented in [15, 16]. Nevertheless, usage of power semiconductor switches was found high compared to [14].

At the outset, in comparison to various topologies discussed in [13–20], it is seen that the output voltage is achieved either by a series connection of DC sources or using a transformer at the inverter side. Thus, it becomes a nonviable solution for grid-connected systems economically. Note that power losses are also increased due to the usage of the bulky transformer. This invokes a power converter system to maintain the nominal voltage at the DC link, and it is achieved by using appropriate DC to DC power converters. Alternatively, cascaded H-bridge inverters among MLI are also proposed in the literature. Owing to the simpler and lucid circuitry, few research works are reported by using cascaded H-bridge inverters (CHBIs) in [17–20]. In comparison over two or three-level inverters, the use of CHBI offers multiple salient features such as (i) meagre transient across the inverter, (ii) reduced total harmonic distortion (THD) without filter component, and (iii) less significant filter components.

Commencing from the extensive review survey, it is seen that there exist a wide gap in formulating an MLI with the following advantages: (i) limited DC sources, (ii) less stress on the converter, (iii) less THD, and (iv) limited use of power electronic switches. Therefore, a new and novel seven-level stepped DC-link converter is proposed in this research. In addition, the converter is integrated with the PV source to check its viability for industry applications. In order to appreciate the panel temperature within limits, an exclusive prototype testing of PV with an aluminum sheet supported by a DC fan for cooling arrangement is performed. It is important to note here that PV panels are provided with a hydrophobic nano coating (HNC) solution to avoid dust accumulation and stagnant water droplets on PV panels. This helps the PV to shield itself from corrosion, thus increasing the lifetime for its continued quality of operation. The distinguished merits of the proposed research are summarized in the following.

- (i) A new seven-level stepped DC-link MLI with reduced stress on the converter is proposed for the first time

- (ii) The seven-level stepped DC-link converters are interfaced with the PV module, and their industrial viability is studied

- (iii) To subside the panel temperature in real time, the cooling arrangement is provided via aluminum sheet and DC fans

- (iv) To enable durability and long sustainability with PV, hydrophobic nano coating (HNC) is used

- (v) The use of two PV sources at the input side per phase eliminates the unnecessary stress on the converter

The entire paper is ordered as follows. In Section 2, PV modelling and design of DC-DC boost converter is detailed. In Section 3, the proposed converter design and its design constraints are given. Software-based results and hardware realization are given in Sections 4 and 5, respectively. To contribute to a fair comparative study, the usage of power electronic components and their losses are analyzed and compared in Section 6. Conclusions are addressed as the summary in Section 7.

#### 2. PV Modelling

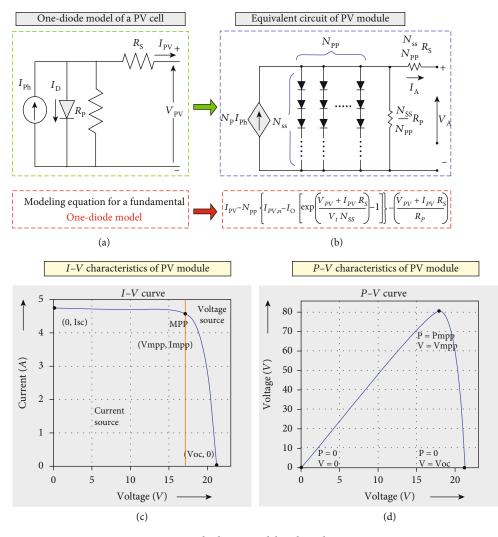

One-diode PV models are prevalently popular to use for simulation investigations. The representation of the corresponding electrical circuit of one diode PV model is represented in Figure 1 [21–23], and for better understanding,

FIGURE 1: One-diode PV model and its characteristics.

the I-V and P-V distinctiveness of a PV module are also presented in the same figure. From the characteristics, it is seen that PV operates at a unique operating point where maximum power can be extracted. In addition, PV demands a power electronic interface to enable its smoother operation. The PV output current [23] by applying KCL is given by

$$I_{\rm PV} = I_{Ph} - I_D - \frac{V + I_{\rm PV} Rs}{Rp}.$$

(1)

The ideal diode current equation is mathematically given in Equation (2).

$$I_{D} = I_{O} \left( e^{V_{D} / \alpha V_{T}} - 1 \right), \tag{2}$$

where " $I_o$ " is the reverse saturation current, "*a*" is the diode ideality factor, and " $V_T$ " is the thermal voltage proportional to temperature changes which is given by

$$V_T = \frac{N_S KT}{q},\tag{3}$$

where " $N_s$ " is the number of cells connected in series, "K" is the Boltzmann constant, "T" is the temperature at STC, and "Q" is the charge of the electron 1.9 \* 10<sup>-19</sup>C. On incorporating " $I_D$ " in " $I_{PV}$ ," then the output current equation (24) becomes

$$I_{\rm PV} = N_{pp} \left\{ I_{Ph} - I_O \left[ \exp\left(\frac{V_{PV} + I_{\rm PV} R_S}{V_t N_{ss}}\right) - 1 \right] \right\} - \left(\frac{V_{\rm PV} + I_{\rm PV} R_S}{R_p}\right),$$

(4)

where " $N_{SS}$ " and " $N_{PP}$ " are the numbers of cells connected in series and parallel [24, 25].

#### 3. Multilevel Stepped DC-Link Converter

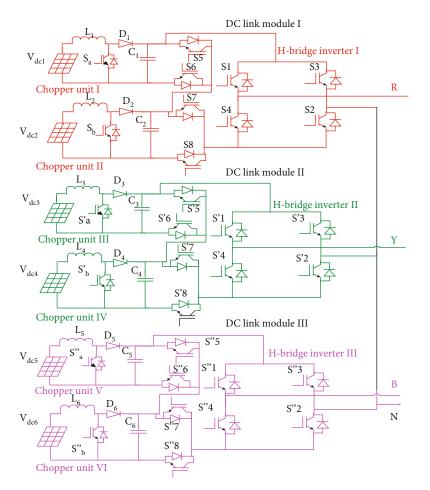

Further, synthesizing sinusoidal voltage with less harmonic using multiple DC sources is its unique characteristic. Note that three-phase multilevel inverters gain more attention since each individual phase requires an "N" number of DC sources to obtain a "2N +" voltage output level. However, MLI greatly suffers due to the requirement for an increased

FIGURE 2: Equivalent circuit of three-phase seven-level BMLDCLC.

number of power electronic components, and this is reduced by using Boosted Multilevel DC Line Converter design. One such configuration with PV as the source is proposed in this research. The operating modes and their analysis on output voltage are discussed in the following.

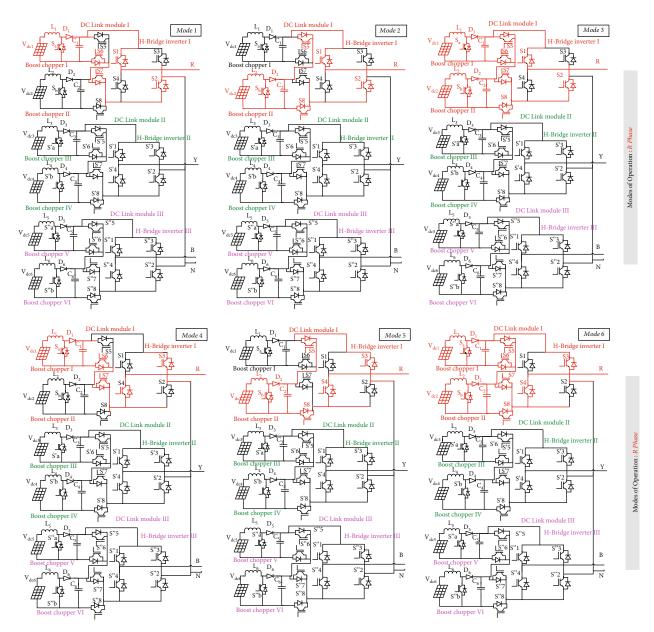

3.1. Design of Boosted Multilevel DC-Link Converter (BMLDCLC). The schematic of the projected seven-level BMLDCLC circuit is represented in Figure 2. For understanding, each phase is highlighted in different colors and named in the convention as R phase, Y phase, and B phase. Note that each phase is provided with a provision to switch on and off to maintain the output voltage in limits. Further, the boost converter is interfaced among the MLI and PV sources. This eliminates the necessity of a transformer and thus improving the cost efficiency of the converter. Further, the equivalent circuit of BMLDCLC clearly shows that boost chopper takes responsibility to uphold DC-link voltage across each phase. In addition, two power sources are used in each phase reduces the stress on converter is a notable merit of proposed converter. The generalized equations (12-14) to estimate the power components, sources, and level of single-phase BMLDCLC are presented in Equations (5)–(7).

$$N_{\text{switch}} = 2s + 4H + b, \tag{5}$$

$$n = 2(H+1)^s - 1, (6)$$

$$H = n - (n - 1), \tag{7}$$

where "s" is the DC source count, "n" is the number of levels, "H" is the number of converter topology at load end, and "b" represents boost converter.

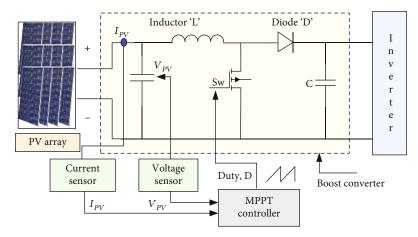

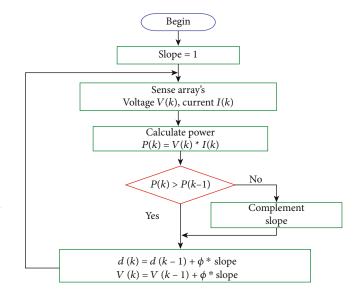

3.2. Design of Boosted Multilevel DC-Link Converter (BMLDCLC). The DC-DC boost converter is an integral part of the proposed converter design. Further, it is connected to the inverter via switching circuitry to generate AC waveforms. The schematic of the DC-DC boost converter is presented in Figure 3. Since PV is a constant voltage source, the task of boosting converter becomes much easier to maintain constant DC-link voltage across the inverter. As a known fact that PV is a nonlinear DC source, the system demands a maximum power point controller to track the MPP. To achieve this, each PV panel is provided with a current and voltage sensor to track the unique operating point where the highest accessible power is able to be pulled out. Note that a simple perturb and observe (P&O) algorithm is employed to appreciate simplicity. Besides, the necessity of a metaheuristic algorithm is not required since only one module is used as a DC source [26-30]. For brevity, the flowchart of the P&O algorithm is presented in Figure 4.

FIGURE 3: Representation of DC-DC boost converter.

In general, P&O works on the standard that repeated perturbation in voltage is made until the MPP is tracked. Based on the power values, the duty cycle of the boost chopper is altered [11]. Duty cycle equation of the boost chopper is given in the following.

$$D = \frac{V_o - V_s}{V_o},\tag{8}$$

where " $V_o$ " and " $V_s$ " are the voltage across the load and source voltage, respectively, and "D" is the duty cycle. Further, the design considerations of boost chopper are given in the following. It is always ensured that the boost chopper is worked in continuous conduction mode, and the design of inductor "L" is made by following the equation given in (9).

$$L = \frac{V_o(1-D)}{\Delta i_I f_s},\tag{9}$$

where " $\Delta i_L$ " is the inductor current  $(i_2 - i_1)$  and " $f_s$ " is the switching frequency. For better output quality, 3% current ripple is considered for designing the inductor. Capacitor design is made by following the equation given in (10).

$$C = \frac{1 - D}{8L(\Delta V_o/V_o)f_s^2},\tag{10}$$

where  $f_s = 1/T$  is the switching frequency and " $\Delta V_o/V_o$ " is the voltage ripple, and it is approximately considered as 3%.

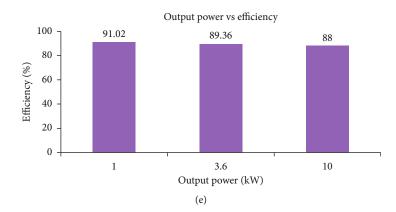

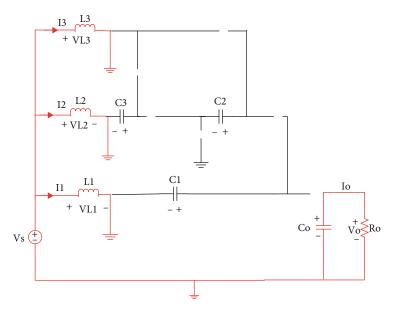

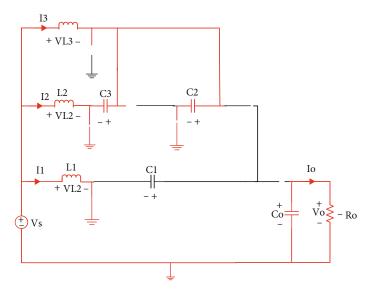

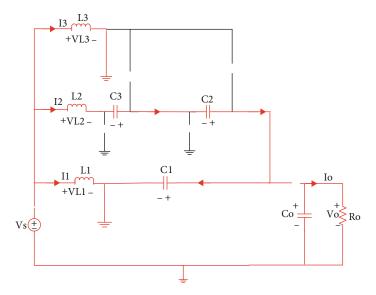

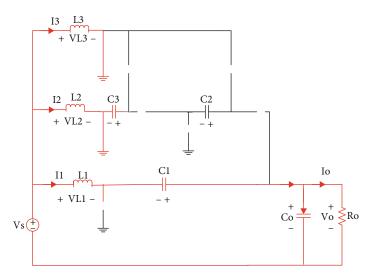

3.2.1. Modes of Operation of Boosted Multilevel DC-Link Converter (BMLDCLC). The proposed Boosted Multilevel DC-Link Converter (BMLDCLC) is designed for 3-phase load, and each phase constitutes six different operating modes. A detailed discussion on its working is given in the following.

(1) Modes of Operations in "R" Phase. During the first and fourth modes of operation, the source voltage " $V_{dc1}$ "is boosted by turning on the switch  $S_a$ . The mathematical expression for " $V_{dc1}$ " is given.

FIGURE 4: Perturb and observe algorithm for MPP tracking.

In Equations (8) and (9), further, the switches  $S_6$  and  $S_7$  are made to behaviour to attain the voltage level " $V_{ob1}$ " at the inverter side.

$$V_{\rm dc1} = L_1 \frac{I_2 - I_1}{T_{\rm on1}},\tag{11}$$

$$V_{\rm dc1} = L_1 \frac{dI_1}{dt}.$$

(12)

The energy stored in the inductor " $E_{i1}$ " can be calculated by using Equation (6).

$$E_{i1} = V_{dc1} I_{s1} T_{on1}.$$

(13)

At the time,  $t = T_{off1}$ , switch  $S_a$  is made to switch off, and hence, source current flows through L from  $I_2$

FIGURE 5: Continued.

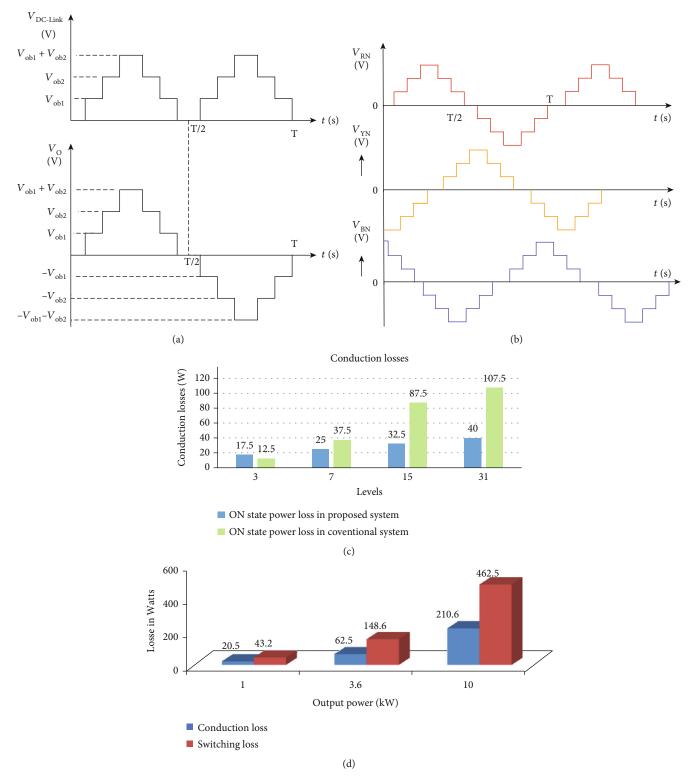

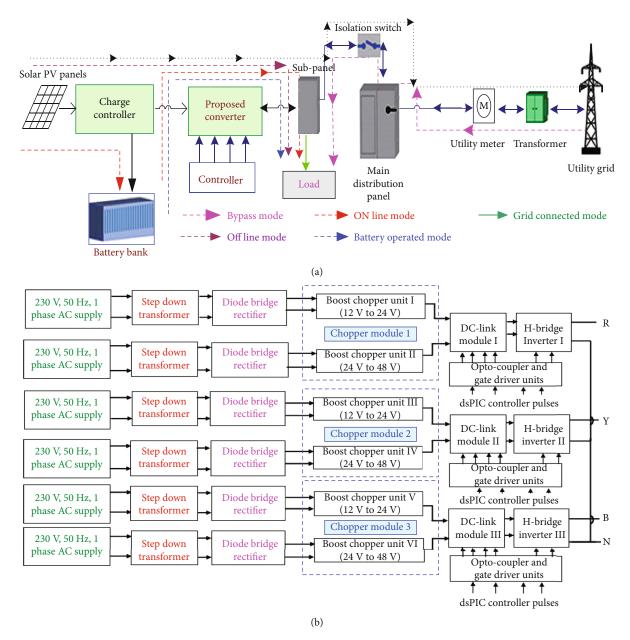

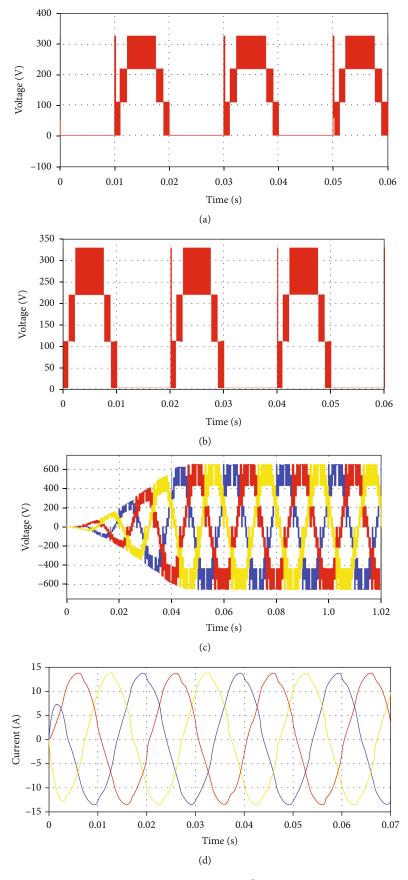

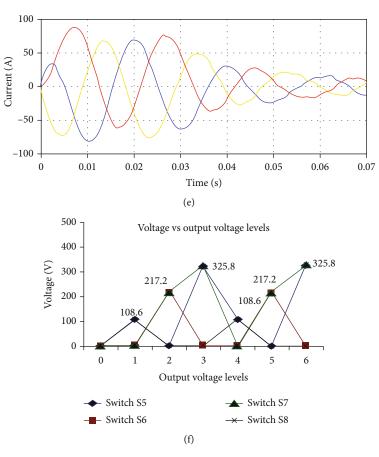

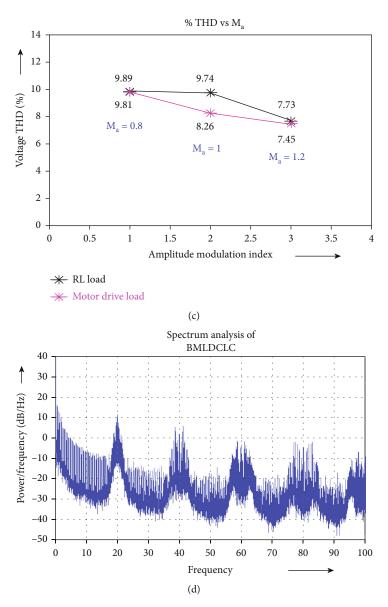

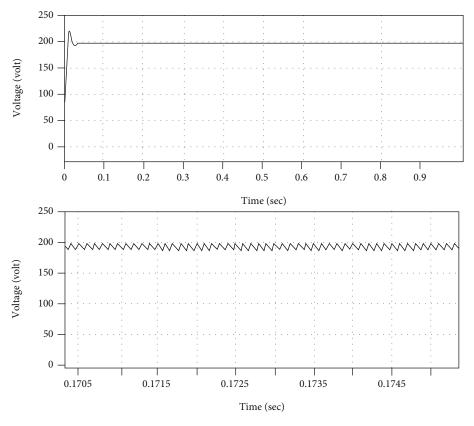

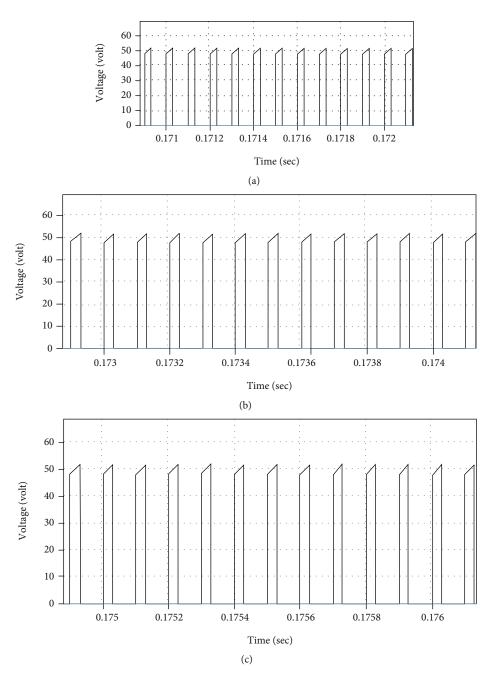

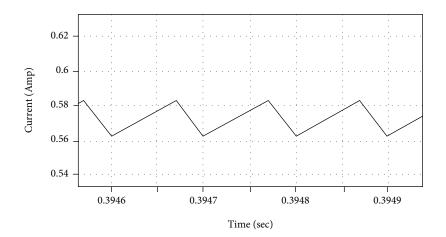

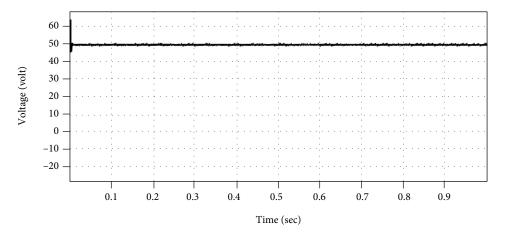

FIGURE 5: (a) Distinctive voltage waveform of 1 $\Phi$  seven-level BMLDCLC. (b) Characteristic output voltage waveform of 3 $\Phi$  BMLDCLC. (c) Analysis of conduction loss of BMLDCLC. (e) Losses and efficiency.

to  $I_1$ . Therefore, the average output voltage at DC to DC boost converter I can be expressed as Equation (14)

$$V_{ob1} = V_{dc1} + L_1 \frac{dI_{s1}}{T_{off1}}.$$

(14)

The energy release  $E_{o1}$  at this instant can be calculated using Equation (15).

$$E_{o1} = (V_{ob1} - V_{dc1})I_{s1}.T_{off1}.$$

(15)

The output voltage of boost converter I of R phase is thus attained as in Equation (16).

$$V_{ob1} = \frac{V_{dc1}}{1 - K_1}.$$

(16)

The change in capacitor voltage can be calculated by using Equation (17).

$$\Delta V_{C1} = I_{o1} * \left[ \frac{V_{ob1} - L_1(I_2 - I_1)}{V_{ob1} * f * C_1} \right].$$

(17)

In the second and fifth switching schemes of the chopper unit, the PV source voltage  $V_{dc2}$  is boosted to  $V_{ob2}$  by turning on the switch  $S_b$  in the boost chopper, while  $S_5$  and  $S_8$  are used as a snubber. At this time period,  $t = T_{on2}$ ; switch  $S_b$  of chopper unit-II is turned on to raise the inductor current  $I_3$  and  $I_4$  linearly. The voltage and energy equation corresponding to inductor  $L_2$  is equated in Equations (18) and (19).

$$V_{\rm dc2} = L_2 \frac{I_4 - I_3}{T_{\rm on2}},\tag{18}$$

$$E_{i2} = V_{\rm dc2}.I_{s2}.T_{\rm on2},\tag{19}$$

where  $I_3$  is the current flowing through the inductor during boost operation in boost chopper unit-II and  $I_2$ is the current flowing through the inductor due to  $S_b$ in boost chopper unit-II. During  $t = T_{off2}$ , switch  $S_b$  of the chopper-II unit gets turned off, because of which, the current through  $L_2$  linearly falls from  $I_4$  to  $I_3$ . The expression pertaining to the average output voltage and energy stored in the boost chopper IV is given in the following equations:

$$V_{ob2} = V_{dc2} + L_2 \frac{dI_{s2}}{T_{off2}},$$

(20)

$$E_{o2} = (V_{ob2} - V_{dc2})I_{s2}.T_{off2}.$$

(21)

For schemes 3 and 6, the source voltage  $V_{dc1}$  and  $V_{dc2}$  are stepped up to obtain  $V_{ob1}$  and  $V_{ob2}$  by turning on switches  $S_a$  and  $S_b$  of DC-to-DC boost converter. During conduction,  $S_6$  and  $S_8$  act as a snubber to protect the boost converter switches. During the turn-on period ( $t = T_{on3}$ ), switches  $S_a$  and  $S_b$  remain conducting to linearly rise the inductor current  $L_1$  and  $L_2$  from  $I_1$  to  $I_2$  and from  $I_3$  to  $I_4$  respectively. The input energy of inductor  $L_1$  from the source voltage  $V_{dc1}$  is given in Equation (22).

$$E_{i3} = (V_{dc1} + V_{dc2}) \cdot (I_{s1} + I_{s2}) \cdot T_{on3},$$

(22)

The output phase voltage ( $V_{RN}$ ) of BMLDCLC is given as

$$V_{RN} = (V_{ob1} + V_{ob2}) \sin \omega t.$$

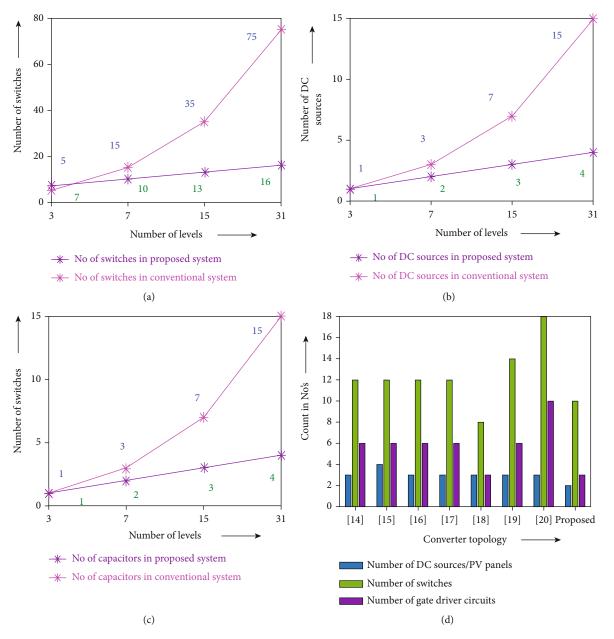

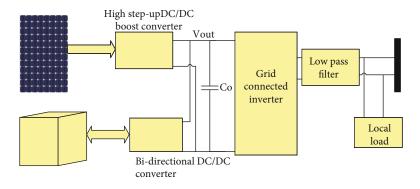

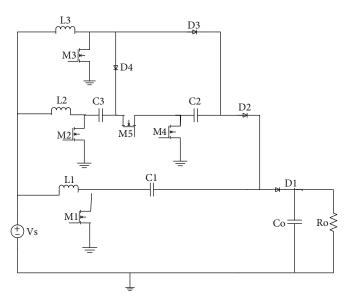

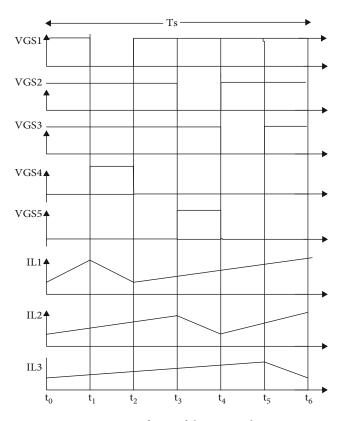

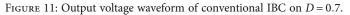

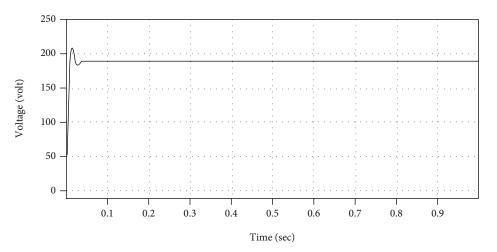

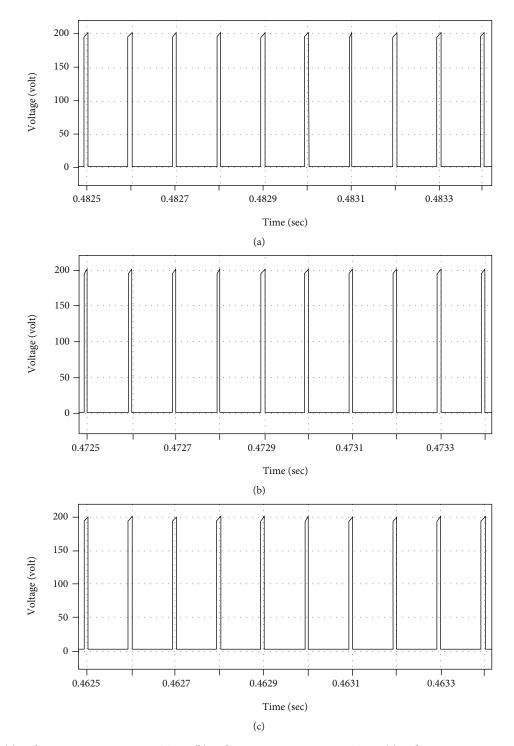

<sup>(23)</sup>