# Clock/Frequency Generation Circuits and Systems

Guest Editors: Wooqeun Rhee, Antonio Liscidini, Jae-Yoon Sim, Kenichi Okada, and Sudhakar Pamarti

# **Clock/Frequency Generation Circuits and Systems**

## **Clock/Frequency Generation Circuits and Systems**

Guest Editors: Woogeun Rhee, Antonio Liscidini, Jae-Yoon Sim, Kenichi Okada, and Sudhakar Pamarti

#### **Editorial Board**

The editorial board of the journal is organized into sections that correspond to the subject areas covered by the journal.

#### **Circuits and Systems**

M. T. Abuelma'atti, Saudi Arabia Ishfaq Ahmad, USA Dhamin Al-Khalili, Canada Wael M. Badawy, Canada Ivo Barbi, Brazil Martin A. Brooke, USA Chip Hong Chang, Singapore Y. W. Chang, Taiwan Tian-Sheuan Chang, Taiwan Tzi-Dar Chiueh, Taiwan Henry S. H. Chung, Hong Kong M. Jamal Deen, Canada Ahmed El Wakil, UAE Denis Flandre, Belgium P. Franzon, USA Andre Ivanov, Canada Ebroul Izquierdo, UK Wen-Ben Jone, USA

Yong-Bin Kim, USA H. Kuntman, Turkey Parag K. Lala, USA Shen-Iuan Liu, Taiwan Bin-Da Liu, Taiwan João A. Martino, Brazil Pianki Mazumder, USA Michel Nakhla, Canada Sing K. Nguang, New Zealand Shun-ichiro Ohmi, Japan Mohamed A. Osman, USA Ping Feng Pai, Taiwan Marcelo A. Pavanello, Brazil Marco Platzner, Germany Massimo Poncino, Italy Dhiraj K. Pradhan, UK F. Ren, USA

Gabriel Robins, USA Mohamad Sawan, Canada Raj Senani, India Gianluca Setti, Italy Jose Silva-Martinez, USA Ahmed M. Soliman, Egypt Dimitrios Soudris, Greece Charles E. Stroud, USA Ephraim Suhir, USA Hannu Tenhunen, Sweden George S. Tombras, Greece Spyros Tragoudas, USA Chi Kong Tse, Hong Kong Chi-Ying Tsui, Hong Kong Jan Van der Spiegel, USA Chin-Long Wey, USA

#### **Communications**

Sofiène Affes, Canada

Dharma Agrawal, USA

H. Arslan, USA

Edward Au, China

Enzo Baccarelli, Italy

Stefano Basagni, USA

Guoan Bi, Singapore

Jun Bi, China Z. Chen, Singapore

René Cumplido, Mexico

Luca De Nardis, Italy

M.-Gabriella Di Benedetto, Italy

J. Fiorina, France Lijia Ge, China

Z. Ghassemlooy, UK

K. Giridhar, India

Amoakoh Gyasi-Agyei, Ghana

Yaohui Jin, China Mandeep Jit Singh, Malaysia Peter Jung, Germany Adnan Kavak, Turkey Rajesh Khanna, India Kiseon Kim, Republic of Korea David Laurenson, UK Tho Le-Ngoc, Canada Cyril Leung, Canada Petri Mähönen, Germany Mohammad A. Matin, Bangladesh M. Nájar, Spain M. S. Obaidat, USA Adam Panagos, USA Samuel Pierre, Canada

Nikos C. Sagias, Greece John N. Sahalos, Greece Christian Schlegel, Canada Vinod Sharma, India Iickho Song, Korea Ioannis Tomkos, Greece Chien Cheng Tseng, Taiwan Theodoros Tsiftsis, Greece George Tsoulos, Greece Laura Vanzago, Italy Roberto Verdone, Italy Guosen Yue, USA Jian-Kang Zhang, Canada

#### **Signal Processing**

S. S. Agaian, USA Panajotis Agathoklis, Canada Jaakko Astola, Finland Tamal Bose, USA A. Constantinides, UK Paul Cristea, Romania Petar M. Djuric, USA Igor Djurović, Montenegro

Karen O. Egiazarian, Finland Woon Seng Gan, Singapore Z. F. Ghassemlooy, UK Ling Guan, Canada Martin Haardt, Germany Peter Handel, Sweden Alfred Hanssen, Norway Andreas Jakobsson, Sweden Jiri Jan, Czech Republic S. Jensen, Denmark Stefan Kaiser, Germany Chi Chung Ko, Singapore Lagunas Lagunas, Spain J. B. Lam, Hong Kong David Laurenson, UK Riccardo Leonardi, Italy Mark Liao, Taiwan Kai-Kuang Ma, Singapore S. Marshall, UK Magnus Mossberg, Sweden Antonio Napolitano, Italy Sven Nordholm, Australia Sethuraman Panchanathan, USA Periasamy K. Rajan, USA Cédric Richard, France W. Sandham, UK Ravi Sankar, USA Dan Schonfeld, USA Ling Shao, UK John J. Shynk, USA Andreas Spanias, USA Srdjan Stankovic, Montenegro Yannis Stylianou, Greece Ioan Tabus, Finland Jarmo Henrik Takala, Finland Ahmed H. Tewfik, USA Jitendra Kumar Tugnait, USA Vesa Valimaki, Finland Luc Vandendorpe, Belgium Ari J. Visa, Finland Jar Ferr Yang, Taiwan

#### **Contents**

**Clock/Frequency Generation Circuits and Systems**, Woogeun Rhee, Antonio Liscidini, Jae-Yoon Sim, Kenichi Okada, and Sudhakar Pamarti Volume 2012, Article ID 941653, 2 pages

#### 480 MHz 10-tap Clock Generator Using Edge-Combiner DLL for USB 2.0 Applications,

Takashi Kawamoto, Kazuhiro Ueda, and Takayuki Noto Volume 2012, Article ID 267247, 17 pages

Semidigital PLL Design for Low-Cost Low-Power Clock Generation, Ni Xu, Woogeun Rhee, and Zhihua Wang Volume 2011, Article ID 235843, 9 pages

**An Interpolated Flying-Adder-Based Frequency Synthesizer**, Pao-Lung Chen and Chun-Chien Tsai Volume 2011, Article ID 871385, 11 pages

**Open-Loop Wide-Bandwidth Phase Modulation Techniques**, Nitin Nidhi, Pin-En Su, and Sudhakar Pamarti Volume 2011, Article ID 507381, 12 pages

Receiver Jitter Tracking Characteristics in High-Speed Source Synchronous Links, Ahmed Ragab, Yang Liu, Kangmin Hu, Patrick Chiang, and Samuel Palermo Volume 2011, Article ID 982314, 15 pages

**VLSI Implementation of a Distributed Algorithm for Fault-Tolerant Clock Generation**, Gottfried Fuchs and Andreas Steininger

Volume 2011, Article ID 936712, 23 pages

Design Considerations for Autocalibrations of Wide-Band  $\triangle \Sigma$  Fractional-N PLL Synthesizers, Jaewook Shin and Hyunchol Shin Volume 2011, Article ID 139183, 9 pages

A Tunable Wideband Frequency Synthesizer Using LC-VCO and Mixer for Reconfigurable Radio Transceivers, Yusaku Ito, Kenichi Okada, and Kazuya Masu Volume 2011, Article ID 361910, 7 pages

**A Wide Lock-Range Referenceless CDR with Automatic Frequency Acquisition**, Seon-Kyoo Lee, Young-Sang Kim, Hong-June Park, and Jae-Yoon Sim Volume 2011, Article ID 701730, 7 pages

Hindawi Publishing Corporation Journal of Electrical and Computer Engineering Volume 2012, Article ID 941653, 2 pages doi:10.1155/2012/941653

#### **Editorial**

#### **Clock/Frequency Generation Circuits and Systems**

#### Woogeun Rhee,1 Antonio Liscidini,2 Jae-Yoon Sim,3 Kenichi Okada,4 and Sudhakar Pamarti5

- <sup>1</sup> Institute of Microelectronics, Tsinghua University, Beijing 100084, China

- <sup>2</sup> Department of Electronics, University of Pavia, 27100 Pavia, Italy

- <sup>3</sup> Department of Electrical Engineering, Pohang University of Science and Technology, Kyungbuk 790-784, Republic of Korea

- <sup>4</sup> Department of Physical Engineering, Tokyo Institute of Technology, Tokyo 152-8552, Japan

- <sup>5</sup> Electrical Engineering Department, University of California, Los Angeles, CA 90095, USA

Correspondence should be addressed to Woogeun Rhee, wrhee@tsinghua.edu.cn

Received 20 November 2011; Accepted 20 November 2011

Copyright © 2012 Woogeun Rhee et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Clock generation and frequency synthesis systems have played a critical role in modern communication system design. As data rate increases, low-noise and low-power clock/frequency generation is getting more important than ever for high-performance digital communication systems. Timing uncertainty directly affects the overall performance of microprocessors and I/O links. The quality of wireless transceiver systems is often determined by the phase noise performance of frequency synthesizers. Active researches in the areas of clocking, data synchronization, and frequency generation have been performed for broad applications. This special issue focuses on the new and existing clock/frequency generation circuits and systems for wireline and wireless system IC designs with a special emphasis given to advanced technical results.

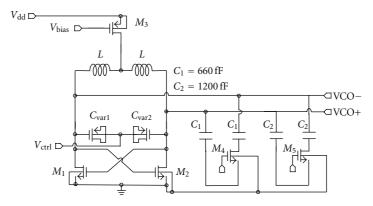

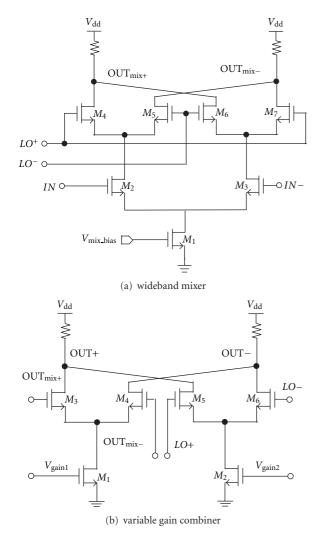

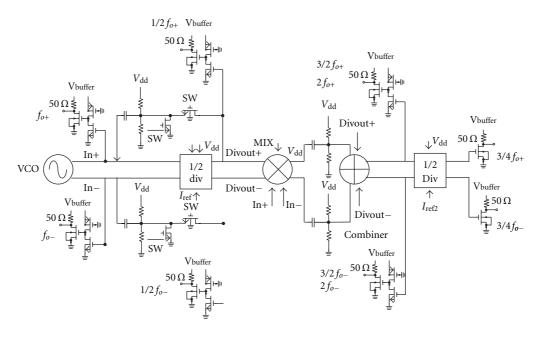

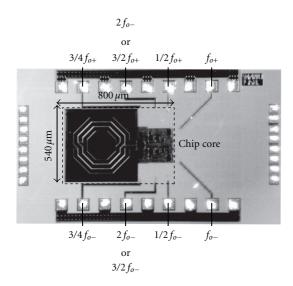

This special issue consists of nine papers. Four papers focus on wireline applications: a paper on characterizing the jitter tracking performance of the receiver for high-speed source synchronous links, a paper on generating fault-tolerant clock for VLSI circuits, a paper on a wide lock range clock-and-data recovery (CDR) circuit, and a paper on a delay-locked-loop- (DLL-) based clock generation for USB 2.0 applications. Three papers focus on wireless applications: a paper on open-loop phase modulation techniques for wide-bandwidth transmitter design, a paper on high-speed, high-resolution autocalibration techniques for fractional-N phase-locked loops (PLLs), and a paper on a wideband LC-based voltage-controlled oscillator (VCO) design for reconfigurable radio transceivers. Other two subsequent papers present nontraditional ways of generating clock frequency:

the one with an all-digital flying-adder-based method and the other with a semidigital PLL-based method.

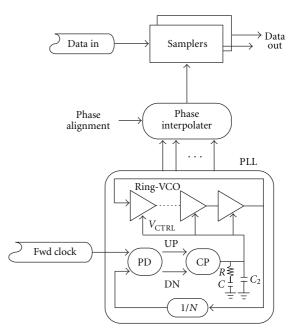

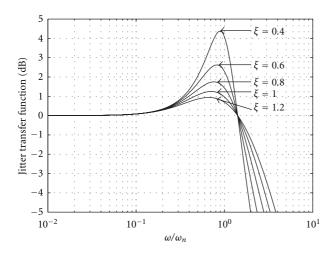

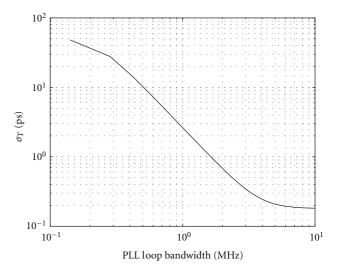

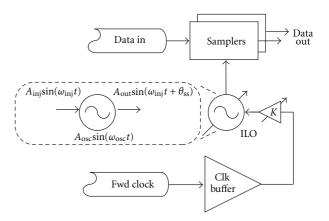

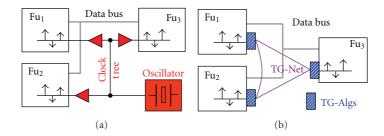

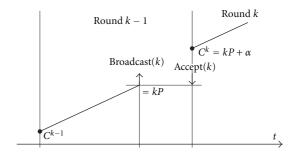

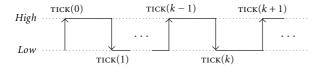

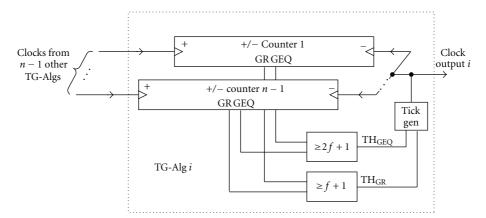

One of the major factors limiting the maximum achievable I/O data rates occurs from the degradation of system timing margins by clock jitter. The paper by A. Ragab et al. presents a comparative analysis of several jitter tracking architectures employed in source synchronous high-speed links. Tracking the transmit clock jitter in the presence of clock skew and channel loss enables high data rate operation in these links. The paper by G. Fuchs and A. Steininger describes a generation scheme of fault-tolerant clock based on a tick synchronization algorithm. An ASIC chip, implemented in a 0.18- $\mu$ m CMOS, demonstrates feasibility of this scheme creating a globally synchronized clock, which is tolerant to a configurable number of arbitrary faults.

For high-speed chip-to-chip communication, serial link protocol has been widely adopted in various computer-to-peripheral interfaces. The use of serial links for multipurpose, however, still presents some challenges which must be overcome by circuit design. The paper by S.-K. Lee et al. presents a 650-Mb/s to 8-Gb/s referenceless CDR with automatic frequency acquisition. By utilizing a novel DLL-based frequency acquisition, the dual-loop CDR shows outstanding performance in terms of lock range, power consumption, and area. The USB 2.0 is one of the most popular wireline standards, but requiring a very small area and low power consumption for portable applications. For low-cost low-power clock generation, a clock generator based on an edge-combiner DLL is presented in the paper by T. Kawamoto et al. The clock generator generates 480-MHz

10-tap output signals from a 12-MHz reference signal and consists of three DLLs to shrink the design area so that it is smaller than the PLL-based one.

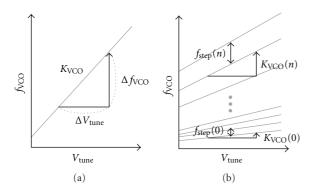

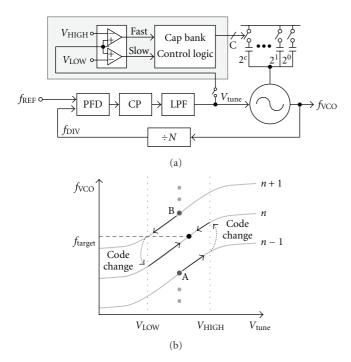

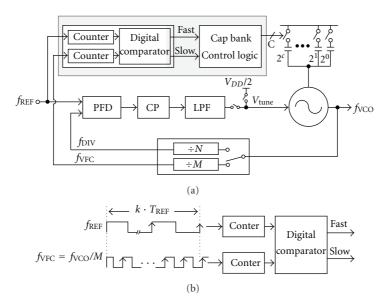

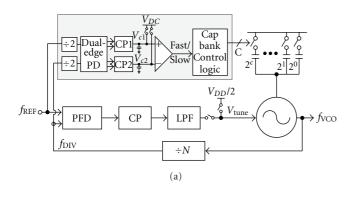

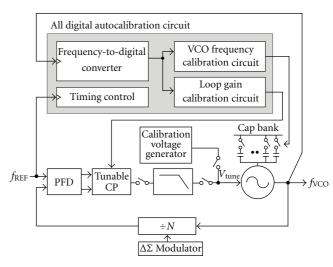

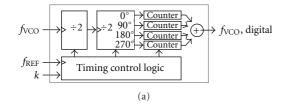

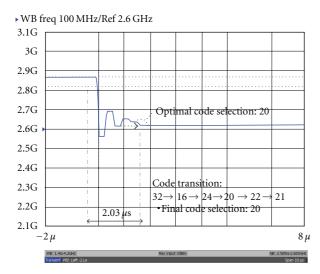

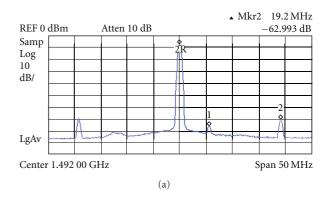

The rapid growth of new communication standards like LTE and WiMAX has led to high data rate, wide signal bandwidth and high peak-to-average power ratio. A wide-bandwidth phase modulator is one of the key building blocks for the design of next generation transceivers. The paper by N. Nidhi et al. presents open-loop phase modulation techniques for upcoming 60 GHz wireless communication and software-defined radio. The open-loop modulation technique achieves maximum flexibility with wide-bandwidth operation. In modern wireless transceiver systems, the  $\Delta\Sigma$  fractional-N frequency synthesizer is an essential building block. Especially for a wide tuning-range fractional-N frequency synthesizer, high-speed and highprecision automatic calibration is important for shortening the lock time and improving the phase noise. In the paper by J. Shin and H. Shin, an automatic calibration technique for the VCO frequency and the loop gain in the fractional-N PLL design is presented. A simple and efficient autocalibration method based on a high-speed frequency-todigital converter significantly reduces the calibration time.

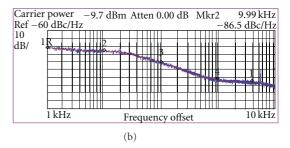

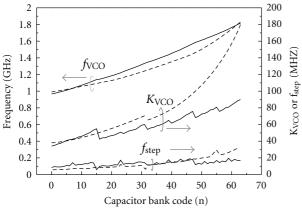

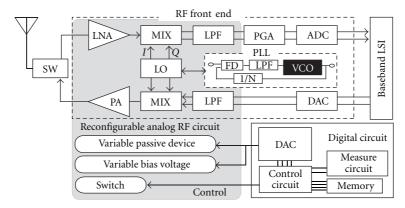

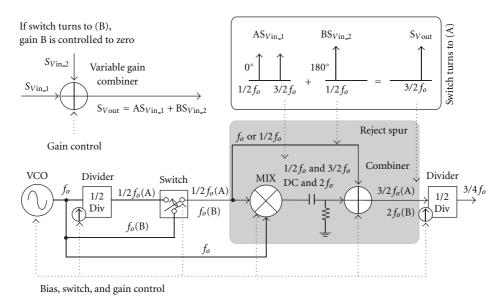

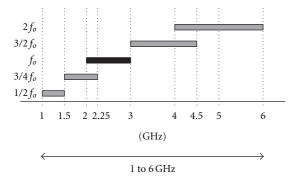

Recently, dozens of wireless communication standards have been used for small mobile terminals, for example, GSM, UMTS, LTE, WiMAX, WLAN, Bluetooth, UWB, GPS, DTV, and RFID, and the standards use several frequency bands spreading in a quite wide range such as 800 MHz to 6 GHz. All of these RF front-ends require a wideband-tunable VCO, which is an indispensable component for the multiband radio in common. The paper by Y. Ito et al. presents a wide-band frequency synthesizer with a frequency range from 1 GHz to 6.6 GHz by employing a wide-tuning LC VCO and a tuning-range extension circuit. Such tuning allows to satisfy the requirements of all cellular and WiFi standards, becoming a very interesting solution for multistandard transceiver where the presence of several local oscillator would results in a too expensive design.

The use of advanced CMOS technologies makes the traditional phase-locked loop (PLL) design challenging as on-chip variability and modeling inaccuracy become severe in deep submicron CMOS. Large loop parameter variation makes it difficult to find the optimum bandwidth for phase noise, spur, and settling time. In addition, analog passive devices become a bottleneck for scalability and integrating the loop filter (LPF) has been a challenging task in the conventional PLL design. Therefore, clock generation based on digital or semidigital method has received great attention recently. The paper by P.-L. Chen and C.-C. Tsai describes a flying-adder-based digital frequency synthesizer with an interpolated multiplexer to improve cycle-to-cycle and rms jitter performance. This synthesizer, fabricated in a 0.18μm CMOS, shows a frequency lock range of from 33 MHz to 286 MHz. The paper by N. Xu et al. introduces recent semidigital PLL architectures which relax technology dependency and provide low-cost low-power clock generation. With the absence of the time-to-digital converter (TDC), the semidigital PLL enables low-power linear phase detection

and does not necessarily require advanced CMOS technology while maintaining a technology scalability feature.

Lastly, the Guest Editors of this special issue would like to thank all the reviewers for their dedicated efforts in ensuring a high standard for the selected papers. We hope that readers will find this issue interesting.

> Woogeun Rhee Antonio Liscidini Jae-Yoon Sim Kenichi Okada Sudhakar Pamarti

Hindawi Publishing Corporation Journal of Electrical and Computer Engineering Volume 2012, Article ID 267247, 17 pages doi:10.1155/2012/267247

#### Research Article

### **480 MHz 10-tap Clock Generator Using Edge-Combiner DLL for USB 2.0 Applications**

#### Takashi Kawamoto, 1 Kazuhiro Ueda, 2 and Takayuki Noto 3

- <sup>1</sup> Hitachi Central Research Laboratory, 1-280, Higashi-Koigakubo Kokubunji-shi, Tokyo 185-8601, Japan

- <sup>2</sup> Technology Development Unit, Mixed Signal Core Development Division, Converter Development Department, Renesas Electronics Corporation, 4-1 Mizuhara, Itani-shi, Hyogo 664-0005, Tokyo, Japan

- <sup>3</sup> SoC Business Unit, 1st Industry & Network Business Division, Optical Disc Solutions Department, Renesas Electronics Corporation, 5-20-1 Josuihon-cho, Kodaira-shi, Tokyo 187-8588, Japan

Correspondence should be addressed to Takashi Kawamoto, takashi.kawamoto.hv@hitachi.com

Received 28 June 2011; Accepted 8 September 2011

Academic Editor: Woogeun Rhee

Copyright © 2012 Takashi Kawamoto et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

A clock generator with an edge-combiner DLL (ECDLL) has been developed for USB 2.0 applications. The clock generator generates 480 MHz 10-tap output signals from a 12 MHz reference signal and consists of three DLLs to shrink the design area so that it is smaller than a conventional one based on a PLL. Each DLL is applied to our proposed shot pulse reset technique to prevent from a harmonic lock and is applied to a voltage-controlled delay line (VCDL) with a trimming function to operate against any process voltage temperature (PVT) variations. A 90 nm CMOS process was used to fabricate our proposed clock generator. The 480 MHz 10-tap output signals satisfy the USB 2.0 specifications. A power consumption is less than 1.3 mW and a locking time is less than  $3.5\,\mu$ s, which are far less than a conventional one,  $10.0\,\mu$ s. The design area is  $200\times225\,\mu$ m, which is half that of the conventional one.

#### 1. Introduction

The clock generator may be one of the largest blocks of the physical layer (PHY) in wireline communications, because it usually consists of a phase-locked loop (PLL) that has large capacitors for use as a lowpass filter. There are many reports proposing the shrinkage of the design area of PLLs. A capacitance-multiplication technique was reported to shrink the capacitance of the loop filter [1, 2]. However, the shrink ratio of a capacitor may be less than five when taking the leakage current of the capacitor and PVT variation into consideration. Thus, the total design area cannot be drastically reduced. An all digital PLL (ADPLL) technique has also been reported [3]. However, an issue with the accuracy operation against the PVT variation still remains. Therefore, a new approach is desirable for essentially reducing the design area.

The DLL has several advantages over the PLL. First, it can be designed to be smaller than the PLL. While the PLL is a higher-order system, the DLL is a first-order system and is always stable. Thus, the DLL needs small capacitors to keep the DLL loop stable while the PLL needs large capacitors to design a stable lowpass filter. Second, the DLL can achieve a shorter locking time than the PLL. Third, the DLL consumes less power than the PLL. The PLL has the VCO and a divider that consumes a large amount of power in order to reduce the jitter. However, the DLL has several disadvantages over the PLL when used as the clock generator. First, the DLL cannot generate faster clock signals than the PLL. Second, the DLL has a locking range limitation while the PLL does not. This means that the DLL cannot achieve a fractional multiplication ratio while the PLL can achieve a fractional N PLL.

An edge-combiner DLL (ECDLL) has been reported as an alternate high-speed clock generator because the ECDLL is based on the DLL and can multiply the reference frequency [4–8]. The ECDLL has a potential for use as the clock generator although it has barely been used in this capacity because the ECDLL has several challenges that need to be

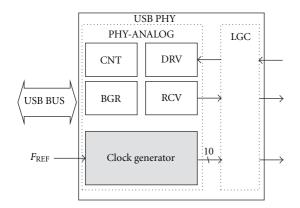

FIGURE 1: Block diagram of USB 2.0 PHY.

FIGURE 2: Conventional clock generator based on PLL.

overcome. The first is an operation against PVT variation. The second is the output signal frequency limitation.

From the viewpoint of the frequency limitation, the operation frequency of the DLL has been increasing in recent CMOS process. The DLL can operate at less than 1 GHz in a submicron CMOS process. Thus, the DLL might be able to be use as the clock generator for wireline communications whose operation frequency is less than about 1 GHz. USB 2.0 is the most popular wireline communication in the world and operates at 480 MHz. USB 2.0 PHY needs a small design area and a low power consumption level for use in portable devices. Therefore, USB 2.0 may be one of the most suitable applications for the clock generator with the ECDLL.

In order to apply the ECDLL for USB 2.0, we propose techniques hat overcome the above-mentioned challenges. The first is a shot pulse generator to prevent from a harmonic lock. The third is the VCDL trimming function to operate against PVT variation.

In this paper, we propose a clock generator applied to an ECDLL for USB 2.0 PHY to shrink the design area [1]. The organization of this paper is as follows. Section 2 describes the overall structure of the proposed clock generator architecture. Section 3 describes the ECDLL and DLL in detail. Section 4 presents the evaluation results of our measurements, and Section 5 concludes with a short summary of the key points.

#### 2. Overall Clock Generator Architecture

Figure 1 shows a block diagram of a USB 2.0 PHY. The PHY consists of a clock generator, a band-gap reference (BGR), a controller (CNT), a driver (DRV), a receiver (RCV), and

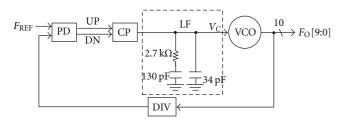

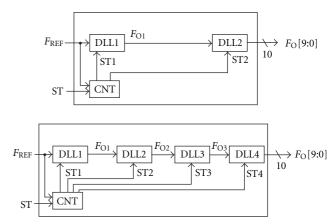

FIGURE 3: Block diagrams of candidate clock generator based on DLLs. Upper block diagram is the structure that consists of one ECDLL and one DLL. The ECDLL has a multiplication ratio of 40. Bottom block diagram is the structure that consists of three ECDLL and one DLL. The DLL1, DLL2, and DLL3 have multiplication ration of two, four, and five, respectively.

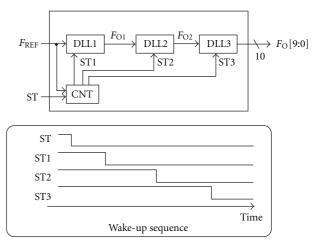

FIGURE 4: Proposed clock generator consisting of three DLLs and wake-up sequence. The DLL1 and DLL2 have multiplication ration of two and eight, respectively.

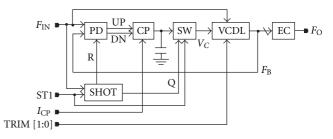

FIGURE 5: Block diagram of DLL1 and DLL2. In DLL1,  $F_{\rm IN}$  and  $F_{\rm O}$  are 12 MHz and 60 MHz, respectively. The VCDL generates 10-tap 12 MHz output signals. The capacitor is 10 pF. In DLL2,  $F_{\rm IN}$  and  $F_{\rm O}$  are 60 MHz and 480 MHz, respectively. The VCDL generates 16-tap 60 MHz output signals. The capacitor is 0.5 pF.

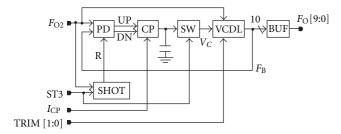

FIGURE 6: Block diagram of DLL.  $F_{O2}$  and  $F_{O}$  [9:0] are 480 MHz and 10-tap 480 MHz, respectively. The capacitor is 1 pF.

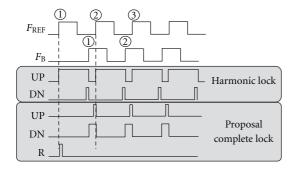

FIGURE 7: Explanation of harmonic lock and proposed shot pulse reset operation.

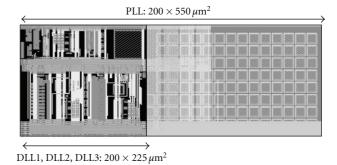

a logic block (LGC). Figure 2 shows a block diagram of a conventional clock generator based on the PLL with a ring oscillator. The reference signal ( $F_{\rm REF}$ ) is 12 MHz. The output signals ( $F_{\rm O}$ [9:0]) are 10-tap 480 MHz. The design area is 200  $\times$  550  $\mu{\rm m}^2$ . The loop bandwidth is designed at 1.6 MHz using a second-order lowpass filter that consists of 130 pF and 34 pF capacitances and a 2.7 k $\Omega$  resistance. Thus, the lowpass filter occupies a large portion of the design area. Therefore, we proposed the ECDLL as a clock generator to shrink the design area.

In this clock generator, there are three candidates, which are one ECDLL and one DLL, two ECDLL and one DLL, and three ECDLL and one DLL, as shown in Figures 3 and 4. The one ECDLL and one DLL structure consists of the DLL1 of the ECDLL that has the multiplication ratio of 40 and the DLL2 of the DLL that generates the 10-tap 480 MHz signals, as shown in Figure 3. The two ECDLL and one DLL structure consists of the DLL1 of the ECDLL that has the multiplication ratio of five, the DLL2 of the ECDLL that has the multiplication ration of eight, and the DLL3 of the DLL that has the same manner of the above DLL, as shown in Figure 4. The three ECDLL and one DLL structure consists of the DLL1 of the ECDLL that has the multiplication ratio of two, the DLL2 of the ECDLL that has the multiplication ratio of four, the DLL3 of the ECDLL that has the multiplication ratio of five, and the DLL4 of the DLL that has the same manner of the above DLL, as shown in Figure 3.

First, it is reasonable that the ECDLL has the multiplication ratio of less than 10, according to the design area and operation against from PVT variation. As the multiplication ratio is larger, the number of the VCDL stage is larger. It

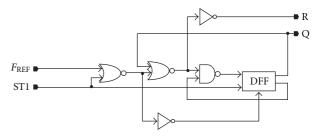

FIGURE 8: Block diagram of shot pulse generator.

causes large design area. The one ECDLL and one DLL structure becomes two times as large as the two ECDLL and one DLL structure because the ECDLL of the multiplication ratio of 40 is large. The two ECDLL and one DLL structure is almost same design area as the three ECDLL and one DLL structure. And then, the previous DLL operates more slowly than the latter one. Thus, the delay cell size in the previous DLL may be smaller than that in the latter one. Therefore, to shrink the design area, the previous DLL might have smaller multiplication ratio than the latter one.

Second, the number of the cascade DLL block should be as low as possible because the operation of the whole clock generator could be stable and the settling period could be short. In our proposed clock generator, the standby sequence is necessary because the DLL may fall into the unlock state if the DLL starts to operate before the previous DLL completes the lock, as shown in Figure 4.

Finally, the two ECDLL and one DLL structure is proposed, considering above concern. The DLL1 and DLL2 have a multiplication ratio of five and eight, respectively.

The counter (CNT) generates the standby signals of each block (ST1, ST2, and ST3) using the standby signal of the clock generator (ST) to create a standby sequence for each DLL, as shown in Figure 4. If DLL2 starts the lock operation before DLL1 completes the lock, DLL2 might fall into the unlock state. Thus, the CNT controls the sequential wake-up operation by generating ST1, ST2, and ST3, as shown in Figure 4.

#### 3. ECDLL and DLL in Detail

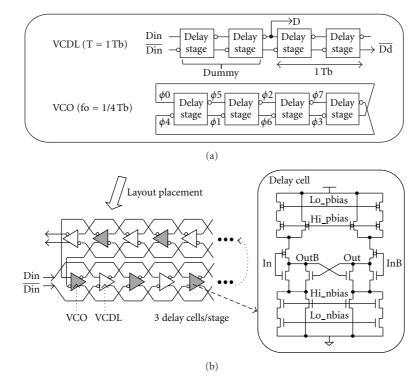

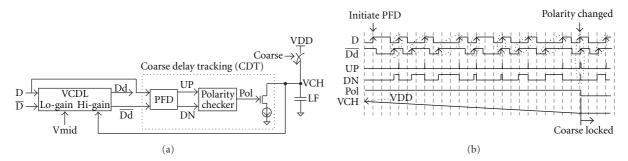

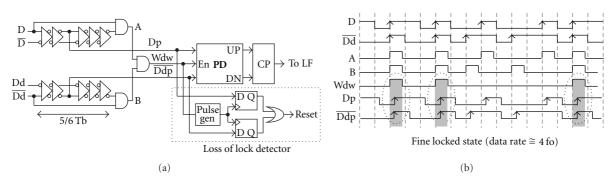

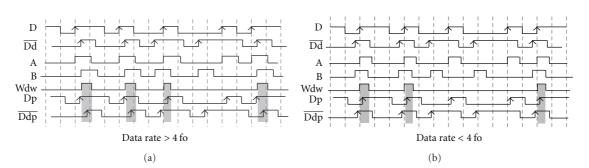

3.1. Shot Pulse Reset Technique. Figures 5 and 6 show a block diagram of our proposed ECDLL applied to DLL1 and DLL2 and DLL applied to DLL3. They consist of a phase detector (PD), a charge-pump (CP), a switch (SW), a capacitor, a voltage-controlled delay line (VCDL), and shot pulse generator (SHOT). And then the ECDLL has an edge-combiner (EC) and the DLL has the output buffer (BUF). The PD makes a comparison between the phase of the  $F_{\rm REF}$  and a phase of the feedback clock ( $F_{\rm B}$ ) and generates result signals (UP/DN). The CP charges and discharges the capacitor. The VCDL generates the output signals from the  $F_{\rm REF}$ . The delay time from  $F_{\rm REF}$  to  $F_{\rm B}$  is controlled by a controlled voltage ( $V_{\rm C}$ ). In Figure 6, the EC generates the output signal ( $F_{\rm O1}$ ) from VCDL output signals.

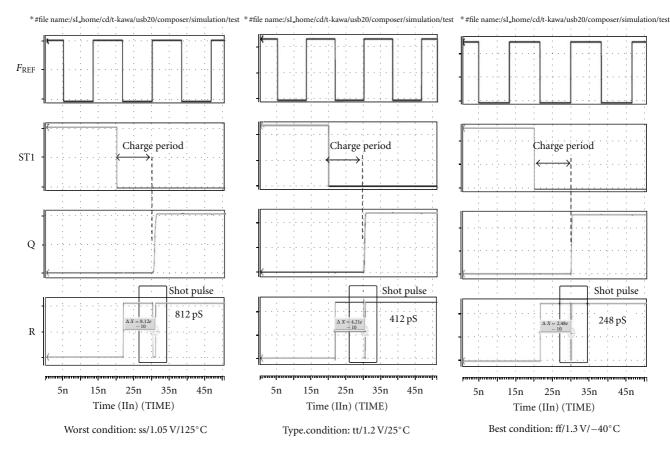

FIGURE 9: Simulation results from shot pulse generator.

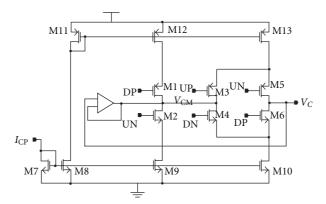

FIGURE 10: Circuit diagram of the CP.

Our ECDLL and DLL have an issue of a harmonic lock. We propose shot pulse reset technique by using the shot pulse generator to resolve this issue.

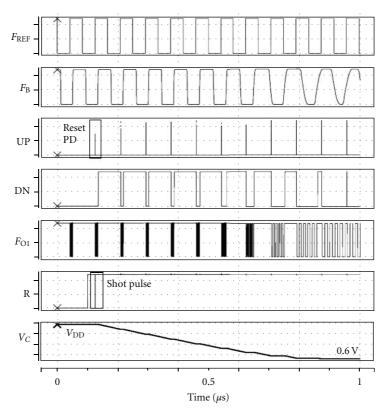

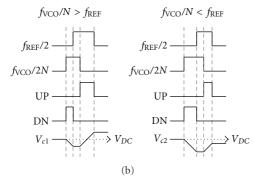

Figure 7 shows an explanation of the proposed shot pulse reset technique. The PD compares the rise edge of the  $F_{\rm REF}$  and the rise edge of the  $F_{\rm B}$  and generates the UP and DN signals. When the second rise edge of the  $F_{\rm REF}$  comes after the first rise edge of the  $F_{\rm B}$ , a harmonic lock occurs that the PD compares between first rise edge of the  $F_{\rm REF}$  and the first rise edge of the  $F_{\rm B}$ . It is an actual operation that the PD compares between the second rise edge of the  $F_{\rm REF}$  and the first rise edge

of the  $F_B$ . A shot pulse reset shown in Figure 7 is proposed to prevent this malfunction from happening. The operation of the PD is reset by R when the PD compares the first rise edge of the  $F_{REF}$  with the first rise edge of the  $F_{REF}$  with the first rise edge of the  $F_{REF}$  with the first rise edge of the  $F_B$ . Even though the PD is reset by R, the harmonic lock occurred and the PD compared the third rise edge of the  $F_{REF}$  with the first rise edge of the  $F_B$ , when the first rise edge of the  $F_B$  comes after the third rise edge of the  $F_{REF}$ . To prevent this malfunction from happening, the capacitor is charged by the SW and the voltage level of the

FIGURE 11: Simulation results from CP.

$\label{eq:figure 12:Block diagram of VCDL in DLL1 and DLL3.}$

FIGURE 13: Circuit diagram of VIC.

FIGURE 14: Circuit diagram of delay cell.

FIGURE 15: Explanation of the VCDL and DLL operation. (a) The explanation of the VCDL delay-current characteristics. The type-A VCDL has the smooth sensitivity and the type-B has the steep sensitivity. (b) The explanation of the influence of the VCDL delay-current characteristics due to the PVT variation. (c) The explanation of the DLL settling operation by using type-A VCDL. The settling operation is smooth because the sensitivity of the VCDL is not steep. (d) The explanation of the DLL settling operation by using type-B VCDL. The settling operation is not smooth because the sensitivity of the VCDL is steep.

FIGURE 16: Postlayout simulation results of VCDL delay-current characteristics by using variable delay cell.

FIGURE 17: Postlayout simulation results of VCDL delay-current characteristics for DLL1.

$V_{\rm C}$  is likely to be  $V_{\rm DD}$ . This allows the first rise edge of the  $F_{\rm B}$  to come before the second rise edge of the  $F_{\rm REF}$  when the PD starts operation.

Figures 8 and 9 show a circuit diagram of the shot pulse generator (SHOT) and the simulation results from the SHOT. After the ST1 is set to low, the R operates the pulse reset and the Q is set to high at the rise edge of the  $F_{\rm REF}$ . The pulse of the R resets the PD operation and the SW charges the capacitor during the period between the fall edge of the ST1 and the rise edge of the Q. After charging the capacitor, the  $V_{\rm C}$  is almost the  $V_{\rm DD}$ . Our ECDLL and DLL can be operated accurately because of the SHOT.

FIGURE 18: Postlayout simulation results of VCDL delay-current characteristics for DLL2.

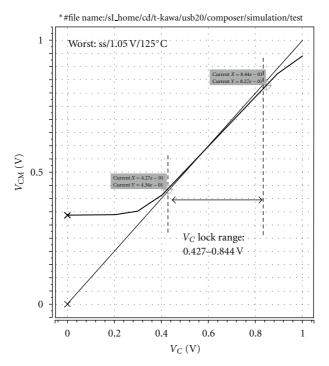

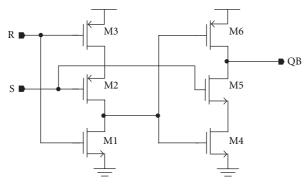

3.2. Charge Pump. Figure 10 shows a circuit diagram of the CP. M5 and M6 are the switches that charge and discharge the capacitor. When the CP charges the current, the UP, UN, DP, and UN are high, low, low, and high, respectively. The charge current, which is the M13 drain current, passes through the switch M5 and charges the capacitor that is connected at the  $V_{\rm C}$ , and the M12 drain current passes through the switches (the M1 and M4) and flows to M10. When the CP discharges the current, the UP, UN, DP, and UN are low, high, high, and low, respectively. The discharge current, which is the M10 drain current, passes through the switch at M6 and discharges the capacitor that is connected at the  $V_{\rm C}$ , and the M13 drain current passes through the switches (the M3 and M2) and flows to M9. The Op-Amp is designed in the CP to structure the common-mode feedback. When the  $V_C$  is not equal to the voltage of the  $V_{\rm CM}$ , the difference between the charge current and the discharge current is larger. This causes a constant phase error. Figure 11 shows the simulation results from the CP. The lock range, which is the range in which the  $V_{\rm C}$  is equal to the voltage of the  $V_{\rm CM}$ , is 0.427–0.884 V under the worst conditions (ss/1.05 V/125°C).

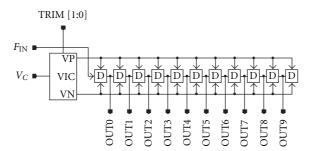

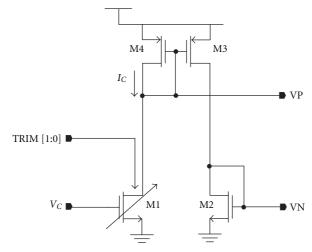

3.3. VCDL. Figure 12 shows a block diagram of the voltage-controlled delay line (VCDL) for DLL1 and DLL3. It consists of a voltage-current converter (VIC) and the delay chain consisting of eleven delay cells. The VCDL for DLL2 has the seventeen delay cells. Figures 13 and 14 show the circuit diagrams of the VIC and the delay cell. The VIC converts the control voltage ( $V_{\rm C}$ ) to a control current ( $I_{\rm C}$ ). The VCDL delays the  $F_{\rm IN}$ , which is the amount of the delay controlled by the  $I_{\rm C}$ . The trimming signal (TRIM[1:0]) controls the sensitivity of the current-voltage characteristics of the M1 by

FIGURE 19: Postlayout simulation results of VCDL delay-current characteristics for DLL2.

Figure 20: Block diagram of EC for DLL1.

Figure 21: Circuit diagram of SRFF.

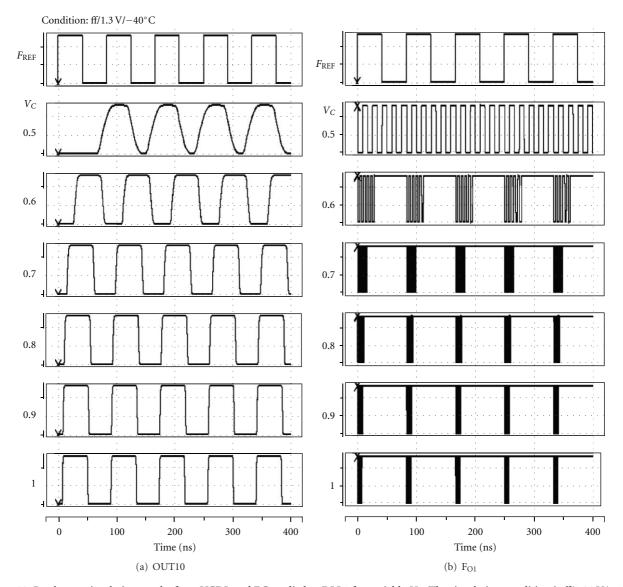

FIGURE 22: Postlayout simulation results from VCDL and EC applied to DLL1 for variable  $V_{\rm C}$ . The simulation condition is ff/1.30 V/ $-40^{\circ}$ C.

changing the gm of M1. The larger the TRIM[1:0] is, the larger the  $I_C$  is. The delay cell consists of the two inverter buffers (M4-M2 and M5-M6) and current sources (M6 and M1).

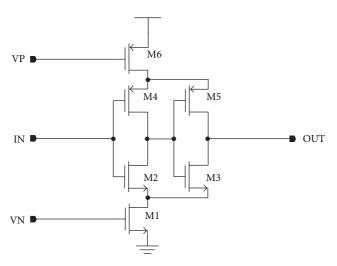

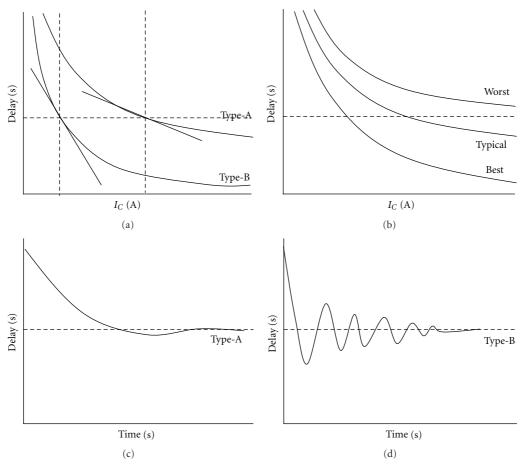

In the VCDL, the sensitivity of the VCDL is important for DLL operation. Figure 15 shows the explanation of the sensitivity of the VCDL and the DLL settling operation. If the sensitivity of the VCDL delay-current characteristics is larger at the lock point, the DLL settling operation may not be stable as shown in Figure 15(d). It is the reason that the overshoot is large because the magnitude of the delay change per one clock cycle is large. To prevent from this unstable state, the VCDL sensitivity is designed small by using large delay cell for VCDL, as shown in Figure 15(a). However, this design causes large power consumption and the malfunction may be caused in the worst condition if the sensitivity is designed too small, as shown in Figure 15(b).

The delay is mainly generated as the control current and input capacitor, which is gate capacitor of M4 and M2, and a parasitic capacitor between delay cells. If the buffer MOSs (M4-M2 and M5-M3) are designed small, the necessary delay is obtained by small current. However, this causes large sensitivity. Thus, the buffer MOSs are not designed small. Figure 16 shows the VCDL delay-current characteristics by using variable delay cell. As the size of the delay cell is larger, the sensitivity at the necessary delay point is smoother.

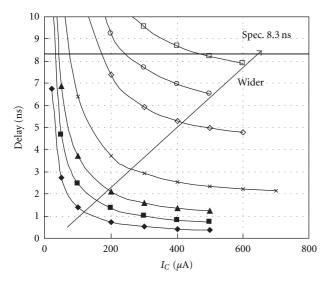

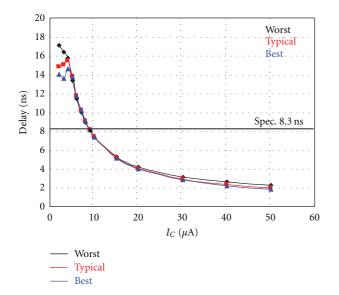

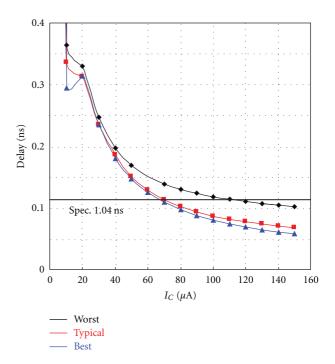

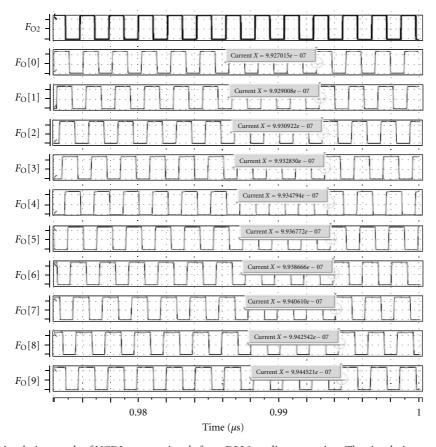

Figures 17, 18, and 19 show the postlayout simulation results of the VCDL delay-current characteristics for DLL1, DLL2, and DLL3, respectively. The VCDL for DLL1 can achieve a target delay of 8.3 ns at about 9  $\mu$ A under variable conditions. The VCDL for DLL2 can achieve a target delay of 1.04 ns at 80  $\mu$ A under typical and the best conditions, which are tt/1.20 V/25°C and ff/1.35 V/-40°C, respectively. However, under the worst condition, which is ss/1.05 V/125°C,

Figure 23: Postlayout simulation results from VCDL and EC applied to DLL1 for variable condition at  $V_{\rm C}=0.5\,{\rm V}$ .

Figure 24: Postlayout simulation results from VCDL and EC applied to DLL2 for variable  $V_{\rm C}$ .

Figure 25: Postlayout simulation results from DLL1 locking operation. The simulation condition is  $tt/1.2\,V/25^{\circ}C$ .

FIGURE 26: Postlayout simulation result of VCDL output signals from DLL1 settling operation. The simulation condition is tt/1.2 V/25°C.

FIGURE 27: Postlayout simulation results from DLL2 locking operation. The simulation condition is tt/1.2 V/25°C.

FIGURE~28:~Postlayout~simulation~result~of~VCDL~output~signals~from~DLL2~settling~operation.~The~simulation~condition~is~tt/1.2~V/25~C.

FIGURE 29: Postlayout simulation results from DLL3 locking operation. The simulation condition is tt/1.2 V/25°C.

the target delay can be achieved at an  $I_{\rm C}$  of about 120  $\mu$ A. This is adjusted by the trimming bits (TRIM[1:0]), as shown in Figure 14. The VCDL for DLL3 can achieve a target delay of 0.208 ns at a  $V_{\rm C}$  of about 200  $\mu$ A. However, the VCDL is trimmed by the TRIM[1:0].

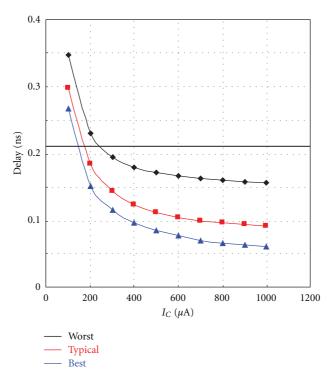

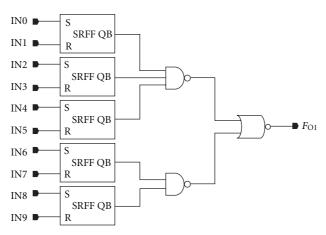

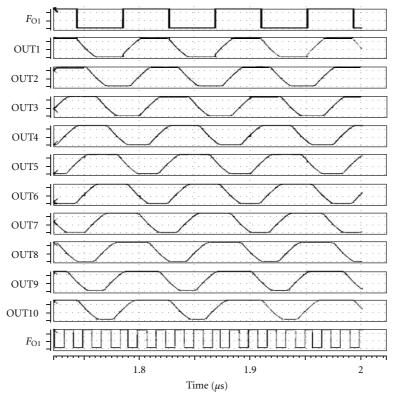

3.4. Edge-Combiner. Figure 20 shows a block diagram of the EC for DLL1. It consists of SR flip-flops (SRFFs) and NANDs and a NOR. Figure 21 shows a circuit diagram of the SRFF. It consists of six MOSs. There are two floating nodes (M3 drain node and M5 source node). Figures 22 and 23 show the postlayout simulation results from the VCDL and EC for DLL1. The one cycle delay is obtained at about  $V_{\rm C}=0.5\,{\rm V}$  in ff/1.30 V/ $-40^{\circ}{\rm C}$  as shown in Figure 22(a). The EC can operate variable input signal as shown in Figure 22(b). If the SRFF cannot operate accurately by the leakage current, the output signal of the EC slips the clock in part. However, the EC can get all clock edges of the each signal at variable  $V_{\rm C}$  as shown in Figure 22(b) and it can operate at variable conditions as shown in Figure 23.

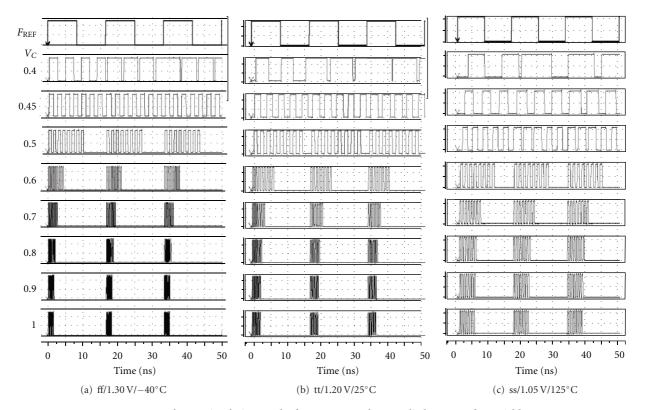

Figure 24 shows the postlayout simulation results from the VCDL and EC for DLL2. The one cycle delay is obtained at between 0.45 V and 0.50 V in ff/1.30 V/ $-40^{\circ}$ C and tt/1.20 V/25°C as shown in Figures 23(a) and 23(b), and at between 0.50 V and 0.60 V in ss/1.05 V/125°C. The EC can get all clock edges of the each signal at variable  $V_{\rm C}$  and it can operate at variable conditions as shown in Figure 24.

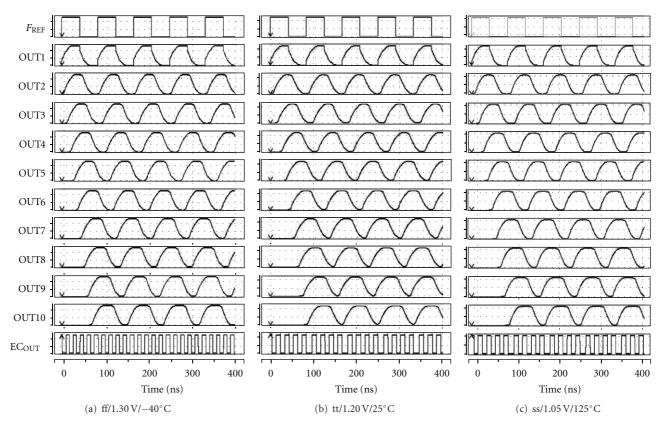

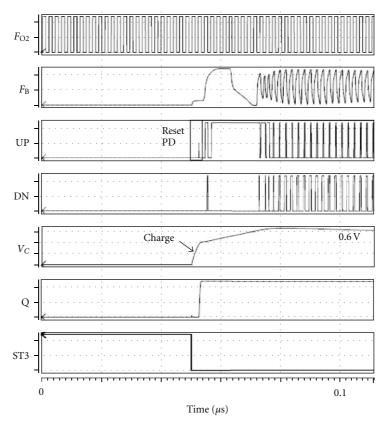

3.5. Lock Operation. Figure 25 shows the postlayout simulation results of the DLL1 locking operation. The simulation condition is tt/1.2 V/25°C. The DLL1 has a capacitor of 10 pF. After ST1 is set to low at about 100 ns, the R is set to high, and then a shot pulse occurs. The PD operation is reset by the shot pulse, as shown by the UP and DN signals in Figure 25. After that, the PD generates a wide DN pulse and then the  $V_{\rm C}$  decreases. Finally, DLL1 completes the lock at about 1  $\mu$ s. When DLL1 completes the lock, the  $V_{\rm C}$  is about 0.6 V. Figure 26 shows the VCDL output signals after the DLL1 completes the lock. The EC can generate the output signal ( $F_{\rm O1}$ ) of 60 MHz.

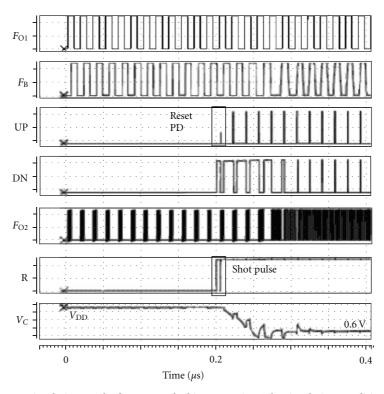

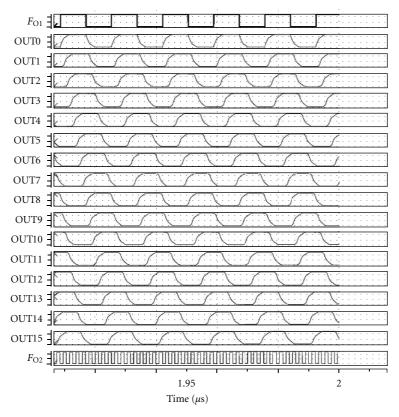

Figure 27 shows the postlayout simulation result of the DLL2 locking operation. The simulation condition is  $tt/1.2 \text{ V}/25^{\circ}\text{C}$ . The DLL2 has a capacitor of 0.5 pF. After ST2 is set to low at about 200 ns, the R is set to high and then a shot pulse occurs. The PD operation is reset by the shot pulse, as shown by the UP and DN signals in Figure 27. After that, the PD generates a wide DN pulse and then the  $V_C$  decreases. Finally, DLL2 completes the lock at about 400 ns. When DLL2 completes the lock, the  $V_C$  is about 0.6 V. Figure 28 shows the VCDL output signals after the DLL2 completes the lock. The EC can generate the output signal ( $F_{O2}$ ) of 480 MHz.

Figure 29 shows the postlayout simulation results of the DLL3 locking operation. The simulation condition is tt/1.2 V/25°C. The DLL2 has a capacitor of 1 pF. After ST3 is set to low at about 50 ns, the PD operation is reset by

FIGURE 30: Postlayout simulation result of VCDL output signals from DLL3 settling operation. The simulation condition is tt/1.2 V/25°C.

the R shot pulse, as shown by the UP and DN signals in Figure 28. After that, the PD generates a wide UP pulse and then the  $V_{\rm C}$  increases. Finally, DLL3 completes the lock at about 100 ns. When DLL3 completes the lock, the  $V_{\rm C}$  is about 0.6 V. Figure 30 shows the VCDL output signals after the DLL3 completes the lock. The DLL3 can generate the output signals of 480 MHz.

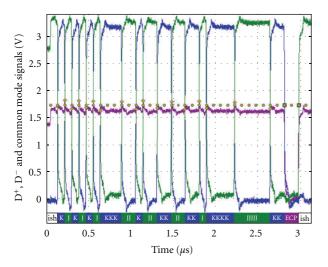

Figure 31 shows the postlayout simulation results from a clock generator that consists of DLL1, DLL2, and DLL3. After ST is set to low, ST1 is set to low first. At this time, ST2 and ST3 remain high.  $F_{REF}$  inserts DLL1 and the  $V_{C}$  is nearly  $V_{\rm DD}$  due to a precharge. The PD generates a wide DN pulse at first because of the precharge. The  $V_{\rm C}$  decreases due to the wide DN pulse. At about 2  $\mu$ s, DLL1 completes the lock and generates  $F_{O1}$ , which is the 60 MHz clock signal. ST2 is set to low at about 1  $\mu$ s. It is essentially set to low after DLL1 completes the lock. However, in this simulation, it is set to low before the DLL lock time. The  $V_C$  in DLL2 is almost  $V_{\rm DD}$  due to the precharge. After ST2 is set to low, the PD in DLL2 generates a wide DN pulse and then the  $V_C$  is soon almost 0.5 V. At about 2 µs, DLL2 completes the lock. ST3 is set to low at about  $2 \mu s$ . It is essentially set to low after DLL2 completes the lock, but in this simulation, it is set to low before the DLL lock time, too. After ST3 is set to low, the  $V_{\rm C}$  at first remains almost  $V_{\rm DD}$ . The  $V_{\rm C}$  decreases at about  $2.6 \,\mu s$  and finally is about  $0.5 \,V$ . DLL3 completes the lock and generates the 10-tap 480 MHz clock signals. The total lock time of the clock generator is about  $3.0\,\mu s$ . In general, the locking time of the DLL is defined by the capacitance and CP current. When the CP current is large for the capacitance, the locking time is short, but the locking operation is barely stable. DLL1 is designed to be stable because the phase error of DLL1 directly influences the other DLLs. DLL2 and DLL3 are designed to achieve a fast locking time because the clock generator can achieve it. Then, DLL2 and DLL3 start to operate before the forward DLL completes the fast locking time. When DLL2 starts to operate,  $F_{\rm O1}$  is almost 60 MHz. Thus, DLL2 can accurately operate.

#### 4. Measurement Results

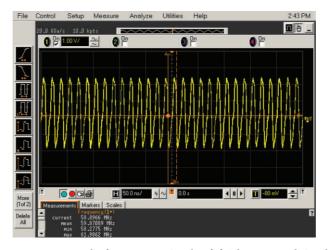

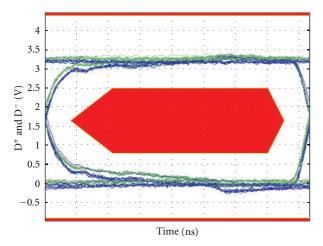

A 90 nm CMOS process was used to fabricate our proposed clock generator for use as a USB 2.0 PHY. Figure 32 shows the measurement results of the output signal  $F_0[9]$ . The measurement signal is  $F_0[9]$  divided by eight. The clock generator output signal frequency is 480 MHz. The jitter is less than 0.8 psrms. Figure 33 shows the measurement results of the EYE pattern for the USB 2.0 specifications. The USB 2.0 PHY with our proposed clock generator can pass these specifications. Figure 34 shows the measurement results of the random data pattern in the USB 2.0 specifications. The USB 2.0 PHY with our proposed clock generator can operate random data that meets the USB 2.0 specifications. Figure 35 shows the layout of the chip. Our proposed clock

Figure 31: Postlayout simulation results from clock generator wake-up operation. The simulation condition is  $tt/1.2\,V/25^{\circ}C$ .

Figure 32: Measurement results from output signal  $F_{\rm O}[9]$ . The measured signal is  $F_{\rm O}[9]/8$ .

Table 1: Comparison table.

| Item          | Unit              | Proposed clock generator | Conventional PLL in Figure 2 |

|---------------|-------------------|--------------------------|------------------------------|

| Structure     | _                 | 2 ECDLL + 1 DLL          | 1 PLL                        |

| Frequency     | MHz               | 480                      | 480                          |

| Locking-time  | μs                | 3.5                      | 10.0                         |

| Output jitter | ps                | 0.8                      | 2.0                          |

| Technology    | nm                | 90                       | 90                           |

| Power         | mW                | 1.3                      | 3.8                          |

| Area          | $\mu\mathrm{m}^2$ | $200 \times 225$         | $200 \times 500$             |

FIGURE 33: Measurement results from EYE pattern of fabricated PHY. The results meet the USB 2.0 specifications.

FIGURE 34: Measurement results from random data pattern of USB 2.0 specifications.

generator consists of three DLLs that is half the design area as that of the conventional one that consists of the PLL. Our clock generator consists of three DLLs. However, each DLL has a small capacitor to maintain the loop stability. Thus, our clock generator is smaller than the conventional one that has a large capacitor in the loop filter. Table 1 is a comparison table. The proposed clock generator has a power consumption of 1.3 mW, which is less than that of the conventional one, which is based on the PLL as shown in Figure 2. The ECDLL operates at the necessary reference signal frequency in the DLL loop that includes the VCDL. Thus, the power consumption is less than that of a PLL that has a VCO and a divider. A locking time of less than  $3.5\,\mu s$  can also be achieved.

#### 5. Conclusion

We proposed novel clock generator architecture to shrink the design area. The proposed clock generator consists of

Figure 35: Chip layout. Our fabricated DLL occupies  $200 \times 225 \,\mu\text{m}$ .

two edge-combiner DLLs and a DLL. A shot pulse generator is used in the DLLs to prevent from harmonic lock and a CP with common-mode feedback is used in the DLLs to reduce the pattern jitter due to a constant phase error. A controller is used to control the wake-up sequence to prevent malfunctions. Our proposed clock generator is fabricated using a 90 nm CMOS process. It can achieve 10-tap 480 MHz clock signals that meet the USB 2.0 specifications. A power consumption of less than 1.3 mA was also achieved. Our USB 2.0 PHY with this clock generator also meets the USB 2.0 specifications. Our proposed clock generator needs only half the design area of the conventional one, which is based on the PLL.

#### References

- [1] Y. Moon, G. Ahn, H. Choi, N. Kim, and D. Shim, "A quad 6 Gb/s multi-rate CMOS transceiver with TX rise/fall-time control," in *Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC '06)*, pp. 79–84, February 2006.

- [2] T. Kawamoto, T. Takahashi, S. Suzuki, T. Noto, and K. Asahina, "Low-jitter fractional spread-spectrum clock generator using fast-settling dual charge-pump technique for serial-ATA application," in *Proceedings of the 35th European Solid-State Circuits Conference (ESSCIRC '09)*, pp. 380–383, September 2009.

- [3] W. Grollitsch, R. Nonis, and N. Da Dalt, "A 1.4psrms-period-jitter TDC-less fractional-N digital PLL with digitally controlled ring oscillator in 65 nm CMOS," in *Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC '10)*, pp. 478–479, February 2010.

- [4] "USB 2.0 transceiver macrocell interface (UTMI) specification version 1.05 3/29/2001," 2001, http://developer.intel.com/technology/usb/download/2\_0\_Xcvr\_Macrocell\_1\_05.pdf.

- [5] G. Chien and P. R. Gray, "A 900 MHz local oscillator using a DLL-based frequency multiplier technique for PCS applications," in *Proceedings of the IEEE International Solid-State Cir*cuits Conference 47th Annual ISSCC, pp. 202–203, February 2000.

- [6] K. H. Cheng, S. M. Chang, Y. L. Lo, and S. Y. Jiang, "A 2.2 GHz programmable DLL-based frequency multiplier for SOC applications," in *Proceedings of the IEEE Asia-Pacific Conference on Advanced System Integrated Circuits*, pp. 72–75, August 2004.

- [7] H. Y. Huang and J. H. Shen, "A DLL-based programmable clock generator using threshold-trigger delay element and circular edge combiner," in *Proceedings of the IEEE Asia-Pacific*

- Conference on Advanced System Integrated Circuits, pp. 76–79, August 2004.

- [8] K. H. Cheng, S. M. Chang, S. Y. Jiang, and W. B. Yang, "A 2 GHz fully differential DLL-based frequency multiplier for high speed serial link circuit," in *Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS '05)*, vol. 2, pp. 1174–1177, May 2005.

Hindawi Publishing Corporation Journal of Electrical and Computer Engineering Volume 2011, Article ID 235843, 9 pages doi:10.1155/2011/235843

#### Research Article

### **Semidigital PLL Design for Low-Cost Low-Power Clock Generation**

#### Ni Xu, Woogeun Rhee, and Zhihua Wang

Institute of Microelectronics, Tsinghua University, Beijing 100084, China

Correspondence should be addressed to Woogeun Rhee, wrhee@tsinghua.edu.cn

Received 15 May 2011; Revised 5 September 2011; Accepted 9 September 2011

Academic Editor: Sudhakar Pamarti

Copyright © 2011 Ni Xu et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

This paper describes recent semidigital architectures of the phase-locked loop (PLL) systems for low-cost low-power clock generation. With the absence of the time-to-digital converter (TDC), the semi-digital PLL (SDPLL) enables low-power linear phase detection and does not necessarily require advanced CMOS technology while maintaining a technology scalability feature. Two design examples in  $0.18\,\mu m$  CMOS and  $65\,nm$  CMOS are presented with hardware and simulation results, respectively.

#### 1. Introduction

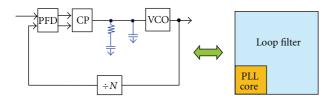

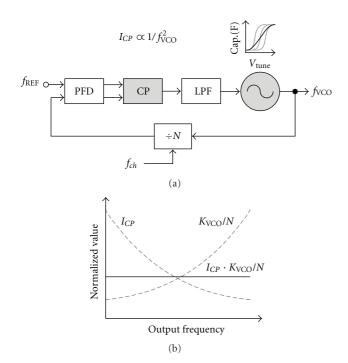

As the system integration complexity increases, robust lowcost frequency generation is highly demanded. Especially, the use of advanced CMOS technologies makes the traditional phase-locked loop (PLL) design challenging as on-chip variability and modeling inaccuracy become severe in deep submicron CMOS. Large loop parameter variation makes it difficult to find the optimum bandwidth for phase noise, spur, and settling time. In addition, analog passive devices become a bottleneck for scalability and integrating the loop filter (LPF) has been a challenging task in the conventional PLL design. Figure 1 depicts an example showing large area contribution of the on-chip loop filter to the PLL. Since the capacitor takes a significant portion of the whole LPF area, the gate leakage current by the on-chip MOS capacitor becomes substantial enough to affect the PLL performance, degrading the static phase error or reference spur performance. As a result, thick-oxide MOSFETs or metal-to-metal capacitors are used for the PLL loop filters at the cost of using an extramask.

#### 2. Design Issues in All-Digital PLL

While integrating a loop filter has been a challenging task in the conventional PLL design, removing the analog loop filter is considered an alternative solution in the recent PLL works [1–13]. However, the all-digital PLL (ADPLL) requires a high-resolution complex time-to-digital converter (TDC) which requires advanced CMOS technology. Use of the bangbang phase detector (BBPD) relaxes the TDC requirement but suffers from a nonlinear PLL bandwidth control [2]. In this paper, we present recent architectures of hybrid PLL systems which reduce technology dependency.

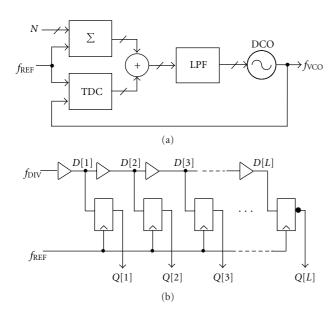

In the ADPLL design, high resolution of the TDC as shown in Figure 2 is important not only to enhance linearity but also to reduce in-band phase noise of the ADPLL. For the given reference clock frequency  $F_{\rm REF}$  and the VCO frequency  $F_{\rm VCO}$ , the in-band phase noise L of the ADPLL due to the TDC time resolution  $\Delta t_{\rm res}$  is given by [1]

$$L = \frac{(2\pi)^2}{12} \left(\frac{\Delta t_{\rm res}}{T_{\rm VCO}}\right)^2 \cdot \frac{1}{F_{\rm RFF}}.\tag{1}$$

The equation implies that finer TDC resolution is required for higher VCO output frequency. In fact, this is analogous to the fact that noise contribution of the phase detector (PD) increases with high division ratio N by the factor of  $20 \log N$  in the conventional analog PLL design. Therefore, the ADPLL design also has difficulty in achieving low inband phase noise performance with high division ratio. Besides, the ADPLL requires advanced CMOS technology for low in-band noise performance based on the above equation, which is different from the analog PLL. In addition to the advanced technology requirement, the TDC is sensitive

FIGURE 1: Loop filter area contribution to PLL in advanced CMOS.

FIGURE 2: ADPLL with linear TDC [1].

to PVT variation. Typical delay time variation of a single inverter exhibits nearly 50% variation over process and temperature. Such a high sensitivity can cause poor linearity and nonuniform phase detector gain, resulting in widespread spur generation.

Table 1 shows architecture comparison between the ADPLL and the conventional analog PLL which typically consists of the phase-frequency detector (PFD) and the charge pump (CP). The conventional analog PLL suffers from poor scalability and leakage current sensitivity mainly due to the analog loop filter and does not offer good control of loop parameters compared to the ADPLL. On the other hand, the ADPLL features high scalability and reconfigurability with digital implementation but suffers from design complexity and nonlinear loop dynamics. Since the digitally controlled oscillator (DCO) has many switches with parasitic capacitance and the TDC requires fine-timing resolution using an advanced CMOS technology is highly demanded for the high performance ADPLL design.

#### 3. Technology Scalable Semidigital PLL

In this paper, we consider a low-cost TDC-less semidigital PLL architectures [14–17] which do not require a large integration capacitor in the LPF, achieving technology scalability and leakage current immunity like the ADPLL.

TABLE 1: ADPLL versus conventional PLL.

|                            | ADPLL                  | Conventional PLL |

|----------------------------|------------------------|------------------|

| Power                      | Fair (depends on tech) | Good             |

| Reconfigurability          | Good                   | Poor             |

| Scalability                | Good                   | Poor             |

| I <sub>Leak</sub> Immunity | Good                   | Poor             |

| Linear BW control          | Fair                   | Good             |

| Design complexity          | High                   | Fair             |

| Tech. dependency           | High                   | Fair             |

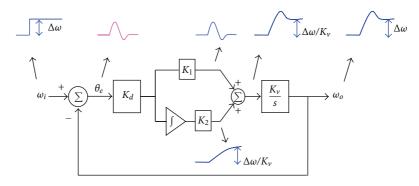

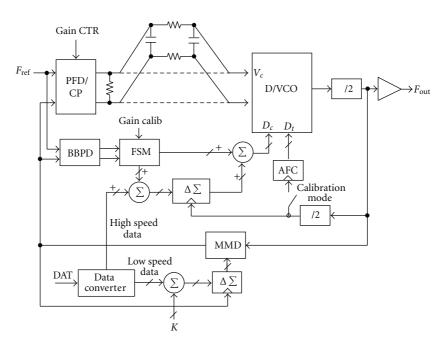

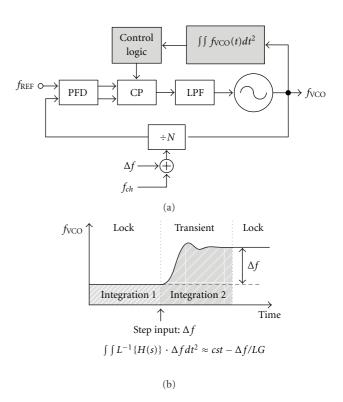

3.1. Basic Concept. The type II PLL inherently provides an integral path which tracks frequency offset independently so that, in theory, the static phase error can be zero even with the frequency offset. Figure 3 shows how the type II PLL obtains frequency acquisition without generating a static phase error. As far as phase tracking is concerned, the integral path is a large-signal path while the proportional-gain path is a small-signal path. When the large-signal path slowly tunes the VCO to the desired frequency, the small-signal path does not have to provide additional DC information for frequency acquisition. Therefore, different implementation for each path is possible in the type II PLL design, namely, the integral path in digital and the proportional-gain path in analog.

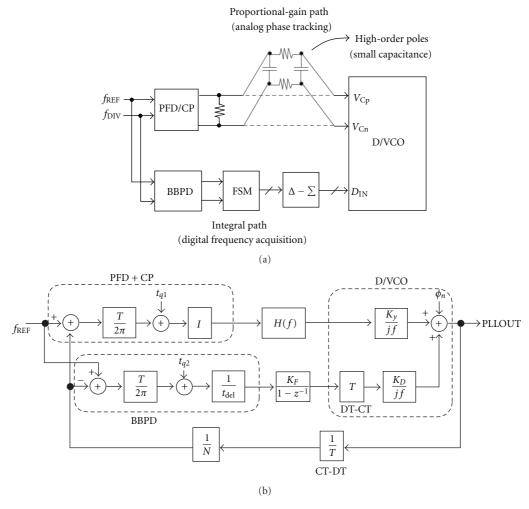

Figure 4 shows the basic concept of the semi-digital loop control [14], and a linear model is shown in Figure 4(b). Since the control path of the type II PLL can be decomposed into a proportional-gain path and an integration path as discussed, independent implementation is considered for each path. For the proportional-gain path, the conventional analog control is used except the absence of the integrating capacitor. Since the capacitance values for high-order poles are not high, either the MOS capacitor with negligible leakage current or the MIM capacitor can be used. As for the integral path, digital implementation is done with the BBPD and the FSM to compensate for the limited frequency tracking capability of the proportional-gain path. The  $\Delta\Sigma$ modulator is used to provide fine frequency resolution as done in the ADPLL. The main purpose of the digital integration path is to provide frequency tracking rather than phase tracking. Accordingly, the time constant of the digital integration path can be much longer than the analog small-signal path, resulting in overdamped loop dynamics. With the overdamped loop dynamics, the PLL bandwidth is linearly controlled by the charge pump current whose value can be digitally programmable in the design. In summary, the proposed hybrid loop control with the analog proportional path and the digital integration path provides linear phase tracking, leakage-insensitive loop filtering, technology scalability, and uniform PD gain capability.

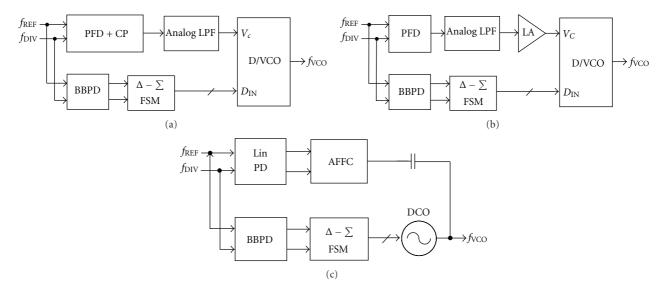

3.2. Architecture Comparison with Other PLLs. For the SDPLL design with an LC VCO, three different topologies can be considered for the analog proportional-gain path as shown in Figure 5. Figure 5(a) is based on the CP PLL topology as already presented previously [14]. Other way

FIGURE 3: State-variable model of type II PLL.

FIGURE 4: (a) Basic concept and (b) linear model.

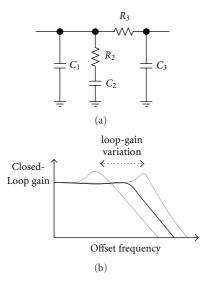

is to have the PFD output directly connected to the VCO input [15]. In this case, a linear amplifier (LA) is needed to set the optimum common mode voltage for maximum varactor tuning range. The additional LA degrades VCO noise performance. However, the LA noise contribution can be suppressed by the PLL bandwidth since the LA is placed after the LPF and gets high-pass noise transfer function by

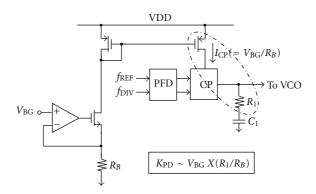

the PLL. Without the CP, Figure 5(b) can achieve better inband phase noise performance. When the PLL bandwidth is narrow and requires good phase noise performance of the VCO, the topology from Figure 5(a) should be chosen. In addition, the phase detector gain can be well regulated over PVT variations if the bias current of the charge pump is generated by an on-chip resistor and a bandgap reference

FIGURE 5: (a) PFD/CP based, (b) PFD/LA based, and (c) AAFC based.

FIGURE 6: CP biasing for uniform PD gain.

voltage [16], which is illustrated in Figure 6. The last one shown in Figure 5(c) uses analog feed-forward circuits (AFFC) to provide a linear phase modulation path [17]. However, having the AC-coupling path at the VCO output requires more complicated design efforts than employing the dual-control path at the VCO input since dealing with high frequency signals is more difficult. Moreover, the analog RC filter in the AFFC connected to both supply and ground can cause a coupling path to the supply noise.

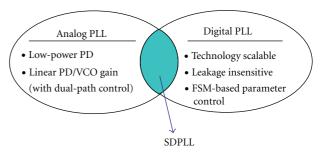

As depicted in Figure 7, the SDPLL offers moderate performance between the conventional analog PLL and the ADPLL. A mixed-mode loop control with an analog proportional path and a digital integration path offers a leakage-insensitive and technology scalable architecture comparable to the digital PLL, while maintaining low-cost linear phase detection like the analog PLL. The PFD/CP-based proportional-gain path provides linear loop dynamics in which tracking bandwidth is simply set by the PD gain, the passive LPF transfer function, and the analog VCO gain. In addition, with the absence of the linear TDC, power consumption can be reduced and using advanced

FIGURE 7: Architecture comparison.

CMOS technology is not a must for achieving good noise performance.

#### 4. Design Examples

In this paper, two SDPLL design examples are presented; one designed in  $0.18\,\mu m$  CMOS for digital clock generation and

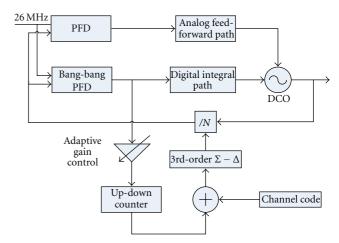

FIGURE 8: SDPLL block diagram.

FIGURE 9: Hybrid D/VCO with embedded FIR filtering.

the other in 65 nm CMOS for wireless applications (Table 2). The former shows that the hybrid loop control is successfully verified in hardware, and the latter shows promising low-power feature of the SDPLL for two-point modulation with a small area comparable to the ADPLL-based modulation.

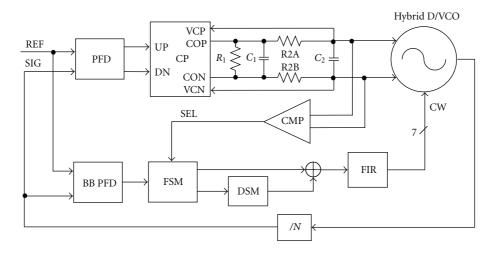

4.1. 0.18 µm CMOS SDPLL for Digital Clock Generation. Figure 8 shows a block diagram of the SDPLL [14]. To minimize noise coupling, a differential charge pump followed by a differential loop filter is designed in the analog control path. For the 3rd- and 4th-order poles, the MIM capacitor is used to have good isolation from the substrate noise coupling. In the digital integration path, the BBPD is used to provide bi-level information to the 18-bit FSM, where the 7-bit output from the MSB is the integral part and the following 8-bit output is the fractional part. The remaining 3-bit output is used for averaging function. The frequency

resolution set by the digital tuning loop is about 2.1 MHz per LSB. Since the digital integration path has slow frequency acquisition, an adaptive bandwidth scheme is designed. For that purpose, a voltage comparator is added to provide transition information to the FSM.

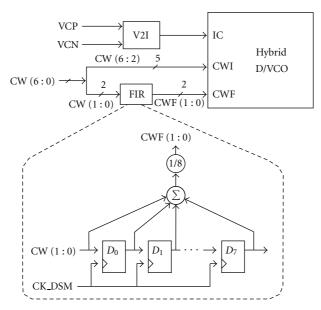

Figure 9 shows the hybrid DCO block diagram with the FIR-based  $\Delta$ - $\Sigma$  control, where a 7-bit control input is used. A 2nd-order MASH modulator is used for its simple structure. The 2nd-order MASH modulator has 2-bit output CW (1:0), so only the last two bits from the LSB are controlled by the modulator. The 5-bit static input, CW (6:2) directly controls the digital input of the hybrid DCO. Since the hybrid DCO has a 5-bit static input and a 2-bit dynamic modulated by the 10-bit modulator, the total frequency resolution of 15 bit is obtained in the digital control path.

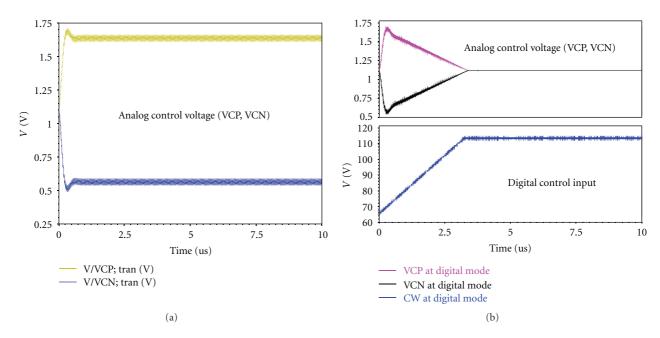

Figure 10 shows the behavioral simulation results of the PLL settling behavior, (a) without digital path and (b) with

FIGURE 10: Simulated transient settling voltage: (a) with digital path disabled, and (b) with digital path enabled.

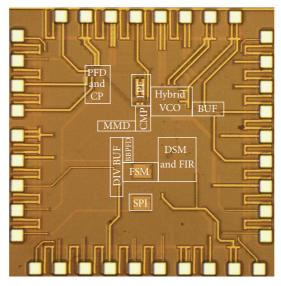

FIGURE 11: Chip micrograph [14].

digital path. When the digital path is not enabled, frequency acquisition is done only by the proportional-gain path, resulting in an analog type I PLL. As a result, large static phase error is observed when the PLL needs to track the frequency offset. With the digital path enabled, the frequency is tracked by the digital integration path. Consequently, the control voltage is settled within a very small range even with the frequency offset as shown in Figure 10(b), showing that the type II PLL is realized.

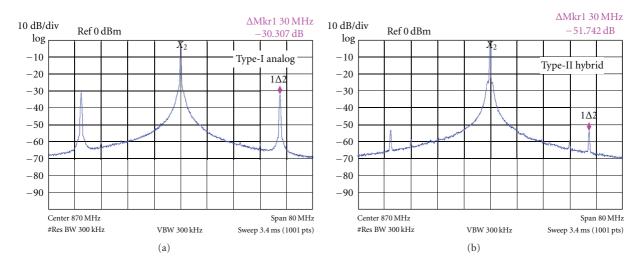

Figure 11 shows the micrograph of the test chip fabricated in 0.18  $\mu$ m CMOS. The active core area is 0.6 mm<sup>2</sup> where only 0.01 mm<sup>2</sup> is occupied by the analog loop filter. Figure 12 shows the measured output spectra at 870 MHz frequency

with the reference clock frequency of 30 MHz. The upper plot shows the output spectrum with the digital path disabled. Since the PLL becomes a type I PLL without the digital integration path, a large static phase offset is generated, resulting in the spur level as high as  $-30~\rm dBc$ . When the digital integration path is enabled, the reference spur is reduced by more than 20 dB. Also, the DC control voltage range is settled within  $\pm 0.02~\rm V$  when the digital path is enabled. The experimental results prove that the type-II PLL is realized with the hybrid loop control.

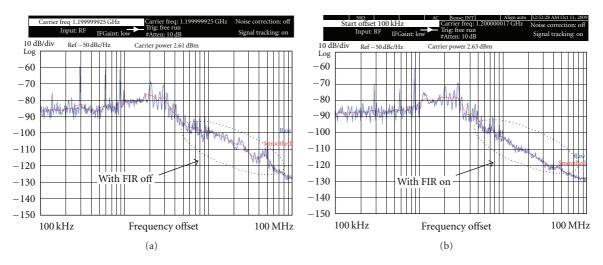

Since the phase noise contribution from the analog control path is worse than expected, it is difficult to see the effect of the hybrid FIR filter. Figure 13 shows the phase

FIGURE 12: Measured output spectra: (a) with digital path disabled and (b) with digital path enabled.

FIGURE 13: Measured output spectra: (a) with FIR disabled and (b) with FIR enabled.

Table 2: Measured performance summary [14].

| Process              | 0.18 μm CMOS                                                                  |  |

|----------------------|-------------------------------------------------------------------------------|--|

| Supply Voltage       | 1.8 V for analog, 1.5 V for digital                                           |  |

| Power consumption    | Total: 16.8 mW<br>(Analog: 11.9 mW, Digital: 4.9 mW)                          |  |

| Occupied area        | Active area: $\sim 0.6 \text{ mm}^2 \text{ (LPF} < 0.04 \text{ mm}^2\text{)}$ |  |

| VCO tuning range     | 790–925 MHz                                                                   |  |

| Reference clock      | 30 MHz                                                                        |  |

| Reference spur       | $< -52 \mathrm{dBc}$                                                          |  |

| Phase noise          | $< -81  \mathrm{dBc/Hz}$                                                      |  |

| Integrated RMS noise | 100 kHz~100 MHz: 12.6° <sub>rms</sub><br>10 MHz~100 MHz; 1.1° <sub>rms</sub>  |  |

noise performance of the SDPLL output from the other test site, in which the hybrid FIR filter embedded in the D/VCO

clearly reduces the high-frequency noise caused by the  $\Delta\text{-}\Sigma$  modulation.

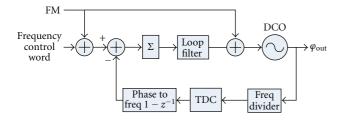

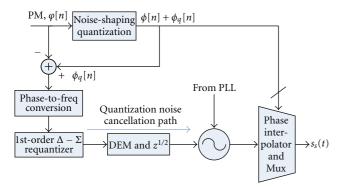

4.2. 65 nm CMOS SDPLL for Two-Point Modulation. The SDPLL architecture can be further extended to accommodate two-point phase modulation for RF transmitter systems, which has been well demonstrated by the ADPLL in the literature [1]. Figure 14 shows a simplified block diagram of the fractional-N SDPLL having the two-point modulation feature for GSM/GPRS applications. Similar to the ADPLL, the DCO gain can be calibrated easily by measuring the frequency step for the 1-LSB change since phase modulation is done in the digital domain with the DCO input control. Also, the group delay mismatch can be controlled to a certain degree by embedding the high-frequency DFFs in the FSM. Since the noise transfer functions of the DCO and the fractional-N divider are still controlled by the PLL loop dynamics, the use of the PFD and the CP offers linear control. Without using the TDC, overall power consumption

FIGURE 14: SDPLL with two-point modulation for RF transmitter systems.

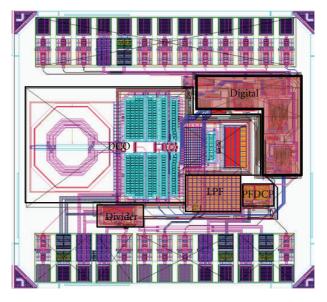

FIGURE 15: SDPLL layout in 65 nm CMOS (active area: 0.52 mm<sup>2</sup>).

of the SDPLL can be further reduced while the total area is comparable to the ADPLL.

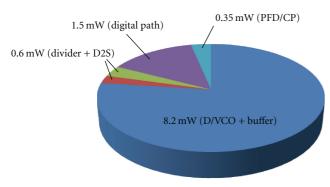

Figure 15 shows a layout of the SDPLL in 65 nm CMOS, occupying the active area of only 0.52 mm². The active area is much smaller than that of the conventional analog PLL and comparable to that of the ADPLL. Except the  $\Delta\Sigma$  modulator and high-frequency control blocks, most digital operations for the two-point modulation are realized by external control with FPGA. Figure 16 shows power consumption analysis of the SDPLL based on postlayout simulation results. The

D/VCO consumes nearly 80% of the total power. The power contribution of the PFD and the CP is less than 5% of the total power, showing that the SDPLL can save more power than the ADPLL by not employing the power-hungry TDC.

#### 5. Conclusion

In this paper, some design issues in recent clock generation systems are reviewed and the SDPLL is presented as a lowpower technology-friendly architecture. We also show that

FIGURE 16: Power consumption analysis.

the SDPLL architecture can be further tailored for various applications without necessarily requiring advanced CMOS technology.

#### References

- [1] R. B. Staszewski, J. L. Wallberg, S. Rezeq et al., "All-digital PLL and transmitter for mobile phones," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 12, pp. 2469–2480, 2005.

- [2] J. A. Tierno, A. V. Rylyakov, G. J. English, D. Friedman, and M. Meghelli, "A wide power supply range, wide tuning range, all static CMOS all digital PLL in 65 nm SOI," *IEEE Journal of Solid-State Circuits*, vol. 43, pp. 42–51, 2008.

- [3] C. M. Hsu, M. Z. Straayer, and M. H. Perrott, "A low-noise wide-BW 3.6-GHz digital ΔΣ fractional-N frequency synthesizer with a noise-shaping time-to-digital converter and quantization noise cancellation," *IEEE Journal of Solid-State Circuits*, vol. 43, no. 12, Article ID 4684627, pp. 2776–2786, 2008.

- [4] M. Lee, M. E. Heidari, and A. A. Abidi, "A low-noise wideband digital phase-locked loop based on a coarse-fine time-to-digital converter with subpicosecond resolution," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 10, article 23, pp. 2808–2816, 2009.

- [5] M. Zanuso, S. Levantino, C. Samori, and A. Lacaita, "A 3 MHz-BW 3.6 GHz digital fractional-N PLL with sub-gatedelay TDC, phase-interpolation divider, and digital mismatch cancellation," pp. 476–477.

- [6] E. Temporiti, C. Weltin-Wu, D. Baldi, M. Cusmai, and F. Svelto, "A 3.5 GHz wideband ADPLL with fractional spur suppression through TDC dithering and feedforward compensation," *IEEE Journal of Solid-State Circuits*, vol. 45, no. 12, Article ID 5604330, pp. 2723–2736, 2010.

- [7] S.-K. Lee, Y.-H. Seo, H.-J. Park, and J.-Y. Sim, "A 1 GHz ADPLL with a 1.25 ps minimum-resolution sub-exponent TDC in 0.18 μm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 45, no. 12, Article ID 5609226, pp. 2874–2881, 2010.

- [8] H.-H. Chang, P.-Y. Wang, J. H. C. Zhan, and B. Y. Hsieh, "A fractional spur-free ADPLL with loop-gain calibration and phase-noise cancellation for GSM/GPRS/EDGE," in *Proceed*ings of the IEEE International Solid State Circuits Conference, (ISSCC, '08), pp. 200–201, February 2008.

- [9] W. Grollitsch, R. Nonis, and N. Da Dalt, "A 1.4 psrmsperiod-jitter TDC-less fractional-N digital PLL with digitally controlled ring oscillator in 65nm CMOS," in *Proceedings of* the IEEE International Solid-State Circuits Conference, (ISSCC '10), pp. 478–479, February 2010.

- [10] P.-H. Hsieh, J. Maxey, and C. K. K. Yang, "A phase-selecting digital phase-locked loop with bandwidth tracking in 65-nm CMOS technology," *IEEE Journal of Solid-State Circuits*, vol. 45, no. 4, Article ID 5437483, pp. 781–792, 2010.

- [11] D.-S. Kim, H. Song, T. Kim, S. Kim, and D. K. Jeong, "A 0.3–1.4 GHz all-digital fractional-N PLL with adaptive loop gain controller," *IEEE Journal of Solid-State Circuits*, vol. 45, no. 11, Article ID 5607237, pp. 2300–2311, 2010.

- [12] T. Tokairin, M. Okada, M. Kitsunezuka, T. Maeda, and M. Fukaishi, "A 2.1-to-2.8-GHz low-phase-noise all-digital frequency synthesizer with a time-windowed time-to-digital converter," *IEEE Journal of Solid-State Circuits*, vol. 45, no. 12, Article ID 5604672, pp. 2582–2590, 2010.

- [13] M. Chen, D. Su, and S. Mehta, "A calibration-free 800 MHz fractional-N digital PLL with embedded TDC," *IEEE Journal of Solid-State Circuits*, vol. 45, no. 12, Article ID 5610982, pp. 2819–2827, 2010.

- [14] R. He, C. Liu, X. Yu et al., "A low-cost, leakage-insensitive semi-digital PLL with linear phase detection and FIR-embedded digital frequency acquisition," in *Proceedings of the IEEE Asian Solid-State Circuits Conference*, (A-SSCC '10), pp. 197– 200, 2010.

- [15] W. Yin, R. Inti, and P. K. Hanumolu, "A 1.6 mW 1.6ps-rms-Jitter 2.5 GHz digital PLL with 0.7-to-3.5 GHz frequency range in 90 nm CMOS," in *Proceedings of the 32nd Annual Custom Integrated Circuits Conference*, (CICC '10), September 2010.

- [16] W. Rhee, H. Ainspan, D. J. Friedman, T. Rasmus, S. Garvin, and C. Cranford, "A uniform bandwidth PLL using a continuously tunable single-input dual-path LC VCO for 5 Gb/s PCI express Gen2 application," in *Proceedings of the IEEE Asian Solid-State Circuits Conference*, (A-SSCC '07), pp. 63–66, November 2007.

- [17] P.-Y. Wang, J. H. C. Zhan, H. H. Chang, and H. M. S. Chang, "A digital intensive fractional-N PLL and all-digital self-calibration schemes," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 8, Article ID 5173739, pp. 2182–2192, 2009.

Hindawi Publishing Corporation Journal of Electrical and Computer Engineering Volume 2011, Article ID 871385, 11 pages doi:10.1155/2011/871385

#### Research Article

#### An Interpolated Flying-Adder-Based Frequency Synthesizer

#### Pao-Lung Chen and Chun-Chien Tsai

Department of Computer and Communication Engineering, National Kaoshiung First University of Science and Technology, No. 2, Jhuoyue Road, Nanzih District, Kaohsiung City 811, Taiwan

Correspondence should be addressed to Pao-Lung Chen, plchen@nkfust.edu.tw

Received 8 June 2011; Revised 25 August 2011; Accepted 25 August 2011

Academic Editor: Jae-Yoon Sim

Copyright © 2011 P.-L. Chen and C.-C. Tsai. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

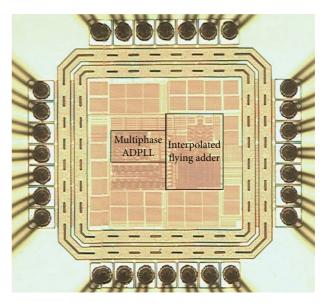

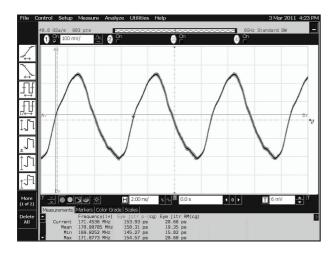

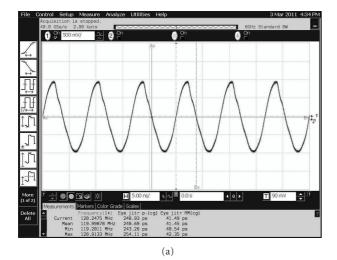

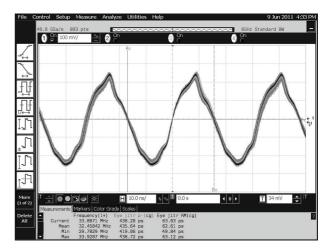

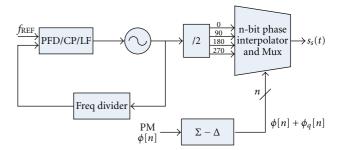

This work presents an interpolated flying-adder- (FA-) based frequency synthesizer. The architecture of an interpolated FA, which uses an interpolated multiplexer (MUX) to replace the multiplexer in conventional flying adder, improves the cycle-to-cycle jitter and root-mean-square (RMS) jitter performance. A multiphase all-digital phase-locked loop (ADPLL) provides steady reference signals for the interpolated flying adder. This paper reveals implementation skills of a multiphase ADPLL, as well as an interpolated flying adder. In addition, analytical details of the jitter performance are derived. A test chip for the proposed interpolated FA-based frequency synthesizer was fabricated in a standard 0.18  $\mu$ m CMOS technology, and the core area was 0.143 mm<sup>2</sup>. The output frequency had a range of 33 MHz  $\sim$  286 MHz at 1.8 V with peak-to-peak ( $P_k$ - $P_k$ ) jitter 215.2 ps at 286 MHz/1.8 V.

#### 1. Introduction

The frequency synthesizer is a key component for numerous systems to generate a desired frequency for frequency conversion in digital communication or in system on chip (SoC) for signal synchronization [1]. Conventional approaches in [2-4] have utilized phase-locked loop (PLL) to generate different high-frequency outputs with a low-frequency crystal clock by setting the frequency control word that is widely used in the industry. While PLL provides flexible frequency synthesis, the loop parameters, such as damping factor and loop bandwidth, must be adjusted to minimize jitter and to ensure that each output frequency and frequency control word is stable. The loop bandwidth should be approximately 1/20 of the reference frequency. To reduce cost and enhance loop stability, an all-digital PLL (ADPLL) in [5] utilized a digital loop filter with a seven-cycle lock time. However, the output frequency range is less than 100 MHz. With a fractional-N synthesis technique [6], finer frequency control can be achieved. But the system typically has a narrow bandwidth that has tight control on loop parameters.

Direct digital synthesis (DDS) in [7] uses memory and logic to generate the desired output frequency. It normally consists of a phase accumulator, an ROM lookup table and

a linear digital-to-analog converter (DAC). The performance of a DAC is the bottleneck of this technique. In recent years, flying-adder frequency synthesis has provided a new way of generating frequency on chip [8–16]. The flying-adder-based frequency synthesizer solves problem that cannot be dealt easily with conventional PLL-based or DDS-based frequency synthesizer. The flying-adder frequency synthesizer is also called a direct digital period synthesizer (DDPS) in [17]. The flying-adder-based frequency synthesizer has been applied in many commercial chips such as the triple DAC graphics digitizer, digital speaker, LCD monitors, HDTV chips, and NTSC video decoders [11–13].

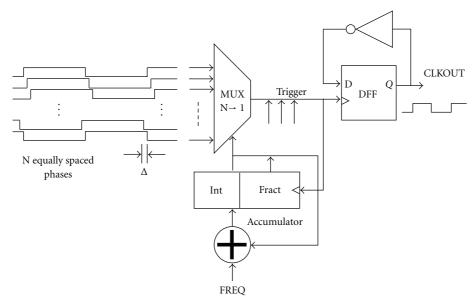

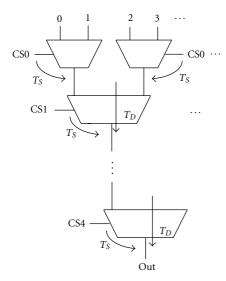

The basic structure of a flying adder is shown in Figure 1. The structure consists of an N equally spaced phases, a multiplexer (MUX), a D flip-flop (DFF), and an *n*-bit accumulator. The *n*-bit accumulator is composed of an *n*-bit adder and an *n*-bit register. The *n*-bit register is divided into the integer (Int) and fractional (Fract) parts. The frequency control word (FREQ) is inputted to the flying adder. The Fract is used for accumulating the fractional part. The multiplexer selects one of the input signals from the N equally spaced phases according to Int value. The output signal from the multiplexer triggers a D flip-flop. The function of D flip-flop is similar to a frequency divider

Figure 1: Block diagram of conventional flying adder [8].

FIGURE 2: Numerical operation of [8]'s flying adder.

by-2 circuit. Meanwhile, the n-bit register for the MUX address is updated. Let us assume that FREQ is a 10-bit frequency control word with 5 bits for Int and 5 bits for Fract, respectively. The timing resolution of a 32 equally spaced phases with " $\Delta$ " is 0.2 ns. If a 769 MHz (1.3 ns) signal is the desired output, then the FREQ[9:0] can be calculated as follows:

$$FREQ[9:0] \cdot 2 \cdot 0.2 \text{ ns} = 1.3 \text{ ns}. \tag{1}$$

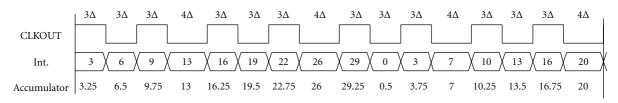

The FREQ[9:0] is equal to  $3.25 = 00011.01000_b$ . As illustrated in this numerical example, the clock cycle at that particular time is 0.2 ns (i.e.,  $\Delta$ ) longer than a normal cycle whenever the value of fractional part is propagated to the integer part. This is called the cycle prolong in a flying-adder frequency synthesizer.

To explain clearly the cycle prolong of the flying-adderbased frequency synthesizer of [8], we assume that the FREQ = Int + Fract = 3.25 as in (1). The Int part is equal to 3, and the fractional part is 0.25.

The numerical operation of Figure 1's flying adder is illustrated in Figure 2. Let us assume that the phase resolution of N equally spaced signals is  $\Delta$ . Whenever there is a rising edge from the MUX output, the value in the accumulator is accumulated with FREQ. The values of the accumulator are 3.25, 6.5, 9.75, and 13. The values of Fract part are 0.25, 0.5, 0.75, and 0. The generated trigger intervals

are  $3\Delta$ ,  $3\Delta$ ,  $3\Delta$ , and  $4\Delta$ . The trigger interval between  $3\Delta$  and  $4\Delta$  is  $1\Delta$  because the accumulation of Fract part is propagated into the Int part. Therefore, the cycle-to-cycle jitter is  $1\Delta$  when the cycle is prolonged, as indicated in [8, 11, 14, 15]. The poor cycle-to-cycle jitter degrades the output clock's performance. Reference [11] solved the prolonged cycle using a post divider. However, the generated frequency is divided down. We propose an interpolated flying-adder structure to reduce jitter which is caused by the cycle prolong.

The rest of this paper is arranged as follows: Section 2 describes the proposed interpolated flying adder. The implementation of a frequency synthesizer using an interpolated flying adder is described in Section 3. In Section 4, the jitter analysis of proposed interpolated flying adder is provided. The experimental result is in Section 5. Finally, Section 6 presents a summary and conclusions.

### 2. Proposed Interpolated Flying Adder

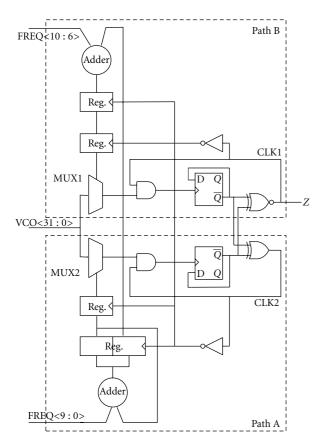

We propose an interpolated flying-adder structure, which can reduce the cycle-to-cycle jitter to one-half, to solve the cycle prolong. The interpolated flying-adder structure is an improvement of [9] two path's flying-adder structure. The two-path flying adder is interlocked through two AND gates and XOR/XNOR gates between path A and path B as shown in Figure 3.

FIGURE 3: Two-path flying-adder frequency synthesizer [9].

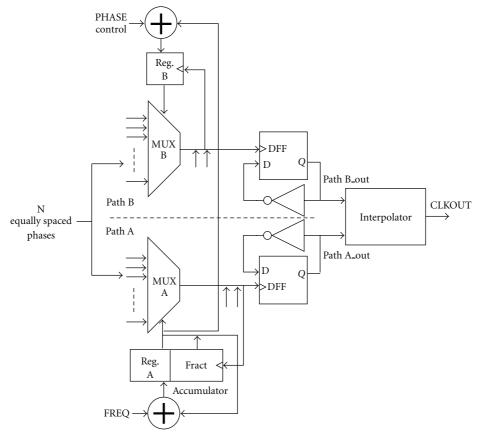

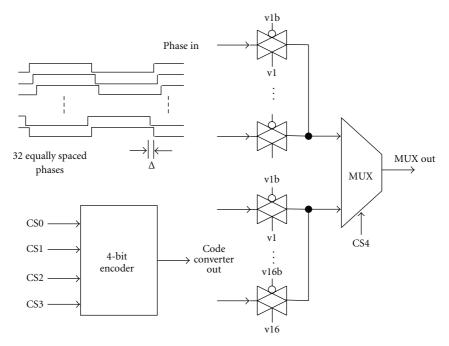

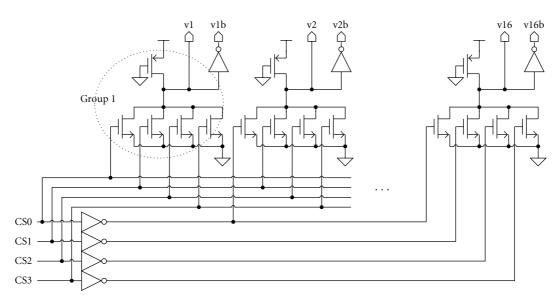

The two AND gates and the feedback self-clocking of the registers ensure that at any given time, there is only one path switched on and one path switched off. The two-path flying-adder makes the 32 VCO ticks look like 64 ticks [19]. utilized an all-digital PLL with delay chain for generation of the 32 VCO ticks for two-path flying-adder frequency synthesizer. A cell-based implementation of two-path flying adder with dual resolution is indicated in [20]. However, the problem of cycle prolong is still unsolved in both one-path and two-path flying adders. Figure 4 is the block diagram of proposed interpolated flying adder. We modify the original two-path flying-adder structure. A digital interpolator is applied to interpolate the output from path A and path B. Both paths are simultaneously switched on in interpolated flying adder which is different from the two-path operation.

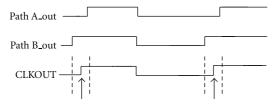

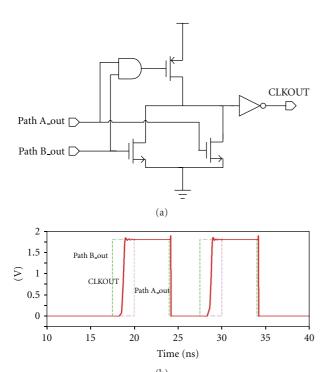

Path A is similar to path B. However, the difference is the bit width of accumulator. The input signal of Reg. A is the integer (Int) part of accumulator. The value of Reg. B is accumulated with the value in Reg. A and input phase control. The phase control is used to control the phase relationship between path A and path B. The output signals of path A and path B are interpolated by an interpolator. The interpolator receives two signals, path A\_out and path B\_out, to produce third output signal, CLKOUT. The rising edge of the out signal is in the midpoint of path A\_out and path B\_out as illustrated in Figure 5.

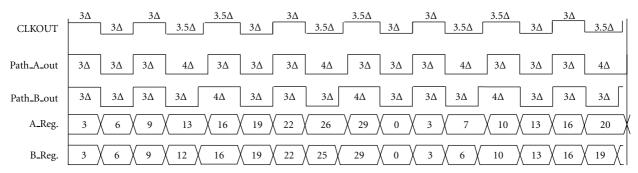

When FREQ = 3.25 is the same as in Figure 2 for the flying adder of [8], the PHASE = 3 is equal to the integer

part of FREQ. Figure 6 shows the numerical operation of the proposed interpolated flying adder. The Int part value of the accumulator is stored in Reg. A. The Reg. A's value will be accumulated with phase into Reg. B triggered by the output MUX B. The output of path A and path B will be interpolated at the output of interpolator. Then the interpolated intervals are  $3\Delta$ ,  $3\Delta$ ,  $3.5\Delta$ , and  $3.5\Delta$ , as calculated in Figure 6. The trigger interval between  $3\Delta$  and  $3.5\Delta$  is  $0.5\Delta$ . Therefore, the cycle-to-cycle jitter of the proposed interpolated flying adder is improved 50% as compared with the flying adder in Figure 2.

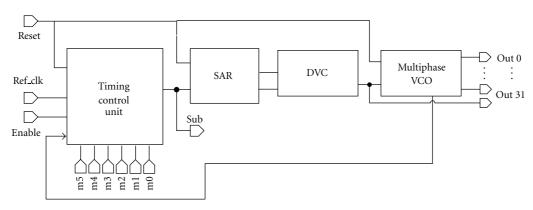

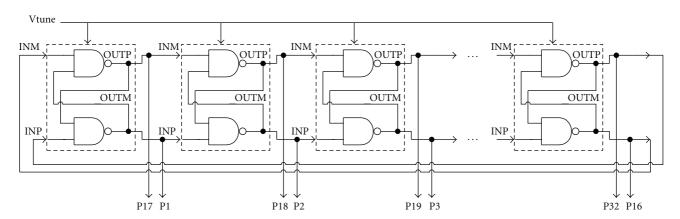

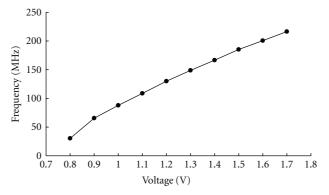

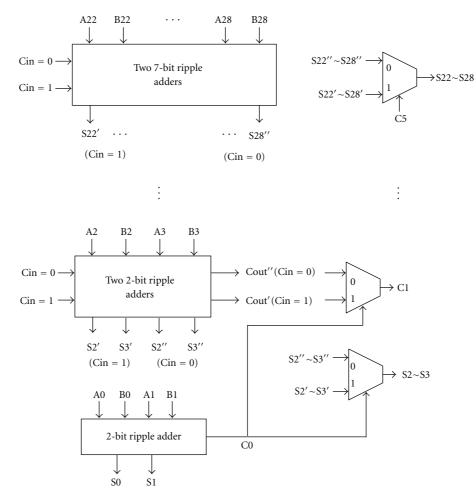

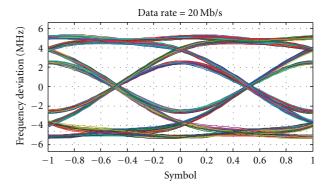

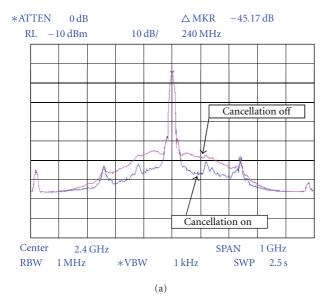

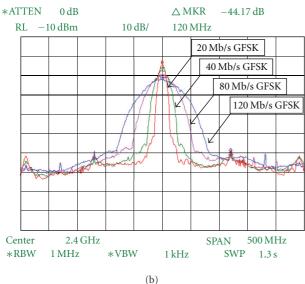

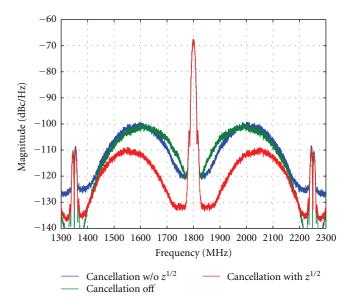

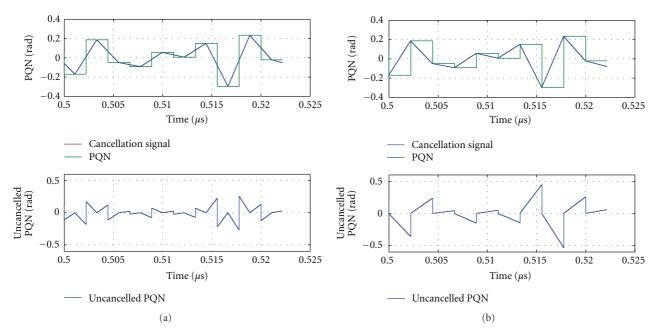

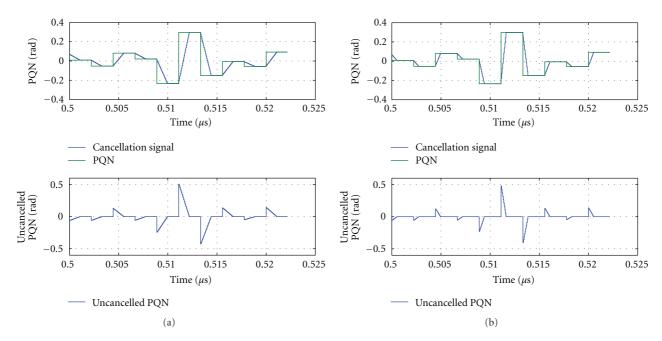

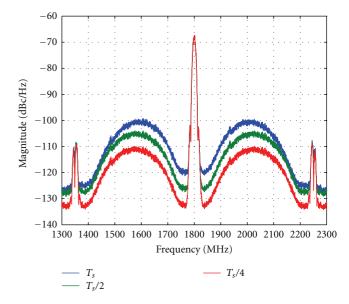

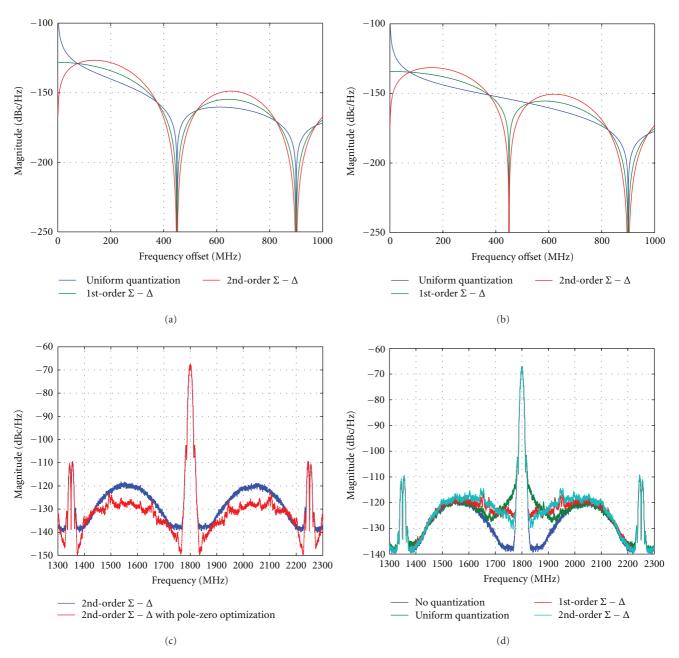

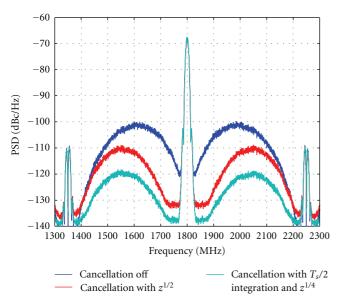

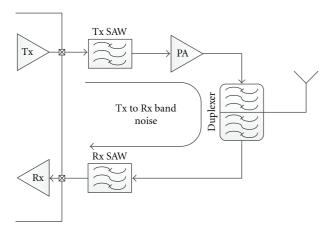

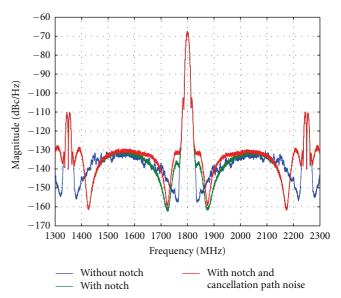

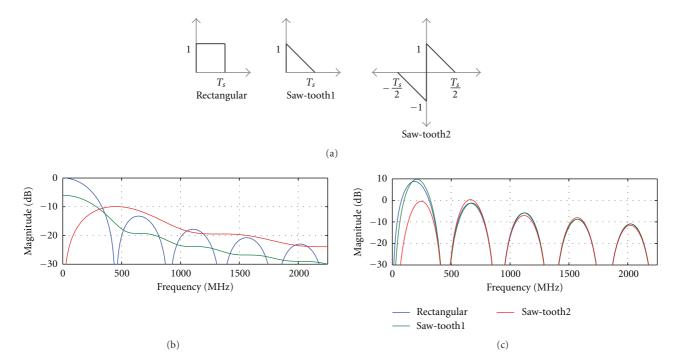

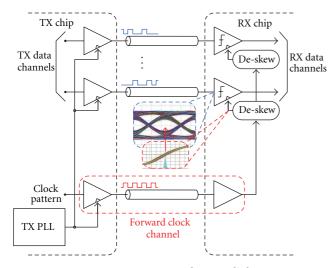

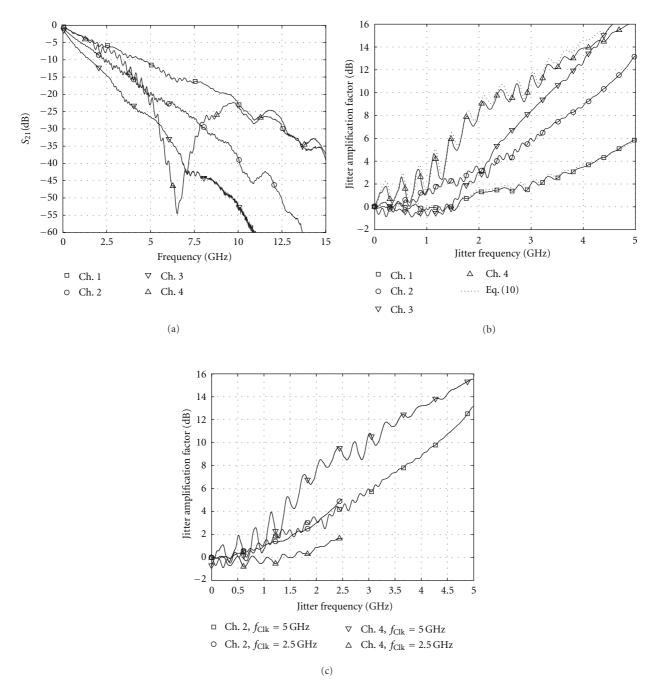

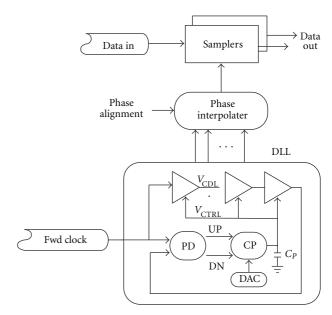

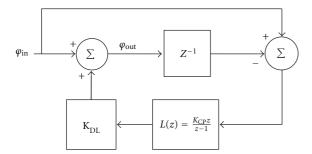

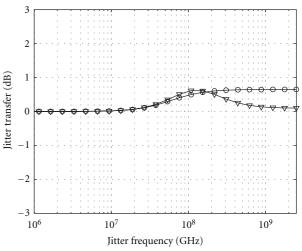

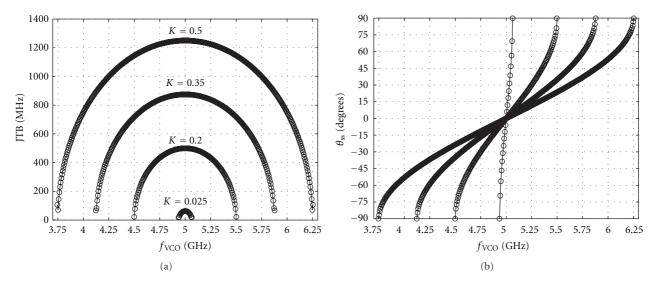

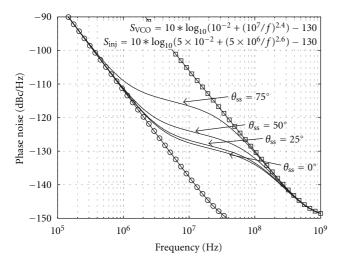

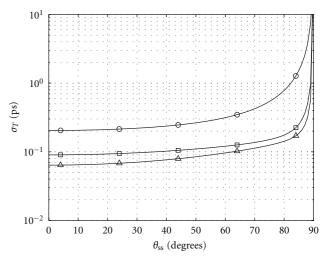

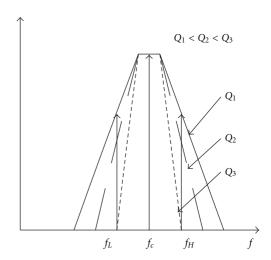

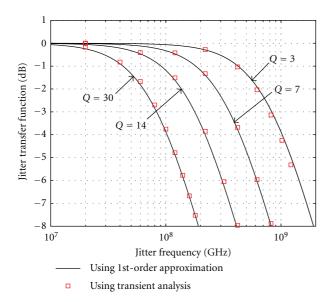

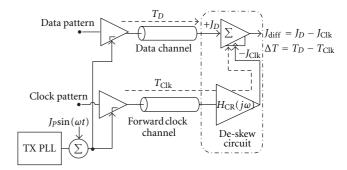

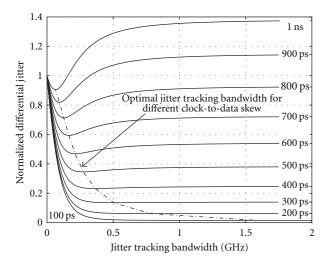

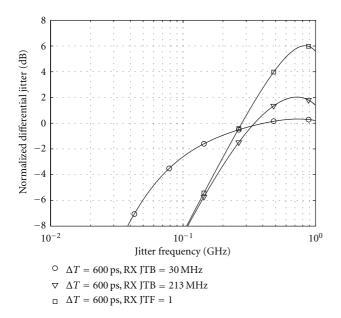

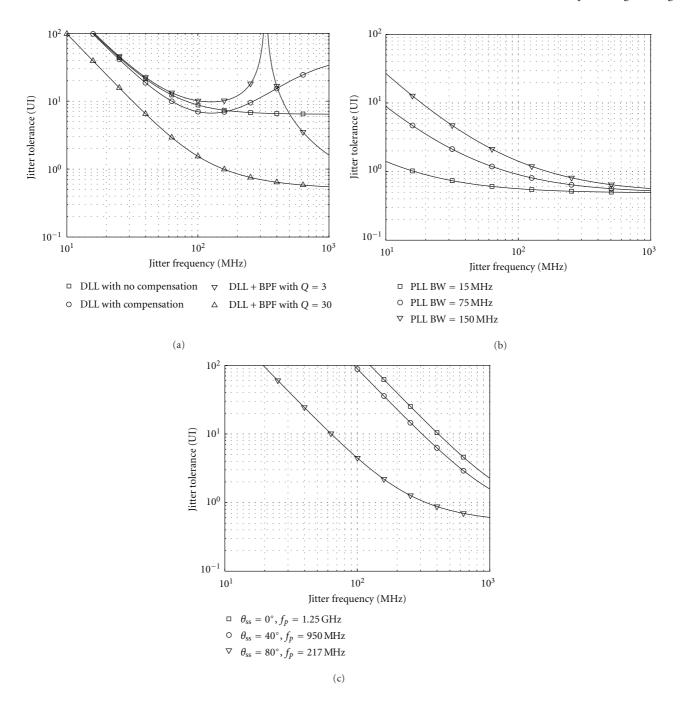

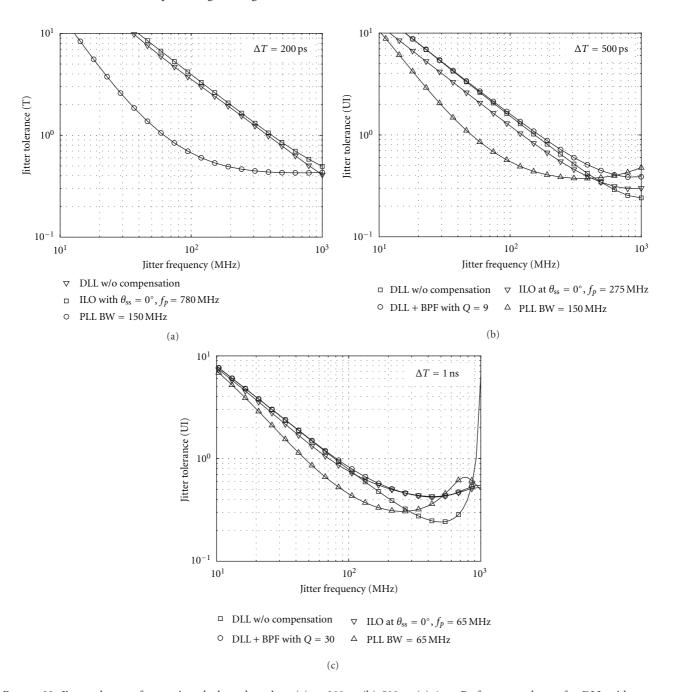

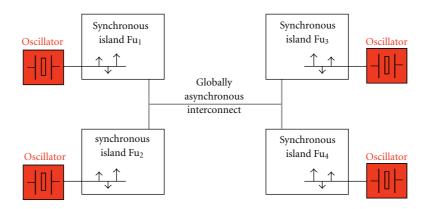

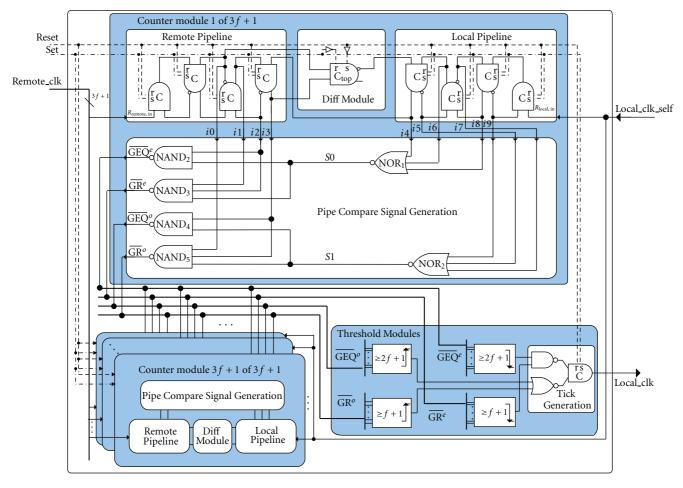

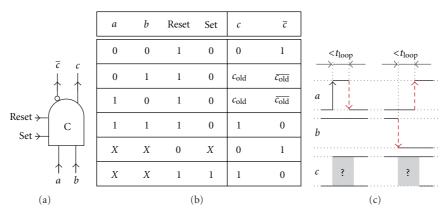

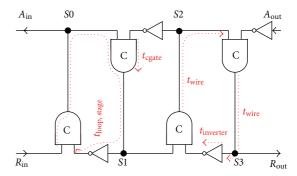

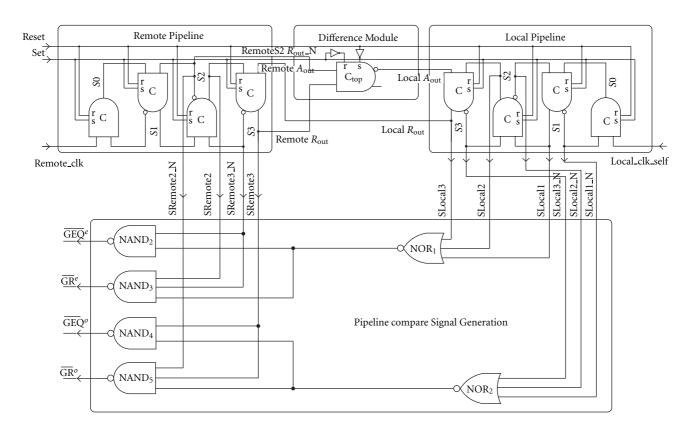

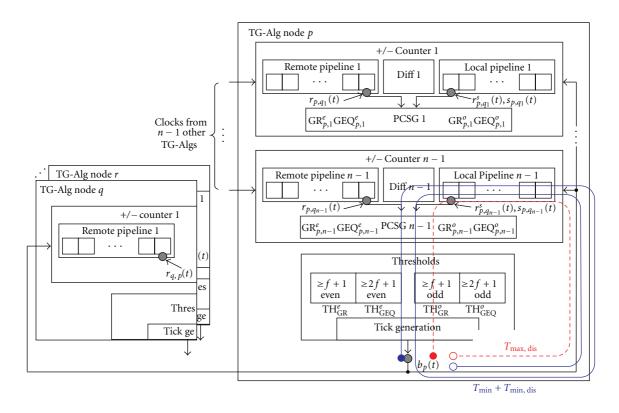

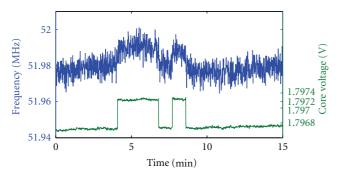

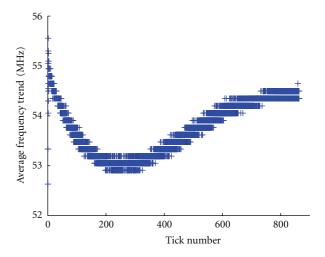

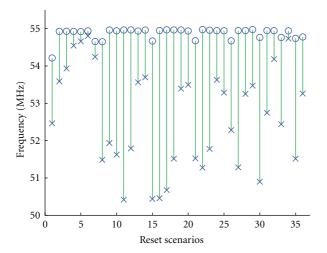

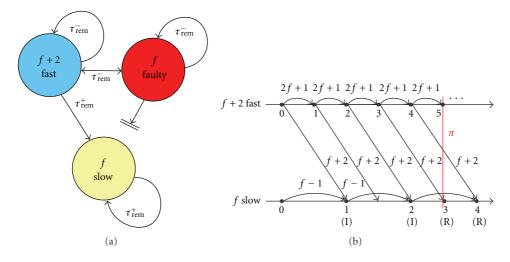

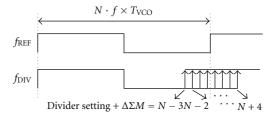

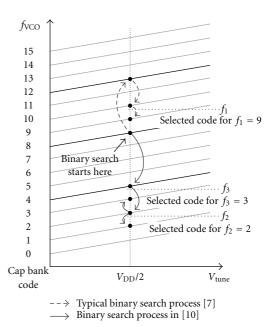

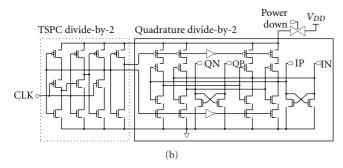

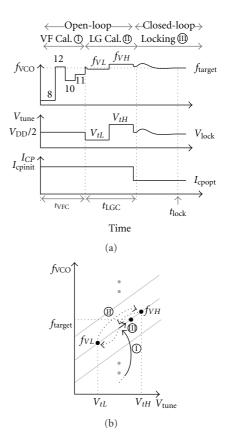

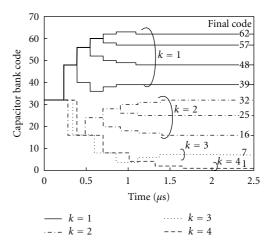

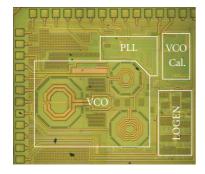

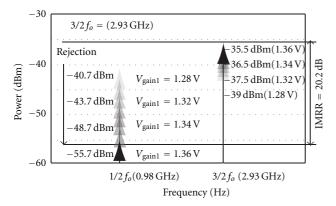

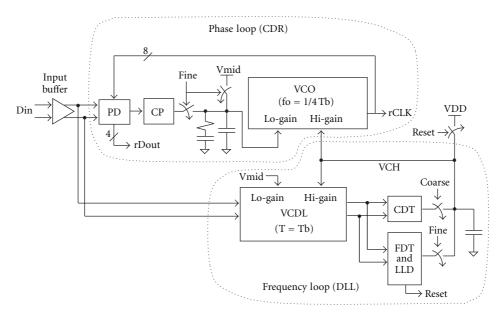

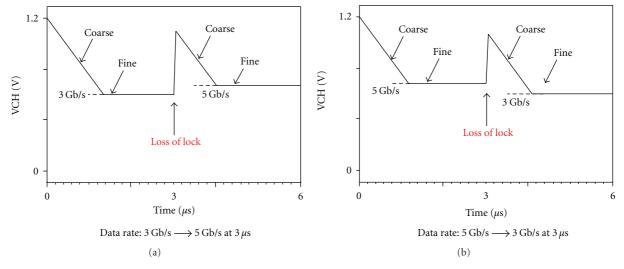

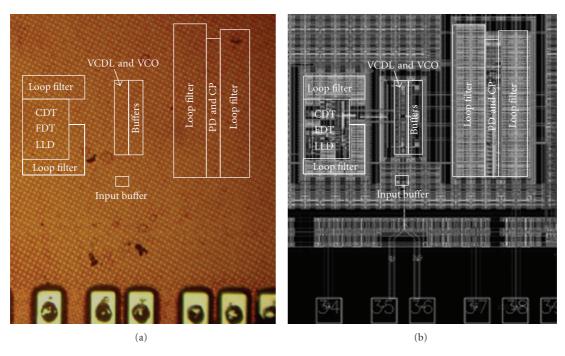

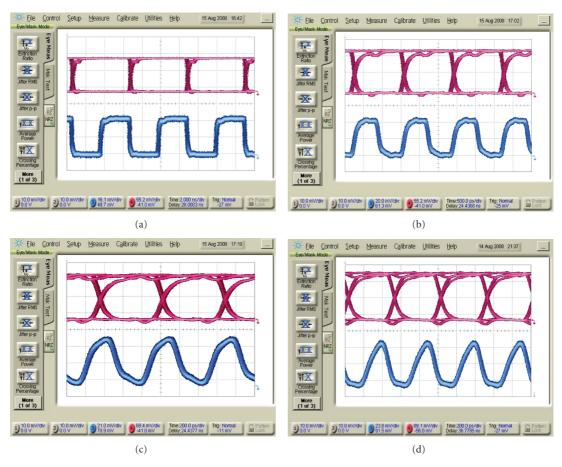

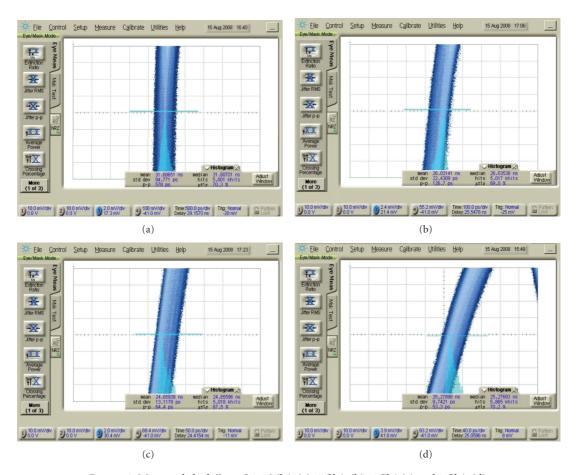

# 3. Implementation of Interpolated Flying-Adder-Based Frequency Synthesizer